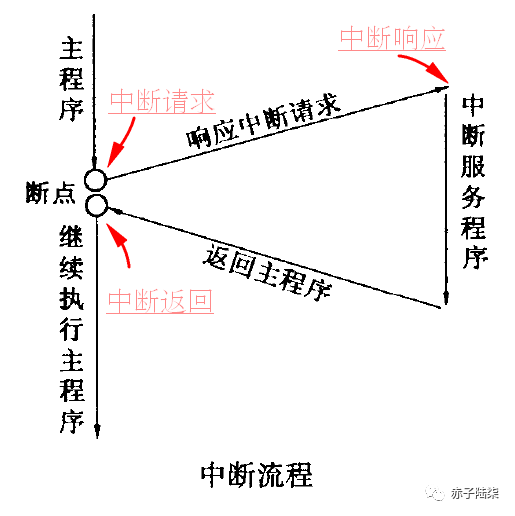

ARM单片机是大多数新手选择的入门切入点,但由于知识的不足,在设计过程中新手们经常会遇到这样或那样的问题,ARM异常中断返回就是这样一种令人头疼的问题。在ARM的使用问题中异常中断返回是新手们较为苦恼的问题,本文就将对ARM异常中断的集中情况进行总结,并给出了一些解决方法。

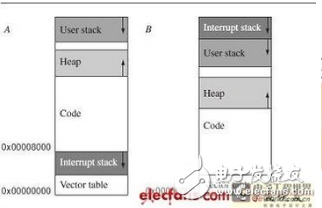

在正式介绍之前,要为大家补充一些较为重要的基础知识。首先R15(PC)总是指向“正在取指”的指令,而不是指向“正在执行”的指令或正在“译码” 的指令。一般来说,人们习惯性约定将“正在执行的指令作为参考点”,称之为当前第一条指令,因此PC总是指向第三条指令。当ARM状态时,每条指令为4字节长,所以PC始终指向该指令地址加8字节的地址,即:PC值=当前程序执行位置+8;而ADS中的pc,是为了调试看着方便而修改过的,它指向的是正在执行的指令,即“真正pc-8”!

SWI和未定义指令异常中断的返回

指令地址:

A PC-8当前指令为SWI或未定义指令,此时发生中断.PC的值还没有更新。

A+4 PC-4中断时处理器将PC-4保存到LR。;r!

A+8 PC

返回时,从发生中断的指令A(PC-8)的下一条指令A+4(PC-4)处开始执行,所以直接把LR的值赋给PC就行了,具体指令为MOV PC,LR(PC=A+4=LR)。

白话解释:对于SWI和未定义指令发生异常时pc没有更新,根据ARM的三级流水线原理,pc没有更新,仍然等于(A+8);lr = pc – 4(这时处理器决定的,无法更改!)即A+4。

由于这类异常返回后应执行下一条指令(A+4),所以返回时,pc=lr即可。

IRQ 和FIQ异常中断处理的返回指令地址对应于PC A,PC-8执行此指令完成后(!)查询IRQ及FIQ,如果有中断请求则产生中断。

A+4 PC-4

A+8 PC ;lr!

(此时PC的值已经更新,指向A+12.将当前PC-4,即A+8)。

保存到LR.返回时,要接着执行A+4(LR-4)处的指令,所以返回指令为:

SUBS PC,LR,#4(PC=A+4=LR-4)

白话解释:对于普中断和快中断异常,中断必须在一条指令执行完以后被检测到,如正在执行指令甲时发生了中断,不等指令甲执行完是不会处理该中断的,发生异常时pc已经更新(A+12); lr=pc– 4(这时处理器决定的,无法更改!)即A+8返回后,应执行被中断而没有执行的指令(上面的A+4),所以返回时,pc= lr-4。

指令预取中止异常中断处理的返回

指令地址:

A PC-8 执行本指令时发生中断,A+4 PC-4处理器将A+4(PC-4)保存到:

LR. ;lr!A+8 PC

返回时,发生指令预取中止的指令A(PC-8)处重新执行,所以返回指令为SUBS PC,LR,#4(PC=A=LR-4)。

白话解释:对于预取指令中止异常发生预取指令异常时,是在执行时发生的异常,pc未更新,即pc=A+8;lr=pc – 4(这时处理器决定的,无法更改!)即A+4。

由于这类异常返回后应重新执行异常的那个指令(A),所以返回时,pc = lr-4。

数据访问中止异常中断处理的返回

指令地址:

A PC-8 本指令访问有问题的数据,产生中断时,PC的值已经更新。

A+4 PC-4 中断发生时PC=A+12,处理器将A+8(PC-4)保存到LR.。

A+8 PC ;lr!

返回时,要返回到A处继续执行,所以指令为SUBS PC,LR,#8.(PC=A=LR-8)

白话解释:对于数据访问中止异常时,是在执行时访问数据错误。

导致的异常,pc已经更新,即pc=A+12。

lr=pc–4(这时处理器决定的,无法更改!)即A+8。

由于这类异常返回后应重新执行异常的那个指令(A),所以返回时,pc=lr-8。

总结

引起PC更新的原因一种是数据中止,还有就是中断了。

中断必须是在一条指令执行完毕后才能被检测到,所以它中断的只是还未执行的那条。指令(pc-8),所以pc=lr – 4;

与中断相同,SWI和未定义指令异常也是返回到下一条指令(pc-4),只是他们在执行时,PC的值并没有更新,所以pc= lr。

预取指令中止异常,也没有发生pc更新,但它还得重新执行发生异常的那条指令,所以pc=lr–4。

数据访问中止异常,发生了pc更新,并且它也需要重新执行发生异常的那条指令,所以pc=lr–8。

通过以上的介绍,可以看到造成单片机中断返回的原因非常多,每种方法的应对方案都不尽相同。在ARM芯片调试过程中遇到中断返回问题的朋友不妨仔细阅读本文,相信会从中找到问题的解决方法。也可收藏本文以备不时之需,在遇到错误的时候进行查阅。

-

单片机

+关注

关注

6078文章

45629浏览量

675253 -

ARM单片机

+关注

关注

0文章

53浏览量

10501

发布评论请先 登录

ARM单片机三种中断返回情况的分析与解决

ARM单片机三种中断返回情况的分析与解决

ARM单片机三种中断返回情况的分析与解决

51单片机定时器中断_51单片机中断系统_51单片机扩展中断的四种方法

单片机中断系统介绍_51单片机中断系统结构

ARM单片机和STM32单片机之间有什么区别

一文详解51单片机中断系统

一文详解ARM单片机三种中断返回情况

一文详解ARM单片机三种中断返回情况

评论