运放电流检测采样电路电压采样电路

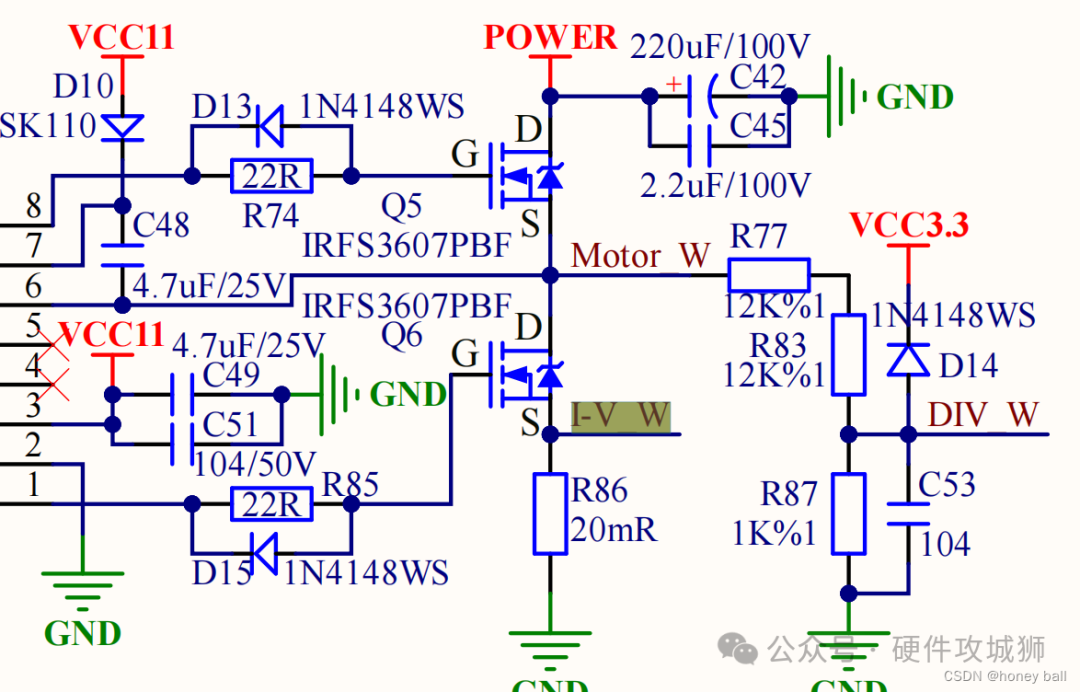

电流驱动电流检测电路

12个电路+10个知识点,讲透了开关模式下的电源电流检测!

以下正文

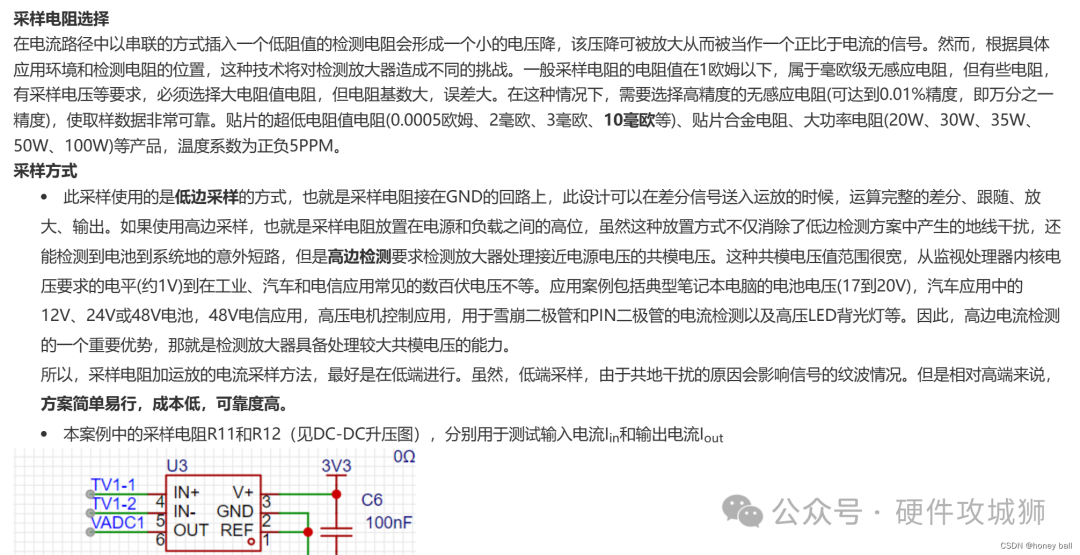

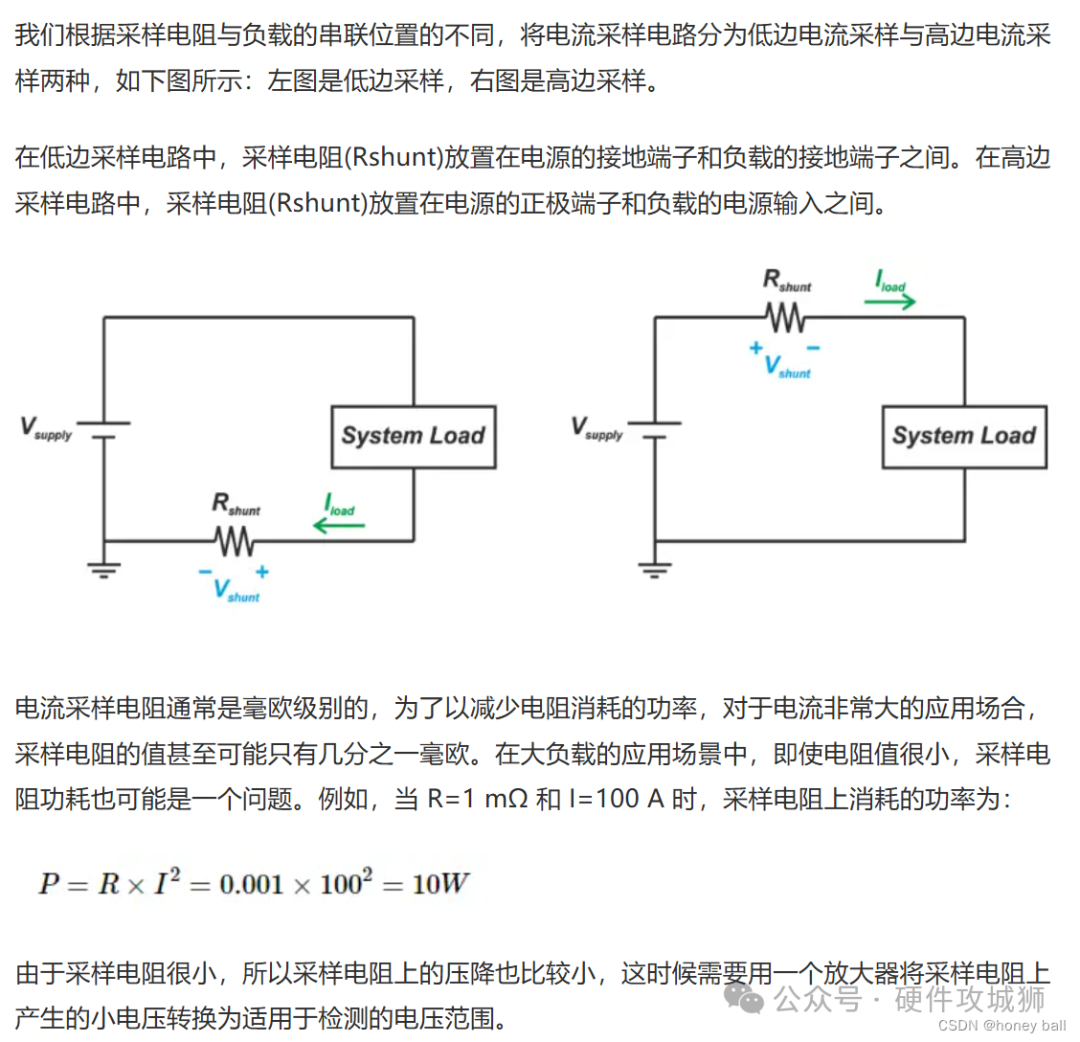

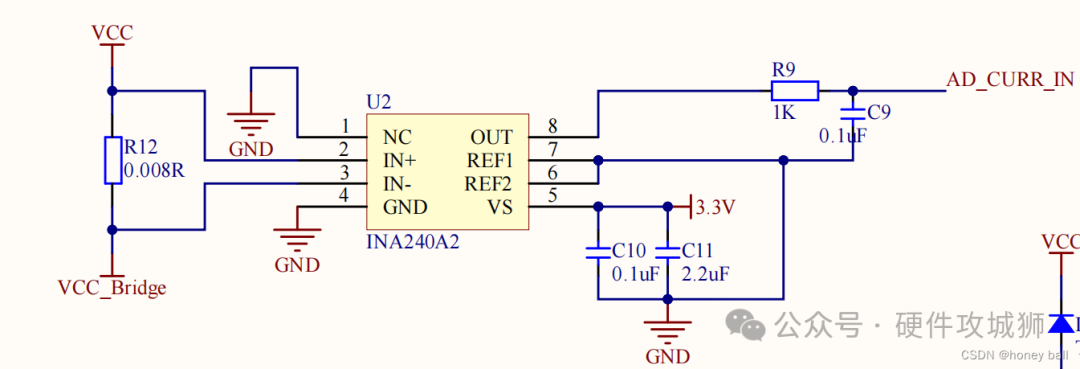

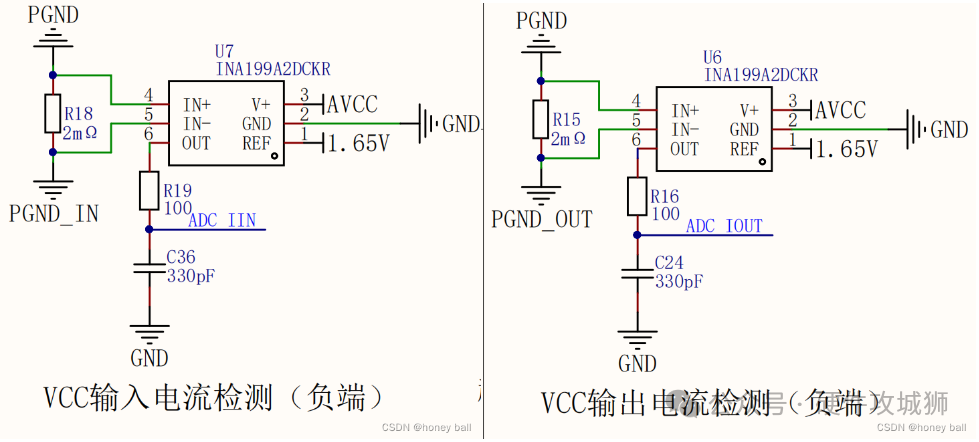

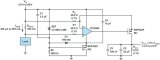

我们知道电流检测有两种方法:一种是用封装好的电流检测芯片+采样电阻;另一种是自己搭建运放电路:

高端检测:

低端检测:

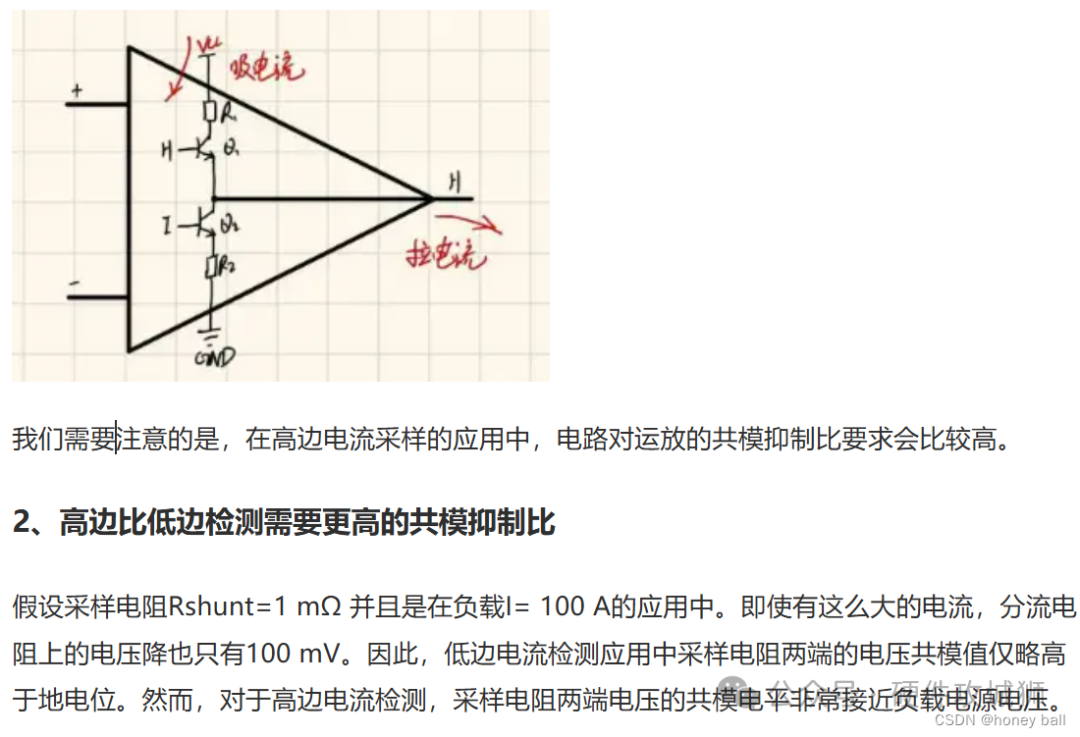

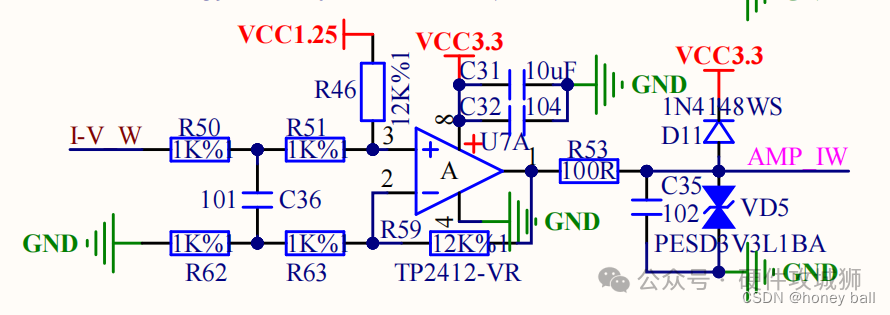

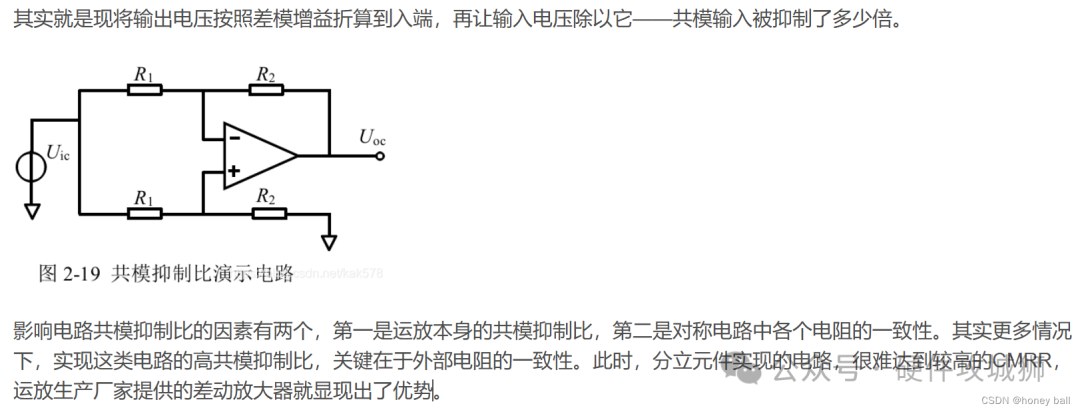

自己搭建运放电路:(这种对电阻的精度要求较高,对称电路中电阻的一致性,为了减小共模抑制比)

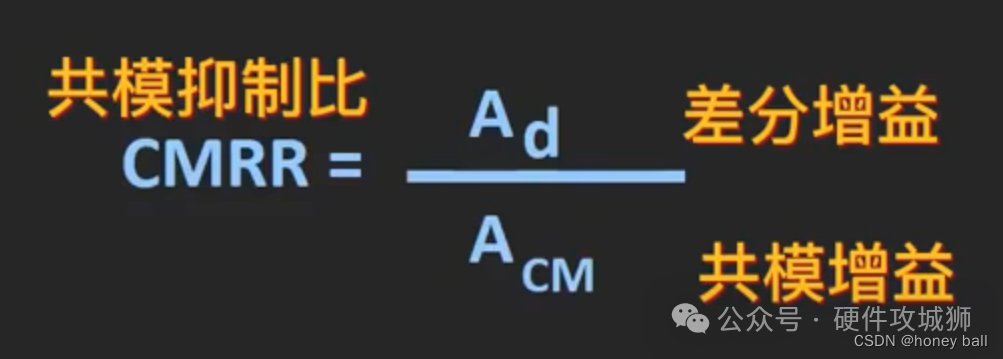

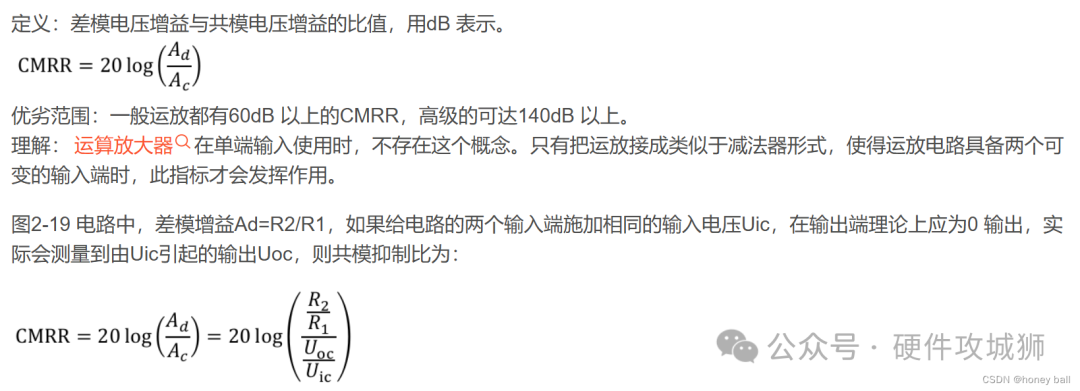

共模抑制比:

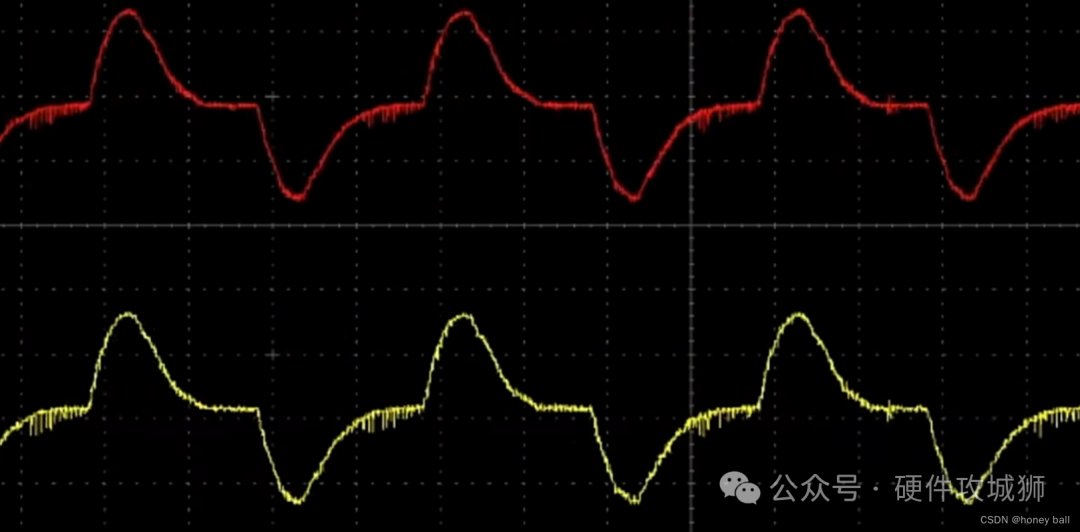

共模电压波形:

一般运放的共模抑制比在60---120之间:

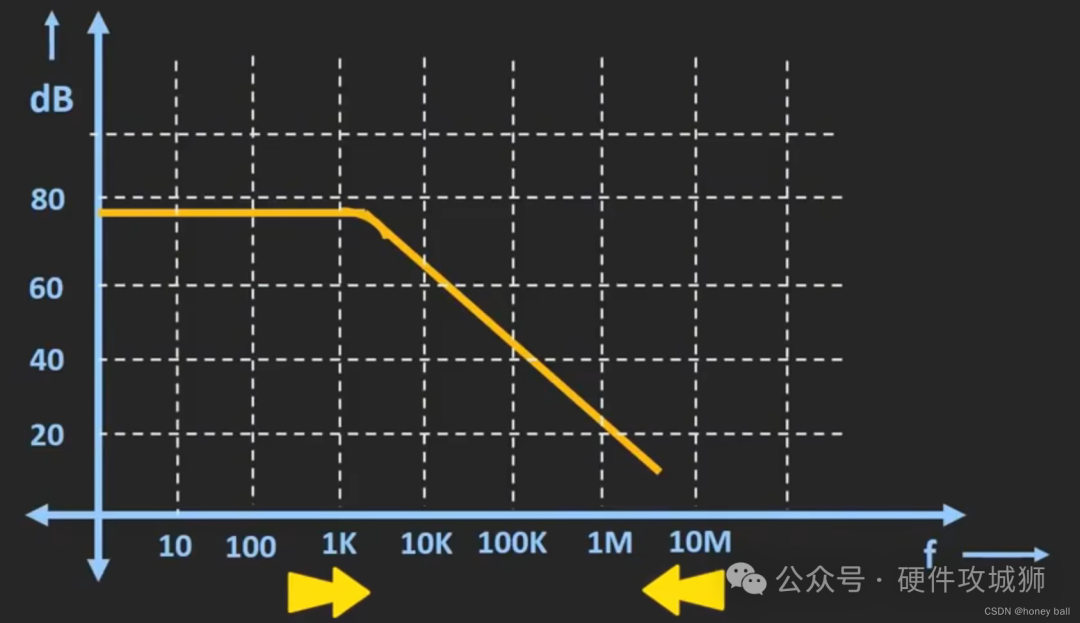

共模抑制比频率曲线图:当频率处于高频的时候,共模抑制比就会大幅减小,无法抑制共模信号:

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

电流检测

+关注

关注

14文章

497浏览量

41011 -

共模抑制比

+关注

关注

3文章

79浏览量

15939 -

采样电阻

+关注

关注

0文章

18浏览量

4263

原文标题:高、低边电流检测中采样电阻和共模抑制比的问题

文章出处:【微信号:mcu168,微信公众号:硬件攻城狮】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

怎么测ADS1299芯片的共模抑制比?

怎么测ADS1299芯片的共模抑制比?将通道1的正负极输入短接,接入一个0.5VP,共模电压2.5V,F=50Hz,FFT图像显示输出在50Hz时,为80dB。然而手册是-110dB,应该怎么测出-110dB的共模抑制比呢?

发表于 11-15 06:26

高边电流检测电路如何提升共模电压

的影响。这种放大器通过比较两个输入信号的差值来放大信号,而对共模信号(即两个输入信号共有的部分)则具有较强的抑制能力。在高边电流检测电路

INA128共模抑制比波形失真是为什么?

按照图接法,后面跟0.5~100Hz的贝塞尔带通滤波器,测INA128共模抑制比波形失真,在输入频率很低时,几十Hz时波形会上面一部分被截平,频率变高到100Hz以后波形变得正常。这是为什么?

发表于 09-20 07:35

影响电路共模抑制比的因素有哪些?如何去提高电路的共模抑制比?

此电路用来检测脑电波的信号,性能要求此电路的共模抑制比要达到不低于80dB,而现在实测只能达到67dB,想知道,影响电路共模抑制比的因素有哪些?如何去提高电路的共模抑制比?

发表于 08-20 07:21

运放的共模抑制比和电源抑制比对输出精度的影响是什么?

1、很多人用运放选共模抑制比越大越好,考虑到成本,我想计算一下理论值到底符不符合,比如我采分流器上的电流±74A,Gain=0.0335,共模输入电压有5V,电流精度要满足0.05%,假如运放

发表于 08-15 07:43

INA199A1共模抑制比低了是什么原因导致的?

最近设计的一款电路输出电流采用INA199高侧采样,VCC=5V,检流电阻12mR,REF接GND。

使用INA199A1,50倍放大系数,电流

发表于 08-13 07:29

消除共模噪声的秘密武器-共模抑制比

一、什么是共模抑制比?共模抑制比(CMRR)是衡量放大器对共模信号抑制能力的一个关键指标,是用来描述设备抵御共模信号影响的能力。共模信号是指同时存在于两个输入端并具有相同大小和相位的信号,例如电源

同相比例放大器为什么对共模抑制比要求高?运放的共模抑制比如何仿真?

同相比例放大器为什么对共模抑制比要求高?运放的共模抑制比如何仿真? 同相比例放大器是一种常见的放大电路,用于放大微弱信号。在应用中,通常需要对放大的信号进行差分测量,即对信号的差值进行

探讨高、低边电流检测中的采样电阻与共模抑制比问题

探讨高、低边电流检测中的采样电阻与共模抑制比问题

评论