雷达数据采集及图像显示是雷达的一个基本应用,普遍应用于军事、气象预测、环境监测、船舶导航等领域。雷达数据具有实时性、高速性的特点。一般说来,对雷达信号采样的时钟频率在100MHz以上,雷达数据采集和处理单元的数据吞吐量要求在Gbits/s以上。因此,要实现一个雷达数据采集和图像显示系统,对处理器的处理速度要求很高。传统的雷达数据采集和图像显示系统采用的是微处理器+FPGA(或DSP)方案,利用微处理器实现操作系统、雷达GUI和显示器控制,利用FPGA(或DSP)实现高速雷达数据采集和处理,这种方案的缺点是要想实现雷达图像在800*600以上分辨率的大屏幕显示比较困难,要么有较高的处理器速度,要么有独立显卡的支持,这样增加了系统复杂度和成本。

SOPC 是一种特殊的片上系统,建立在可编程逻辑技术的基础上,尽可能将一个大而完整的电子系统实现在一块FPGA硅片上,具有硬件可裁剪、可扩充、可升级,软件在系统可编程的特点,使得设计的系统在规模、功能、体积、性能、上市周期、开发成本等方面有着了很大的优势。基于SOPC技术的软核处理器主频虽然不是很高,目前Xilinx公司的microblaze处理器最高主频为210MHz、240DMIPS的运算能力,Altera公司的NIOS II处理器最高主频为340MHz、290DMIPS的运算能力,但是由于其极强的灵活性,可以通过软硬件协同设计,在处理器速度不高的情况下,解决需要高速度处理器才能完成的问题。

本文基于SOPC技术,提出一种在主频较低的软核处理器上实现雷达数据采集和图像大屏幕显示的方法。

2总体方案设计

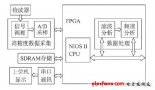

本设计采用microblaze软核处理器作为开发平台,SOPC系统框图如图1所示。

图1 系统硬件结构框图

本设计通过以下办法,解决在主频较低的SOPC软核处理器上实现雷达数据采集、处理和大屏幕图像显示的问题。

首先,使用FPGA硬件逻辑设计实现雷达数据采集、处理和显示控制器。雷达数据采集、处理模块负责对雷达上单元、ADC芯片的控制和对雷达数据的处理。显示控制器模块完成显存数据的管理和显示器的驱动。

其次,使用DMA传输。DMA负责将雷达数据采集、处理后数据通过DMA通道送到内存中。

最后,根据SOPC硬件可配置、可裁剪的特性,将雷达数据采集和处理模块、显示控制模块和DMA模块作为microblaze处理器的设备挂载到外设局部总线上[4]。

由于雷达数采集、处理模块和显示控制模块的内部逻辑都由FPGA硬件逻辑完成,微处理器不需直接对雷达上单元、ADC进行控制,不需进行复杂的雷达数据处理,不用对显存数据进行管理,不用控制产生高速的信号驱动显示器,从而大大减轻了处理器的负担,加上DMA传输的使用,处理器只需要处理DMA传输的请求和传输完成中断,从而使处理器从繁重的数据传输中解脱了出来。通过以上办法,处理器的负担已经变得很轻,使得较低的处理器速度即可处理系统的任务。而且显示控制由FPGA硬件实现还有个优点是,使得显示器分辨率的大小对处理器的负担影响很小,从而在处理器较低的情况下,同样可以支持大屏幕的图像显示。

-

sopc

+关注

关注

2文章

248浏览量

64791 -

数据采集

+关注

关注

42文章

8394浏览量

121346

发布评论请先 登录

LCoS显示技术的大屏幕HDTV介绍

SoPC技术在图像采集和处理系统中的应用设计

一种基于SOPC和USB2.0接口的高速数据采集系统及虚拟仪器设计

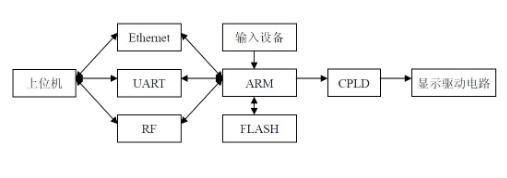

如何设计大屏幕显示器控制系统?

FPGA+DSP的红外图像数据采集与显示

SOPC基础上的数据采集系统设计

基于SOPC的数据采集与处理系统设计

基于LED显示技术的会展用大屏幕的设计与实现

LED大屏幕显示屏控制系统的总体设计框架图解析

基于SOPC技术实现雷达数据采集和图像大屏幕显示

基于SOPC技术实现雷达数据采集和图像大屏幕显示

评论