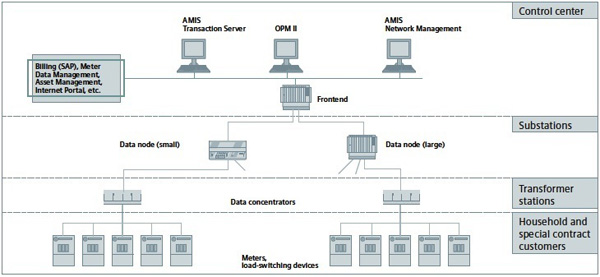

本文档介绍了采用C2000系列双核(CM3+C28x)微控制器实现的,基于PRIME标准的电力线通信(PLC)数据集中器方案。本方案通过一颗Concerto MCU加SDRAM实现完整的PRIME协议栈,提供波特率115200bps的UART异步串行端口给客户端主机进行网络管理及数据通信,为需要低成本实现数据集中器功能的场合提供了有效的解决方案。

简介

PRIME-PoweRline Intelligent Metering Evolution标准是由西班牙Iberdrola电力公司联合有关的PLC芯片、系统、电表等厂商,为窄带PLC电力线通信制定的远程抄表技术标准,包括物理层和MAC层的数据传输标准。该技术的协议开放,实施无版权费用,不同厂商的产品能够实现互联互通。TI采用低成本的DSP控制器,以软件的方式来实现PRIME协议,相较其他厂商以专用芯片ASIC的实现方式,提高了应用的灵活性。

事实上,早前TI已经采用OMAP1808实现了PRIME数据集中器的完整功能。本文介绍的方案,主要是将OMAP平台的DC方案移植到单芯片Concerto上,实现一颗芯片完成PRIME的上层和底层MAC协议以及物理层协议,适用于低成本的嵌入式数据集中器应用,因此,我们也把该数据集中器方案简称为EDC,即Embedded Data Concentrate。

OMAP1808平台的DC方案基于Linux操作系统,而本EDC方案基于TIRTOS操作系统,上层和下层MAC通信采用内部数据共享,不但系统精简很多,占用资源少,而且数据更加可靠,除了没有TCP/IP接口之外,所能管理及连接的节点数量与OMAP平台的DC方案无异。

1 EDC系统架构

本方案采用Concerto系列芯片F28M35H52C1作为主芯片,处理PRIME协议的UPPER MAC及LOW MAC, PHY层协议。F28M35H52C1是一款双核的MCU,它内部包含了Cortex m3主系统和TI C28x控制子系统两个MCU系统,每个系统分别有512KB的Flash空间,Cortex m3独立使用32KB RAM,TI C28x独立使用36KB RAM,另外还有可配置使用权的 64KB的共享RAM(在EDC系统中全部被分配给C28x使用)和2KB的IPC Message RAM。在EDC系统应用中,Cortex m3核工作主频为75MHz,它负责处理Upper MAC协议,C28x核工作主频为150MHz,它负责处理Low MAC及PHY层协议,两个核之间通过IPC内部数据共享区机制进行通信。主芯片MCU外加一个8M Bytes的SDRAM,由CM3核进行访问,用来存储节点信息数据库等数据,目前系统使用的大小约为3M Bytes;另外有一个128KByts 的EEPROM,由C28x访问,用来存储系统掉电参数;模拟前端采用TI AFE031,支持三相和单相连接,由C28x核通过SPI接口对其进行控制。系统框图如图1 所示。其中,CM3 通过1个GPIO口控制一个LED,在系统正常工作时以1Hz频率进行显示;C28x通过3个GPIO控制另外三个LED,分别指示C28x工作状态及PLC通信状态。

图1 PRIME EDC系统架构示意图

2 EDC方案特性

单芯片实现PLC PRIME DC完整功能。

提供UART接口与PC或用户Host Processor进行通信,通信速率115200bps,8位数据位,1位停止位,无奇偶校验。

提供PC(Ubuntu Linux OS)客户端软件进行模拟测试,客户端软件通过mgmt及IEC-432 API接口与EDC上运行的服务器端进行通信,用户可参考这些客户端软件示例代码实现Host代码设计,客户端软件包括:

Management tool application

Base node conference tool application

IEC 61334-4-32 data transfer application

硬件设计保留C28x的SCIA UART通信接口,便于客户使用TI提供的PC端ZCG工具软件,通过连接PC的COM口或USB-UART转接板至该接口来单独对PLC PHY层参数进行测试。

3 硬件设计

3.1 参考原理图

硬件相关的原理图部分设计请参考图2,图3,图4 所示。

图2 主芯片MCU参考设计原理图

图3 SDRAM及UART接口参考设计原理图

图4 AFE031周边电路参考设计原理图

-

电力线

+关注

关注

1文章

89浏览量

23492

发布评论请先 登录

相关推荐

基于AM335x ARM Cortex-A8 处理器的数据集中器参考设计包含原理图和物料清单

可进行电力线通信的智能电表开发平台 (SMB 3.0)包括原理图,物料清单及光绘文件

基于TIRTOS操作系统的PRIME电力线通信数据集中器

如何为数据集中器选择合适的处理器

一种新型自动抄表系统数据集中器的设计

Atmel携手威胜开发基于PLC的智能电表和数据集中器的MoU

德州仪器智能数据集中器评估板提供灵活平台,可连接并管理超过2000个电表

基于C2000的集成电力线载波通信功能(PLC)光伏逆变系统

TI基于Concerto双核MCU的PRIME电力线通信数据集中器方案应用说明

采用C2000系列双核实现电力线通信(PLC)数据集中器方案

采用C2000系列双核实现电力线通信(PLC)数据集中器方案

评论