本文介绍了半大马士革工艺:利用空气隙减少寄生电容。

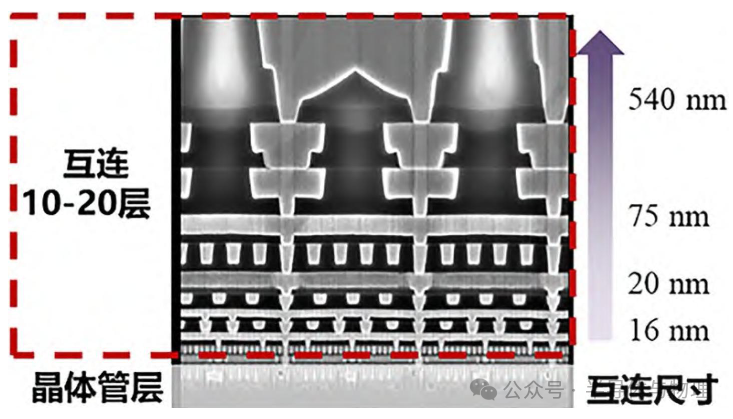

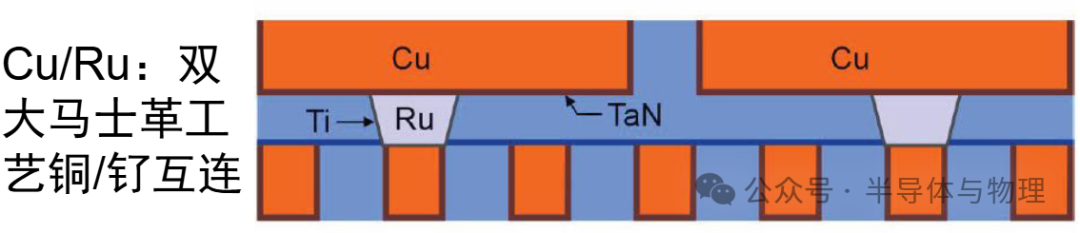

随着半导体技术的不断发展,芯片制程已经进入了3纳米节点及更先进阶段。在这个过程中,中道(MEOL)金属互联面临着诸多新的挑战,如寄生电容等问题。为了应对这些挑战,人们提出了大马士革(semi-damascene)工艺,特别是在使用钌(Ru)作为互连材料时,这种工艺显示出了显著的优势,尤其是通过引入空气隙来减少寄生电容。

传统铜互连的问题

在传统的铜互连工艺中,随着制程节点的不断缩小,寄生电容和电阻问题变得日益严重,导致信号延迟增加,性能下降。为了解决这些问题,研究人员开始寻找替代材料和技术。

钌(Ru)作为互连材料

钌(Ru)作为一种低电阻、高可靠性的金属,成为了下一代互连材料的有力候选。钌具有以下优点: 低电阻:钌的电阻率远低于钴(Co),接近于铜(Cu),即使在极小尺寸下,其电阻增长速度也较慢。 高可靠性:钌具有出色的抗电迁移能力和高可靠性,特别适合未来的5纳米及更先进节点。 惰性和硬度:钌具有很高的惰性和硬度,不易通过化学机械抛光(CMP)去除,这使得传统的双大马士革工艺在CMP过程中容易对低k介质造成损伤,导致成品率下降。

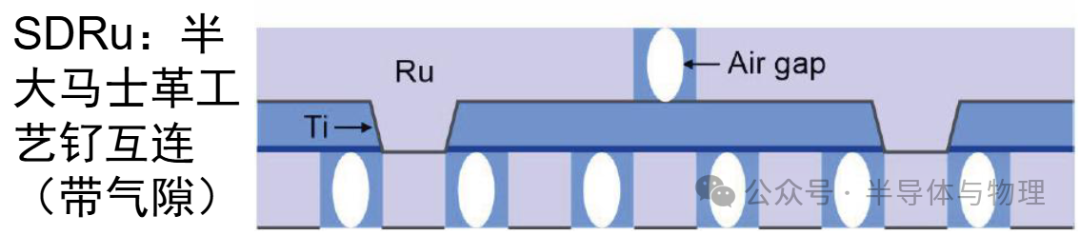

空隙的重要性

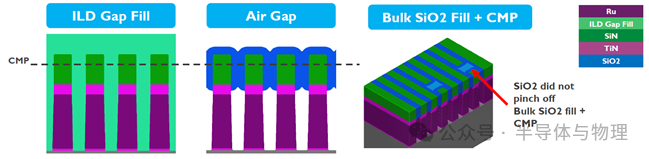

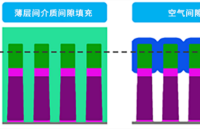

空隙(airgap)在半大马士革工艺中起到了关键作用,它可以显著降低金属线间的寄生电容,从而减少RC延时。具体来说,空气隙的引入可以: 减少电容:空气隙的介电常数接近于1,远低于传统介质材料(如二氧化硅,介电常数约为3.9),因此可以显著降低寄生电容。 提高性能:通过减少寄生电容,可以提高信号传输速度,减少信号延迟,从而提升整体性能。 降低功耗:减少寄生电容还可以降低信号传输过程中的能量损失,从而降低功耗。

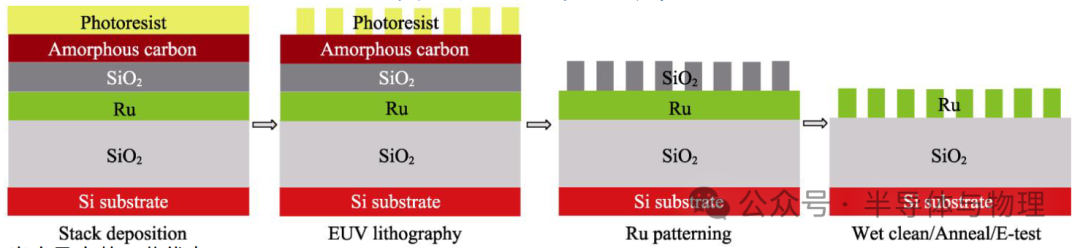

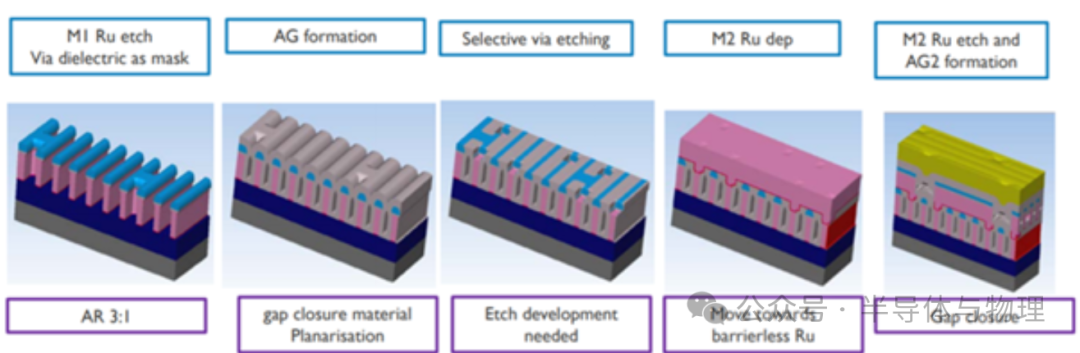

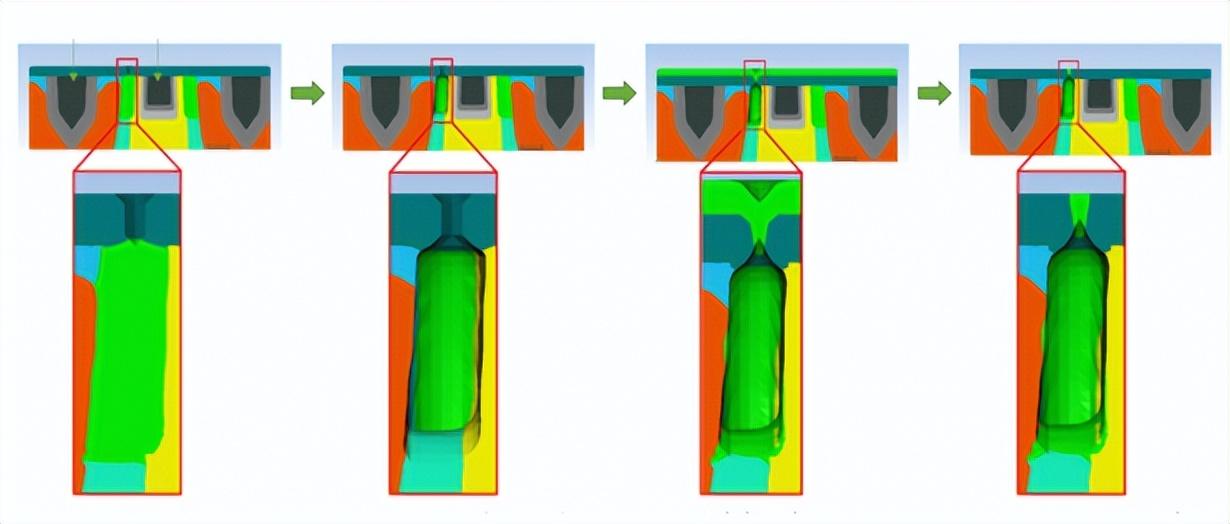

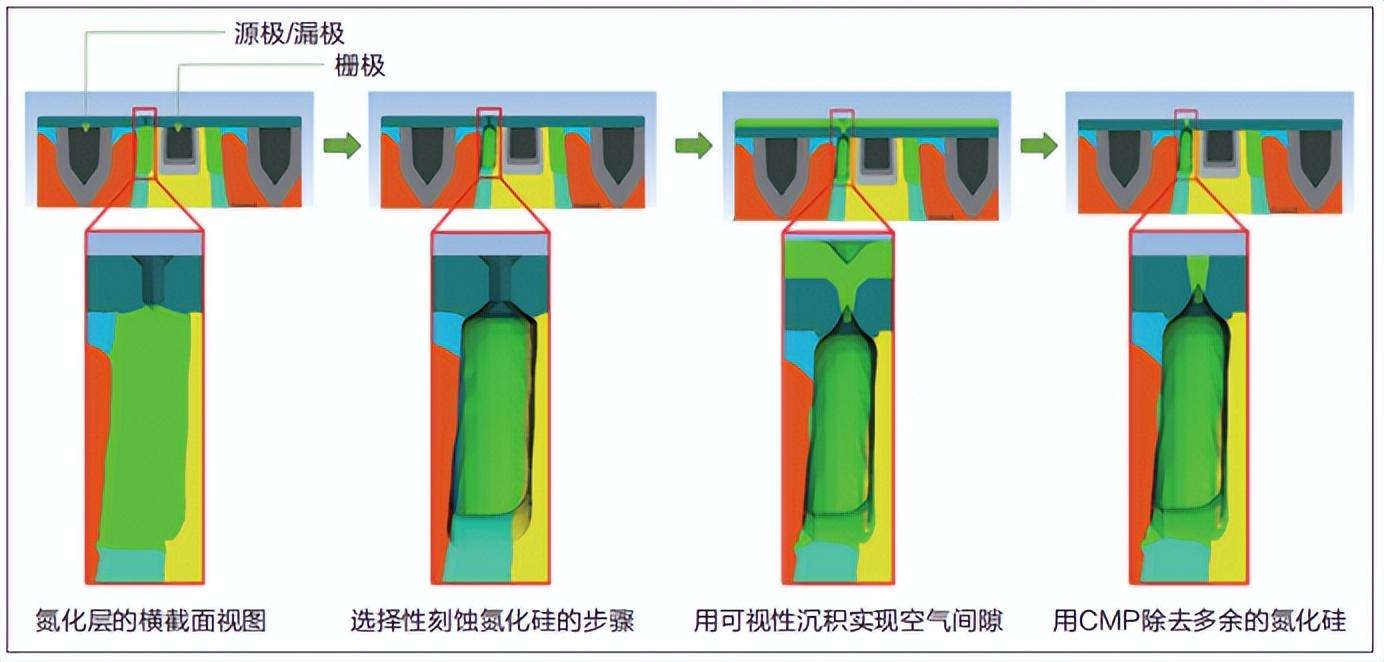

半大马士革工艺流程

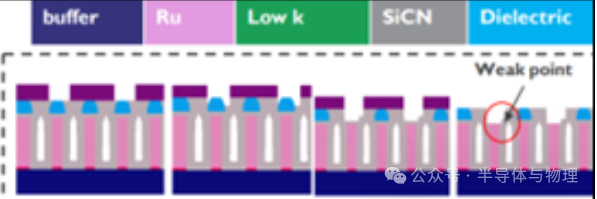

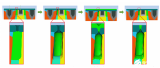

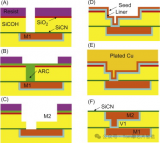

M1 Ru刻蚀:使用介质作为掩模,刻蚀出M1层的钌金属线图案。 空气隙形成:使用ALD沉积一层绝缘层,在M1层的钌金属线之间形成空气隙,以减少寄生电容。 选择性通孔刻蚀:刻蚀出通孔,以便连接上下层金属线。 M2 Ru沉积:在通孔和M2层的图案上沉积钌金属。 M2 Ru刻蚀和空气隙形成:刻蚀出M2层的钌金属线图案,并在M2层的钌金属线之间形成空气隙。

空隙的挑战与解决方案

尽管空气隙在减少寄生电容方面具有显著优势,但在实际应用中仍面临一些挑战,例如空气隙闭合的控制、平面化的要求等。研究人员通过仿真和实验,逐步解决了这些挑战,确保了工艺的稳定性和可靠性。

空气隙闭合控制:在M1层的钌金属线之间形成空气隙后,需要精确控制空气隙的闭合,以确保空气隙不会在后续工艺步骤中意外打开。这需要高精度的刻蚀和沉积工艺。 平面化:空气隙形成后,需要进行平面化处理,以确保介质层的表面平整,不影响后续工艺步骤。这通常通过化学机械抛光(CMP)实现。 材料选择:选择合适的空气隙闭合材料(如SiCN)和刻蚀工艺,以确保空气隙的稳定性和可靠性。

-

电容

+关注

关注

100文章

6034浏览量

150246 -

寄生电容

+关注

关注

1文章

292浏览量

19225

原文标题:半大马士革工艺:利用空气隙减少寄生电容

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

PCB寄生电容的影响 PCB寄生电容计算 PCB寄生电容怎么消除

如何采用铜互连单大马士革工艺制作超厚金属铜集成电感的概述

实现3nm技术节点需要突破哪些半导体关键技术

什么是寄生电容_寄生电容的危害

引入空气间隙以减少前道工序中的寄生电容

引入空气间隙以减少前道工序中的寄生电容

寄生电容对MOS管快速关断的影响

什么是铜互连?为什么铜互连非要用双大马士革工艺?

半大马士革集成中引入空气间隙结构面临的挑战

半大马士革工艺:利用空气隙减少寄生电容

半大马士革工艺:利用空气隙减少寄生电容

评论