纵观历史,但凡能够大幅提升生产力的技术必将大规模应用并深刻改变社会发展进程。以大模型为代表的新AI第一次使智能体具备了主动学习和泛化能力,为生产力的发展带来质的飞跃,未来数字世界和物理世界的绝大多数事物都将接入大模型新AI,进行智能化升级,引发新一轮工业革命。

互联网和移动互联网的发展历史表明,越贴近用户,其应用场景越大,产业价值越高。大模型最大的应用场景在终端和边缘端。未来所有的终端和边缘端设备都值得用大模型重新做一遍,为数十万亿规模的电子信息制造业提供增量市场和高质量发展的机遇。

大模型需要在资源有限的终端设备上高效运行,对芯片的AI部署通用性、易用性、经济性等提出了更高的要求。进迭时空的实践表明,RISC-V作为开源开放的下一代计算架构,以通用CPU核为基础,结合少量DSA定制和大量微架构创新,不仅具备完整CPU功能,更拥有强大的原生AI算力,可以为端侧大模型落地应用提供全新的解决方案。

1

RISC-V新CPU提供强大的AI通用性

进迭时空SpacemiT Key StoneK1凭借其开放性和可编程性,能够轻松接入ONNXRuntime等主流开源生态。这一特性不仅降低了部署大量现有AI模型的门槛,还天然支持了timm、onnx modelzoo、ppl modelzoo等开源模型仓库的模型,以及所有的公开onnx模型。这意味着,无论是传统的小模型还是当下火热的大模型,如qwen系列、llama系列、minicpm系列、phi系列、chatglm系列、gemma系列等,都能在这款AI CPU上得到高效支持。

尤其是,进迭时空SpacemiT Key StoneK1的原生AI算力具有极强的可编程性,支持主流低bit量化方式,从而极大地降低了大模型的带宽需求。K1芯片运行主流的5亿参数大模型可以实现每秒20个token的优异性能。

2

RISC-V新CPU提供强大的AI便捷性

借助主流开源生态,进迭时空不仅扩充了模型仓库,还实现了低成本的迁移ONNXRuntime生态中的各种案例。此外,通过云端通用AI助手,用户只需通过自然语言描述,即可实现AI部署。由于AI CPU支持全集ONNX算子,用户只需修改模型路径和摄像头设备号,即可成功进行部署,极大地简化了操作流程。

3

RISC-V新CPU构建本地大模型推理应用

进迭时空在SpacemiT Key StoneK1芯片上构建了以通义千问(qwen2.5-1.5B-coder)为基础的本地AI助手。借助本地AI助手,用户可以通过自然语言描述实现AI部署,无需依赖网络连接,进一步提升了AI应用的便捷性和安全性。

未来,进迭时空将继续坚持RISC-V+AI技术路线,通过技术创新带来更具竞争力的解决方案,为大模型在终端和边缘端的普及提供强有力的支持。

来源:进迭时空

-

cpu

+关注

关注

68文章

10940浏览量

213718 -

RISC-V

+关注

关注

46文章

2362浏览量

47004 -

大模型

+关注

关注

2文章

2746浏览量

3394

发布评论请先 登录

相关推荐

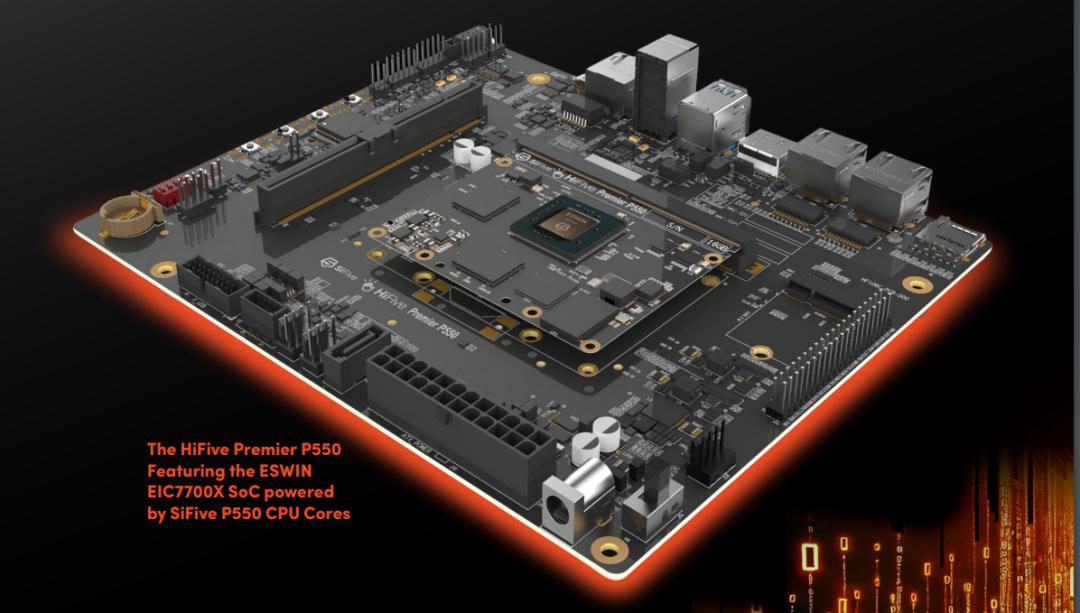

SiFive 推出高性能 Risc-V CPU 开发板 HiFive Premier P550

RISC-V,即将进入应用的爆发期

加入全球 RISC-V Advocate 行列,共筑 RISC-V 的未来 !

RISC-V Summit China 2024 青稞RISC-V+接口PHY,赋能RISC-V高效落地

RISC-V Summit China 2024 | 青稞RISC-V+接口PHY,赋能RISC-V高效落地

2024 RISC-V 中国峰会:华秋电子助力RISC-V生态!

建设进展 | 全球首家 RISC-V 开源创新中心落地深圳

RISC-V为何如此重要?

IC咖啡沙龙“芯未来”公益讲座丨仇健乐:RISC-V指令架构赋能端侧智能芯片产业化落地

解锁RISC-V技术力量丨曹英杰:RISC-V与大模型探索

瑞萨推出采用自研CPU内核的通用32位RISC-V MCU 加强RISC-V生态系统布局

RISC-V 基础学习:RISC-V 基础介绍

Imagination:RISC-V CPU的重要力量

RISC-V新CPU为端侧大模型落地应用提供新范式

RISC-V新CPU为端侧大模型落地应用提供新范式

评论