在ASIC(专用集成电路)集成电路设计过程中,设计师们可能会遇到一系列常见问题。以下是对这些问题的归纳与解析:

一、前端设计问题

- RTL编码问题

- 功能验证问题

- 功能验证是设计过程中的关键步骤,用于在进入下一阶段之前识别、解决和调试潜在问题。然而,功能验证可能非常复杂且耗时,特别是在大型ASIC设计中。

- 在功能验证中,需要确保所有条件分支都被正确赋值,以避免潜在的Latch问题。

二、后端设计问题

- 布局布线问题

- 在布局布线阶段,需要仔细考虑信号完整性、配电和热管理等因素。随着工艺技术的发展,信号串扰的机会增加,因此需要采取一系列措施来减少串扰,如增加金属信号线之间的间距或采取屏蔽措施。

- 布局布线还需要考虑时钟树的插入和全局布线,以确保时钟信号能够均匀分布到整个芯片上。

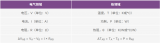

- 静态时序分析问题

- 静态时序分析是后端设计中的关键步骤,用于检查设计是否满足时序约束。然而,随着设计规模的增加和工艺技术的提高,静态时序分析变得越来越复杂和耗时。

- 在静态时序分析中,需要提取布局布线后的寄生参数,并根据提取的负载模型在不考虑任何串扰影响的情况下计算出信号延时。然后,将这些提取的延时标注到设计中,并使用静态时序分析工具来判定不正确的时序。

- 物理验证问题

- 物理验证包括设计规则检查(DRC)、版图一致性检查(LVS)等步骤,用于确保布局布线后的设计满足制造要求。然而,随着设计复杂性的增加,物理验证变得越来越困难且耗时。

- 在物理验证中,需要仔细检查布局布线是否满足制造规则、电源和地是否连接正确、以及各个模块之间的连接是否一致等问题。

三、其他问题

- 功耗问题

- ASIC设计需要仔细考虑功耗问题,以确保芯片在低功耗下运行。然而,随着设计规模的增加和性能要求的提高,功耗问题变得越来越突出。

- 为了降低功耗,可以采用多种技术,如动态功耗管理、电源门控、时钟门控等。然而,这些技术的实现需要仔细权衡性能和功耗之间的折衷关系。

- 可测性设计问题

- 可测性设计(DFT)是ASIC设计中的一个重要方面,用于提高芯片的测试覆盖率并降低测试成本。然而,随着设计复杂性的增加和测试要求的提高,DFT变得越来越困难且耗时。

- 为了解决DFT问题,可以采用多种技术,如扫描链插入、内建自测试(BIST)等。然而,这些技术的实现需要仔细考虑测试覆盖率、测试时间和测试成本之间的折衷关系。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

集成电路

+关注

关注

5464文章

12695浏览量

375801 -

asic

+关注

关注

34文章

1278浏览量

124967 -

信号完整性

+关注

关注

68文章

1500浏览量

98266 -

编码

+关注

关注

6文章

1041浏览量

57151

发布评论请先 登录

相关推荐

热点推荐

“2026中国强芯评选”正式开始征集! 六大奖项,覆盖集成电路产业全链条!

由中国集成电路设计创新联盟、国家“芯火”双创基地(平台)、《中国集成电路》杂志社、芯脉通会展策划主办的“2026中国集成电路设计创新大会暨第六届创芯应用展”(ICDIA创芯展)将于8月

集成电路版图设计的核心组成与关键步骤

在集成电路设计中,版图(Layout)是芯片设计的核心环节之一,指芯片电路的物理实现图。它描述了电路中所有元器件(如晶体管、电阻、电容等)及其连接方式在硅片上的具体布局。版图是将

CW32系统有哪些常见问题?

在CW32系统中,可能会遇到一些常见问题,包括但不限于:

重复定义函数:例如在a.c里定义了函数void func(),在b.c里也定义了一个void func()。这会导致编译时出现错误,需要

发表于 12-15 06:47

东莞理工学院“小眼睛科技杯”第四届集成电路设计与创新应用竞赛圆满落幕

BASEDINNOVATION“小眼睛科技杯”集成电路设计与创新应用竞赛2025年11月23日,东莞理工学院第四届集成电路设计与创新应用竞赛于学术会议中心圆满落幕。本届竞赛由校团委、学生工作部

集成电路制造中薄膜刻蚀的概念和工艺流程

薄膜刻蚀与薄膜淀积是集成电路制造中功能相反的核心工艺:若将薄膜淀积视为 “加法工艺”(通过材料堆积形成薄膜),则薄膜刻蚀可称为 “减法工艺”(通过材料去除实现图形化)。通过这一 “减” 的过程,可将

功率集成电路应用中的通用热学概念

单芯片功率集成电路的数据手册通常会规定两个电流限值:最大持续电流限值和峰值瞬态电流限值。其中,峰值瞬态电流受集成功率场效应晶体管(FET)的限制,而持续电流限值则受热性能影响。数据手册中给出的持续

PDK在集成电路领域的定义、组成和作用

PDK(Process Design Kit,工艺设计套件)是集成电路设计流程中的重要工具包,它为设计团队提供了与特定制造工艺节点相关的设计信息。PDK 是集成电路设计和制造之间的桥梁,设计团队依赖 PDK 来确保设计能够在晶圆

华大九天Empyrean Liberal工具助力数字集成电路设计

数字集成电路设计中,单元库和IP库宛如一块块精心打磨的“积木”,是数字IC设计的重要基础。从标准单元库(Standard Cell)、输入输出接口(I/O Interface)、存储器单元(如

PCBA代工避坑指南:常见问题+解决方案全解析

和元器件采购。在这个过程中,PCBA代工代购成为一种高效、成本控制良好的解决方案。然而,企业在进行PCBA代工代购时,往往会遇到一些常见问题,影响项目进度和质量。 PCBA代工代购元器件常见问题及解决方案 一、

实用电子电路设计(全6本)——数字逻辑电路的ASIC设计

由于资料内存过大,分开上传,有需要的朋友可以去主页搜索下载哦~

本文以实现高速高可靠性的数字系统设计为目标,以完全同步式电路为基础,从技术实现的角度介绍ASIC逻辑电路设计技术。内容包括:逻辑

发表于 05-15 15:22

ASIC集成电路设计中的常见问题

ASIC集成电路设计中的常见问题

评论