AMD Versal AI 引擎使您能够扩展数字信号处理( DSP )算力与面向未来的设计,从而适应当前和下一代计算密集型 DSP 应用。借助 Versal AI 引擎,客户能以更低的功耗1和更少的可编程逻辑资源2获得高性能 DSP。

“Versal AI 引擎可以在降低功率预算的情况下提升 DSP 计算密度。这种效率使得 Versal AI 引擎能够在严格的功率预算内应对最严苛的 DSP 应用。”

—— Udayan Sinha

AMD 高级产品营销经理

可以从这些计算功能中受益的市场包括测试与测量、医学成像/医疗,以及其他需要在 GSPS 吞吐量范围内运行的高吞吐量实时 DSP 市场。

利用 AMD Vitis 统一软件平台,Versal AI Engine 设计可以通过基于 C 的设计流程进行编程。对于更倾向于基于模型的流程的工程师,则可以使用 Vitis Model Composer( MathWorks Simulink 插件)。此外,DSP 库函数、API 和增强型 IP 核的集合可实现高性能 DSP 设计的快速开发。

您可以访问 AMD GitHub 查看我们的 Versal AI 引擎 GitHub 设计教程和 DSP 库。

您也可以由我们的网络研讨会系列开始入手,来自 AMD 的专家将介绍 Versal AI 引擎技术并演示如何使用它们来加速各种有价值的 DSP 算法。该网络研讨会系列的主题包括:

Versal Adaptive SoC 与 AI 引擎技术介绍

使用 Versal AI 引擎加速多相信道器设计

使用 Versal AI 引擎加速 FFT 算法

如果您希望了解 Versal AI 引擎在 DSP 基准测试中与传统 HDL 实现的对比情况,请联系您的销售代表了解基准测试设计。

总之,Versal AI 引擎可以通过降低动态功耗和可编程逻辑资源来加速高性能 DSP 应用。如果您当前的 DSP 应用由于资源或功耗限制而遇到潜在的扩展问题,Versal AI 引擎是释放您当前和下一代 DSP 计算能力的理想解决方案。

1. 基于 AMD 于 2024 年 2 月委托的第三方基准测试,在信号处理应用 FIR 实现中,对带有 AMD Vitis for AI 设计工具的 AMD Versal 自适应 SoC 与带有 Vivado 软件和 Vitis Model Composer 工具版本 2023.1 的传统可编程逻辑进行了比较。结果为 3 种设计的平均值。结果会因设计规格而异。(VER-034)

2. 根据 AMD 于 2024 年 2 月委托第三方进行的基准测试,测试对象为搭载 AMD Vitis for AI 设计工具的 AMD Versal 自适应 SoC,以及在信号处理应用 FIR 实施中使用 Vivado 软件和 Vitis Model Composer 工具 2023.1 版本的传统可编程软件实施。结果取 4 个设计的平均值。结果将根据设计规格而有所不同。(VER-035)

-

dsp

+关注

关注

553文章

7998浏览量

348975 -

amd

+关注

关注

25文章

5469浏览量

134182 -

Xilinx

+关注

关注

71文章

2167浏览量

121454

原文标题:借助 AMD Versal AI 引擎释放 DSP 算力

文章出处:【微信号:赛灵思,微信公众号:Xilinx赛灵思官微】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

使用 AMD Versal AI 引擎释放 DSP 计算的潜力

贸泽开售适用于AI和机器学习应用的 AMD Versal AI Edge VEK280评估套件

AMD Alveo V80计算加速器网络研讨会

贸泽开售适用于高性能计算应用的AMD Alveo V80加速器卡

AMD发布第二代Versal自适应SoC,AI嵌入式领域再提速

AMD Versal SoC刷新边缘AI性能,单芯片方案驱动嵌入式系统

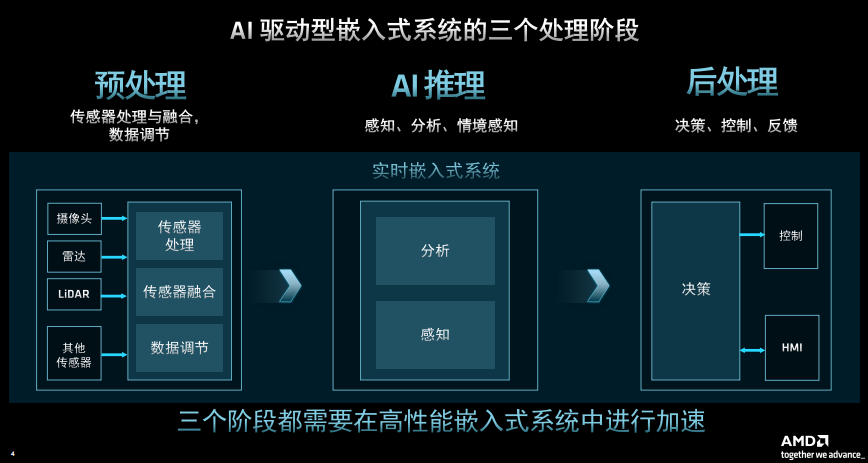

AMD推出第二代Versal器件,为AI驱动型嵌入式系统提供端到端加速

AMD Versal SoC全新升级边缘AI性能,单芯片方案驱动嵌入式系统

在Vivado中构建AMD Versal可扩展嵌入式平台示例设计流程

【ALINX 技术分享】AMD Versal AI Edge 自适应计算加速平台之 Versal 介绍(2)

AMD Versal AI Edge自适应计算加速平台之Versal介绍(2)

使用AMD Versal AI引擎加速高性能DSP应用

使用AMD Versal AI引擎加速高性能DSP应用

评论