本文翻译转载于:Cadence blog

作者:Paul Graykowski

混合信号设计在半导体设计飞速发展的过程中发挥着关键作用。混合信号设计将模拟与数字电路无缝集成至一个 SoC 上,为用户提供了显著的性能、尺寸和能效优势。

从广义上讲,混合信号集成电路是指结合了模拟与数字功能的集成电路(IC),不仅指这些域之间的接口,还指同时包含模拟和数字功能的组件的集成电路。它的应用范围涵盖了电源管理系统、用户接口(如触觉反馈),以及手机、笔记本电脑充电器、游戏控制器和 GPS 系统中找到的射频应用。

合二为一

模拟系统和数字系统属于不同的开发领域,开发工具和方法论也各不相同。数字设计工程师使用 Verilog、SystemVerilog 和 VHDL 等硬件描述语言(HDLs),以及数字逻辑仿真器和硬件仿真器进行创建和验证他们的设计。而模拟设计工程师则使用 SPICE 或 FastSPICE 等专业仿真器来分析和验证模拟组件。尽管数字设计工程师和模拟设计工程师都是专业人士,但他们都对对方领域的技术了解有限,如建模语言、仿真器和仿真技术。

混合信号设计旨在将这两个独立系统集成为一个 SoC 上的整体。要实现这一目标,就必须进行全面的系统验证,以确保系统功能正常。

设计验证

数字验证(DV)工程师通常使用以下先进工具和方法进行设计验证,其中包括通用验证方法学(UVM)、SystemVerilog 断言(SVA)、统一电源格式(UPF)和度量驱动验证(MDV)。这些工具和方法助力 DV 工程师生成测试激励、评估覆盖率、调试设计并无缝地运行回归测试。

然而,如何将这些技术扩展应用于模拟领域,以实现全面验证呢?虽然可以通过连接模拟与数字仿真器来进行模拟混合信号(AMS)仿真,但大量的进程间通信会大幅降低仿真运行速度,使其比纯数字验证慢很多。因此,AMS 仿真不总是适用于执行回归测试和 MDV 流程等任务。

验证的局限性

DV 工程师采用的传统解决方案是创建简单的存根模型(stub model)来隔离任何模拟和混合信号单元的数字部分,而不是运行 AMS 仿真。

借助存根模型,工程师可专注于数字部分的一维验证。然而,模拟工程师与数字工程师关于模拟-数字接口方面的看法分歧可能导致一些可以避免的工作失误,进而导致设计失败或代价高昂的硅片返工。此类工作失误包括引脚连接错误、极性反转、总线排序不当以及电源域连接错误。

实数建模(RNM)解决方案

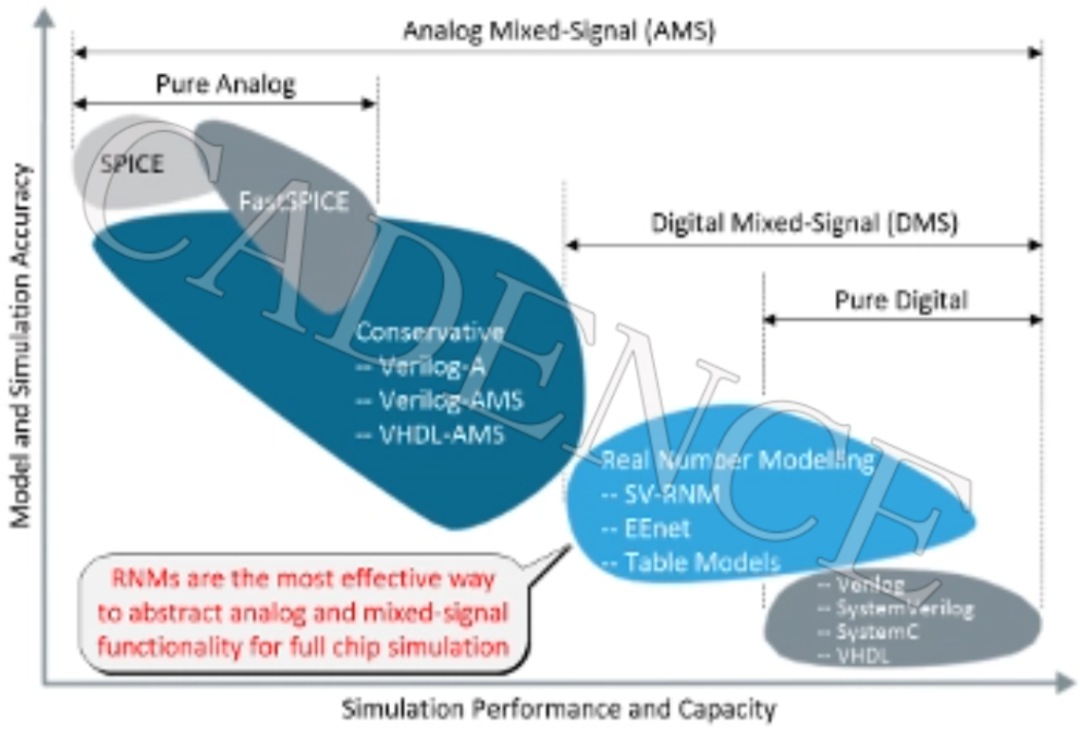

实数建模借鉴了模拟和数字仿真领域的理念。最重要的是,实数模型使用 DV 工程师熟悉的语言,例如 SV-RNMs 中使用的 SystemVerilog 语言。如下图 1 所示,该模型可使 DV 工程师使用逻辑仿真器和硬件仿真器进行数字混合信号(DMS)验证。

图 1:混合信号仿真的模型和仿真精度 vs. 性能与容量

DV 工程师可利用 RNMs 能够创建处理多于二态的模型,这些模型可以使用复杂的数学公式和实数值(如 3.142 或 16.893)。例如,DV 工程师可设计一个简化的 RNM,即模拟数字转换器。通过使用 RNM,工程师可以避免模拟电路中的许多复杂难题,只需专注于实数输入和整数输出即可。

此外,通过用 SystemVerilog 实现 RNM,DV 工程师可以利用熟悉的语言对混合信号接口进行细致和精确的建模,这不仅能提高验证流程的效率和精度、弥合模拟与数字领域之间的鸿沟,还使得在混合信号场景下应用 UVM 和功能覆盖成为可能。

值得注意的是,RNM 的应用范围十分广泛,不仅能用于电路模型,还能用于旋转和振动检测传感器,以及激光与光子处理器之间的的接口建模。

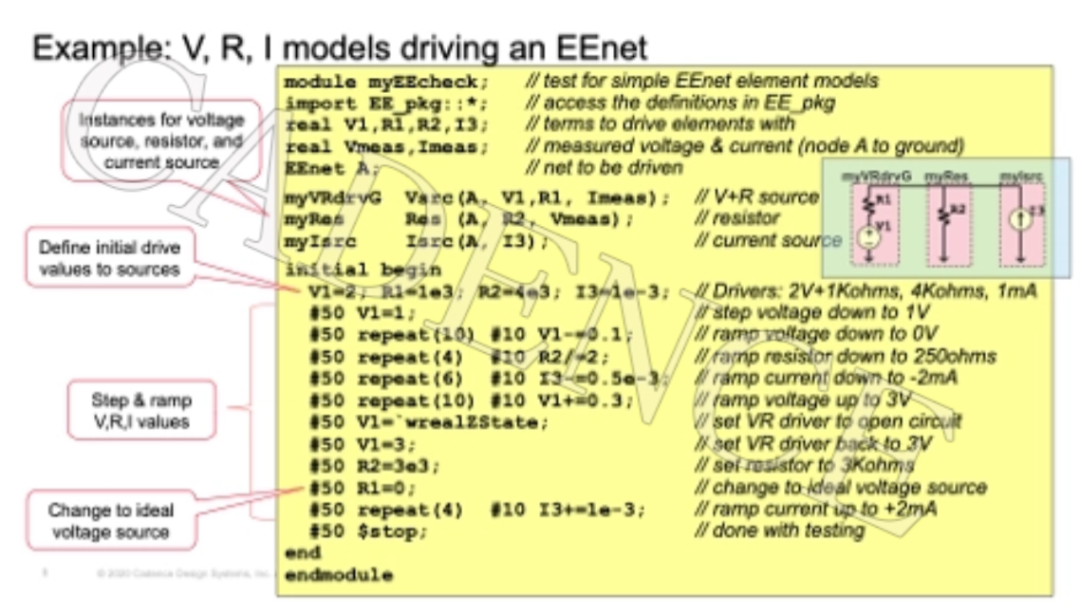

EEnet

在多数情况下,DV 工程师通常希望提高具体模拟和混合信号功能仿真的逼真程度。Cadence 的 Xcelium 与 Xcelium Mixed-Signal App 结合,可提供一个定制的参数化 RNMs EEnet 库,其中包含电阻、电感器、电容器、二极管、晶体管及运算放大器等 RNMs。DV 工程师可借助这些工具在 SystemVerilog 中精确构建模拟电路模型。事实证明,EEnet 模型可以实现高达 5 倍的运行效率,而且与 SPICE 模型相比,在精确度方面与后者只有 0.5% 的差距。

图 2:EEnet 模块

结论

RNMs 可以通过 DMS 仿真或硬件仿真简化数字领域的验证流程,使验证速度远超过 AMS 验证。同样值得注意的是,DV 工程师使用的所有标准工具和技术,如 UVM、SVA、UPF 和 MDV,均能够兼容应对设计中的模拟和混合信号问题。

总之,RNMs 可使 DV 工程师利用熟悉领域中的现有资源进行高效而全面的混合信号验证。

-

集成电路

+关注

关注

5400文章

11689浏览量

364529 -

半导体

+关注

关注

335文章

27970浏览量

225146 -

混合信号

+关注

关注

0文章

484浏览量

65086 -

Cadence

+关注

关注

65文章

934浏览量

142797 -

数字电路

+关注

关注

193文章

1631浏览量

81039

原文标题:利用实数建模简化混合信号验证流程

文章出处:【微信号:gh_fca7f1c2678a,微信公众号:Cadence楷登】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

利用实数建模简化混合信号验证流程

利用实数建模简化混合信号验证流程

评论