AMD推出了Versal Premium Series Gen 2,这是业界第一个支持CXL 3.1和PCIe Gen6的FPGA平台。

AMD为数据中心、航空航天、通信和T M市场设计了Versal Premium系列Gen 2。

随着人工智能和数据分析的加强,这些技术背后的基础设施必须跟上繁重的数据需求。数据中心互连系统的兴起提升了FPGA在处理复杂任务中的作用。随着内存可扩展性和安全性的进步,AMD推出了可扩展的Versal Premium Series Gen 2,以满足依赖快速、安全数据流的行业的需求。

所有关于电路与迈克,AMD的高级产品线经理,以了解新的FPGA的第一手资料。

高级互连

相反,Versal Premium Series Gen 2被描述为“流量副本”,而不是主要的AI加速器。

“我们正在启用AI,尽管GPU是这种情况下的主力,”他说。“我们的职责是快速有效地管理数据移动,以便GPU能够以最高水平运行。”

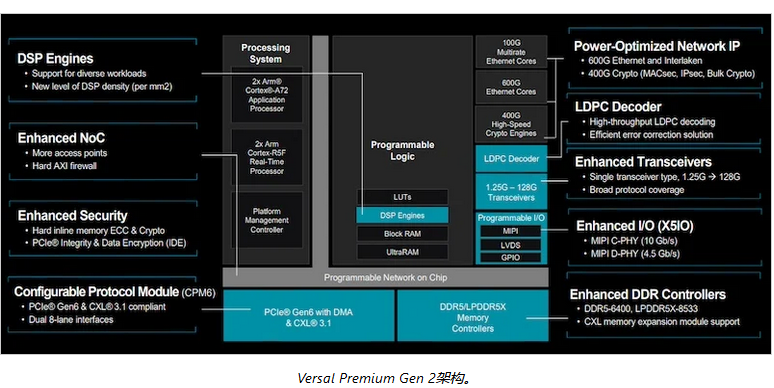

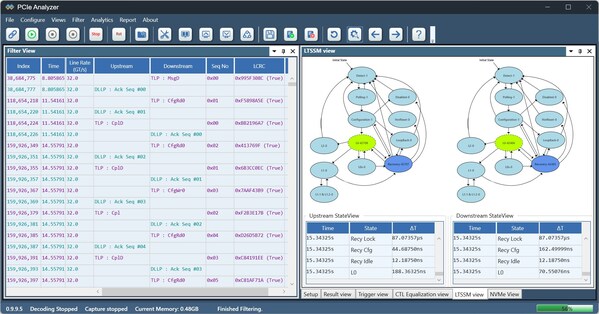

为此,Versal Premium系列Gen 2采用先进的互连技术,以满足AI系统中处理器和加速器之间的高速、低延迟数据移动。该解决方案支持CXL 3.1和PCIe Gen6,使其成为第一个集成这些最新行业标准的FPGA。

PCIe Gen 6提供每通道64千兆比特每秒(Gbps)的带宽,相当于前几代PCIe速度的2- 4倍。另一方面,CXL 3.1通过提供内存一致性和池化功能增强了主机到加速器的连接。CXL允许连接的加速器直接与CPU共享内存,减少冗余数据移动和延迟。通过结合PCIe Gen 6和CXL 3.1支持,AMD的Versal Premium Gen 2设备实现了双八通道接口,可支持高达256 Gbps的聚合带宽。

存储器架构

AMD还为Versal Premium Series Gen 2配备了复杂的内存架构,包括支持每秒8,533兆比特(Mbps)的LPDDR5X内存和6,400 Mbps的DDR5。与仍采用DDR4或LPDDR4标准的竞争设备相比,此配置可实现高达2.7倍的内存带宽。

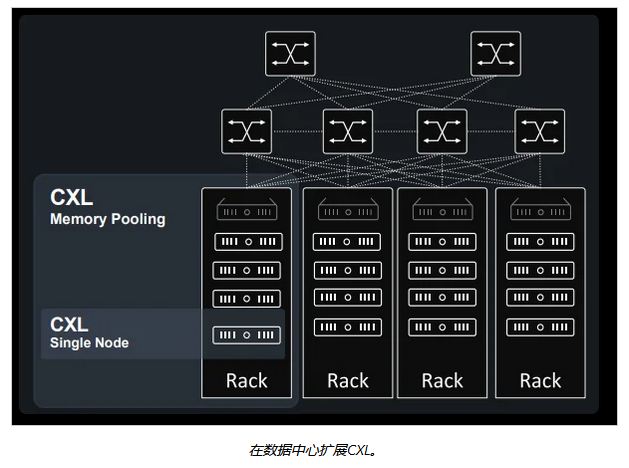

该FPGA还可以集成基于CXL的存储器扩展模块,以进一步增强其存储器的可扩展性。通过启用多主机、单逻辑设备配置,Versal Premium系列Gen 2可以在多个设备之间池化和动态分配内存,这是AI应用越来越需要的一项功能。

“通过CXL内存扩展,我们可以通过在多个设备上动态分配内存池来增加LPDDR 5X的带宽,”Rather说。此体系结构支持多头单逻辑器件(MH-SLD),无需开关,最终优化了内存利用率。

这些特性对于AI应用程序非常重要。CXL内存扩展减少了内存访问延迟,使AI核心能够快速访问更大的内存池。同时,高带宽接口使加速器能够更有效地处理和传输数据。此外,AMD的FPGA器件提供了DSP引擎,可以执行AI所需的数学运算,使它们足够灵活,可以在需要时处理一些推理任务。

加强了安保

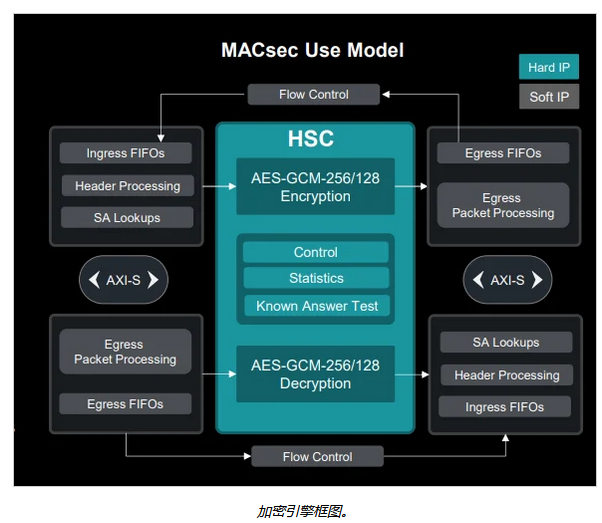

着眼于数据安全,Versal Premium系列Gen 2集成了一套旨在保护传输和静态数据的功能。

它包括集成的PCIe完整性和数据加密(IDE),用于安全的数据传输,沿着DDR内存的内联加密,用于跨数据流的端到端保护。AMD集成了两个400-G高速加密引擎,可加速加密和解密,使吞吐量比上一代产品提高一倍。这些引擎支持高达800 Gbps的数据保护,为实时应用提供了额外的安全层。

时间轴和开发工具

AMD为数据中心、航空航天、通信以及测试和测量市场设计了Versal Premium系列Gen 2。该公司计划在2025年下半年发布Versal Premium Series Gen 2的开发工具,预计在2026年初推出硅样品,并在2026年中期推出生产单元。

“如果你考虑整个人工智能时代,数据就像原油。数据越多,你能做的就越多,”Rather总结道。这正是我们对内存和高速数据传输需求的驱动力,推动我们在连接和处理能力的各个层面进行创新。”

审核编辑 黄宇

-

FPGA

+关注

关注

1634文章

21832浏览量

608115 -

amd

+关注

关注

25文章

5516浏览量

134986 -

PCIe

+关注

关注

15文章

1281浏览量

83632

发布评论请先 登录

相关推荐

ASW3410 USB3.1高速数据开关切换规格书

澜起科技推出PCIe 6.x/CXL 3.x Retimer芯片

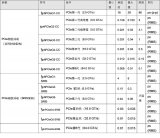

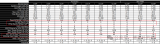

第二代AMD Versal Premium系列产品亮点

韩国无晶圆厂初创公司Panmnesia展示第一个支持CXL的AI集群

拓展AI数据中心内存,第二代AMD Versal Premium系列自适应SoC,首发支持CXL 3.1、 PCIe Gen6

AMD推出第二代Versal Premium系列

Xilinx 7系列FPGA PCIe Gen3的应用接口及特性

美光研发出世界首款PCIe Gen6 SSD

是德科技推出PCIe和UCIe仿真解决方案

Prodigy Technovations推出功能强大的PCIe Gen5协议分析仪

AMD Versal™ Adaptive SoC CPM PCIE PIO EP设计CED示例

HighPoint发布商用PCIe Gen5解决方案,最大可达960TB SSD容量

核芯互联发布支持PCIe Gen 6的时钟发生器芯片CLG0841/CLG0851

Achronix的FPGA有哪方面的优势?

AMD推出了Versal Premium Series Gen 2,这是业界第一个支持CXL 3.1和PCIe Gen6的FPGA平台。

AMD推出了Versal Premium Series Gen 2,这是业界第一个支持CXL 3.1和PCIe Gen6的FPGA平台。

评论