人工智能 (AI) 半导体和封装技术正在快速发展,这得益于 AI 和高性能计算 (HPC) 应用的高性能和复杂需求。随着 AI 模型的计算量越来越大,传统的半导体封装方法难以满足实现最佳 AI 功能所必需的效率、散热和信号完整性要求。先进的半导体封装技术旨在通过提高功率效率、带宽和小型化来应对这些挑战。

以下是该领域主要趋势和技术的细分:

异构集成:异构集成允许将多种类型的半导体(通常采用不同的工艺技术制造)集成到单个封装中,从而增强计算能力和效率。这种方法在 AI 应用中至关重要,其中 CPU、GPU 和 AI 加速器协同工作,每个都针对特定任务进行了优化。通过堆叠或并排放置这些组件,异构集成可显著提高 AI 任务的计算速度和能效。

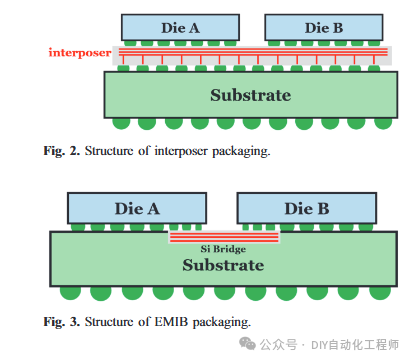

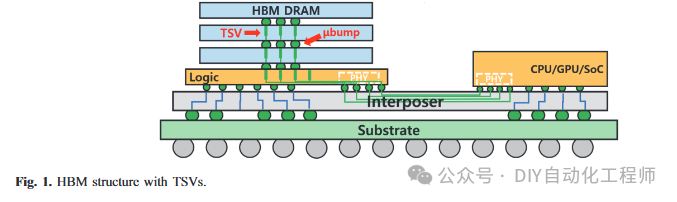

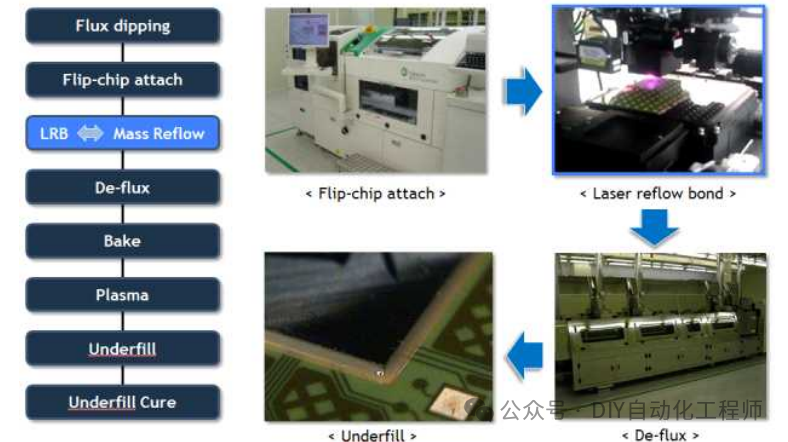

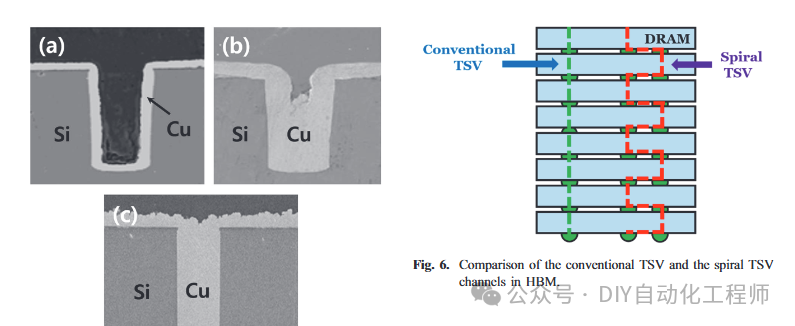

3D 集成和硅通孔 (TSV):硅通孔 (TSV) 是一种用于 3D 集成的方法,其中垂直连接穿过硅晶圆或芯片。该技术缩短了层间互连距离,从而降低了延迟和功耗。在 AI 中,TSV 可实现内存和处理单元之间的高带宽连接,这对于实时数据处理至关重要。通过 TSV 进行的 3D 集成还有助于小型化,这对于边缘计算模块和嵌入式多芯片互连桥 (EMIB)** 等紧凑型 AI 设备至关重要:中介层是先进封装的一个重要方面,它提供了一个放置多个芯片的基础层,并通过精细的布线将它们连接起来。这种结构允许高数据传输速率和组件之间的可靠连接。英特尔的嵌入式多芯片互连桥 (EMIB) 是这种方法的一种变体,它仅在需要时使用较小的中介层式桥,为复杂的 AI 半导体设计提供了有效的解决方案。中介层和EMIB技术增强了内存和计算核心的性能,使AI应用能够更快地处理数据密集型任务。

混合键合:结合了传统的铜-铜和氧化物-氧化物键合,可在芯片之间创建高度可靠、低功耗的连接。在AI应用中,这种键合方法可以实现紧密的芯片集成,从而提高速度并降低功耗。混合键合可用于内存和逻辑组件的3D堆叠,减少占用空间并提高数据传输速率,这对于需要高速数据移动的AI任务至关重要。

系统级封装:(SiP)技术将多个组件(如内存、逻辑和通信模块)封装在一个封装中。在AI和HPC应用中,SiP允许组合不同的技术,这些技术可以针对特定任务进行优化,从而减少延迟并提高能源效率。这种模块化方法正在获得关注,尤其是在空间有限但处理能力仍然至关重要的AI边缘计算中。

扇出型晶圆级封装:扇出型晶圆级封装 (FOWLP) 扩展了晶圆以允许更多互连,从而提供高性能和更小的占用空间。与传统封装方法相比,该技术在 AI 半导体封装中具有优势,因为它支持更高的 I/O 密度、更好的热性能和功率效率。FOWLP 正被用于 AI 加速器和处理器,其中高密度互连和散热对于处理 AI 的密集处理需求是必不可少的。

未来发展方向:AI 半导体封装技术面临着散热、功率效率和生产复杂性等挑战。集成这些先进的封装技术需要克服产量管理、生产可扩展性和成本方面的问题。然而,随着对高性能、低功耗 AI 芯片的需求不断增长,旨在克服这些障碍的投资和研究也在不断增长。未来趋势表明,多芯片集成、先进互连和混合键合技术将继续改进,以支持 AI 不断变化的需求。

人工智能驱动的半导体和封装技术进步有助于满足下一代人工智能和高性能计算系统对高数据传输、处理能力和效率的需求。随着封装技术的发展,它们将在提高人工智能硬件的计算效率、可靠性和可扩展性方面发挥重要作用,最终支持人工智能在各个行业的广泛发展和应用。

-

半导体

+关注

关注

335文章

27837浏览量

223942 -

人工智能

+关注

关注

1797文章

47890浏览量

240906 -

先进封装

+关注

关注

2文章

434浏览量

292

原文标题:人工智能半导体及先进封装技术发展趋势

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

先进封装成为AI时代的核心技术发展与创新

开关电源的最新技术发展趋势

《AI for Science:人工智能驱动科学创新》第一章人工智能驱动的科学创新学习心得

变阻器的未来发展趋势和前景如何?是否有替代品出现?

risc-v在人工智能图像处理应用前景分析

名单公布!【书籍评测活动NO.44】AI for Science:人工智能驱动科学创新

人工智能芯片先进封装技术

人工智能半导体及先进封装技术发展趋势

人工智能半导体及先进封装技术发展趋势

评论