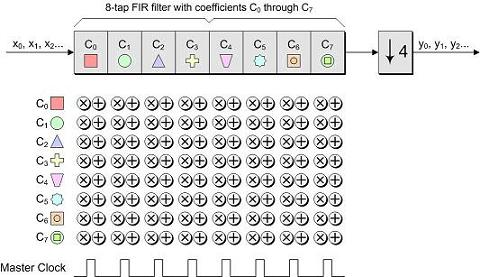

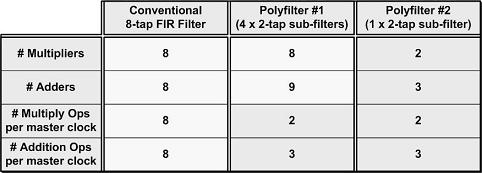

多相滤波器的基本概念是把FIR滤波器分割成若干较小的单元,然后组合这些单元的结果。首先,让我们考虑一个基于常规8抽头FIR滤波器的抽取子系统的符号表示,如图11所示(为了使用这些例子,我们假设抽取因子为M = 4 )。

图11 基于传统的8抽头FIR滤波器的抽取器的符号表示

现在让我们假设主时钟正在以某一频率fHz运行。像往常一样,在滤波操作之后任何不要的样本将被丢弃,但这样做是低效率的,因为这意味着是以完全的时钟频率在进行滤波。用另一种方式来看这种操作,即在每个时钟时刻,每个抽头级执行乘法和加运算。

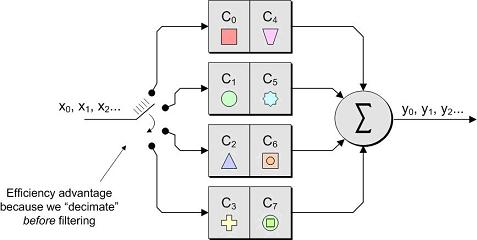

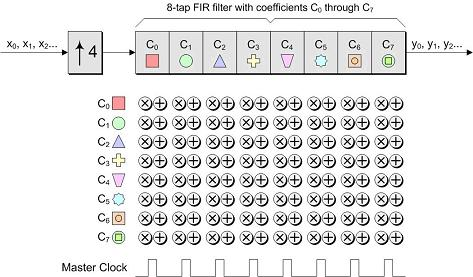

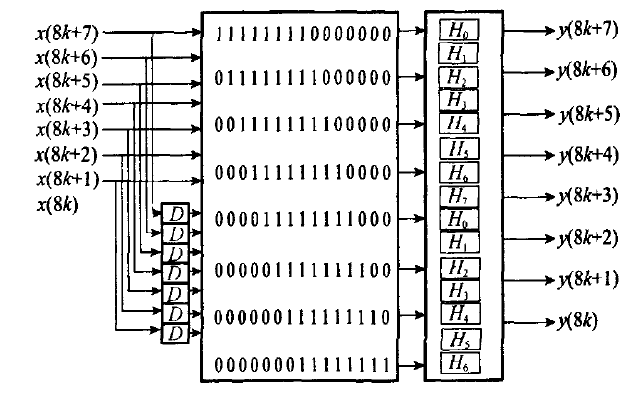

相比多相实现的情况,我们可以将原来的8抽头FIR滤波器分为四个2抽头子滤波器,如图12所示。

图12 基于4 × 2抽头多相滤波器的抽取器的符号表示

假设同样的主时钟以f Hz的频率运行,我们可以想象输入数据流被送入一个旋转开关(当然,这可用标准的逻辑技术来实现)。第一个数据值送入第一个子滤波器;第二个数据值送入第二个子滤波器;第三个数据值送入第三个子滤波器;第四个数据值送入第四个子滤波器。然后,我们进行“循环”操作,以便第五个数据值送入第一个子滤波器;第六个数据值送入第二个子滤波器;等等。

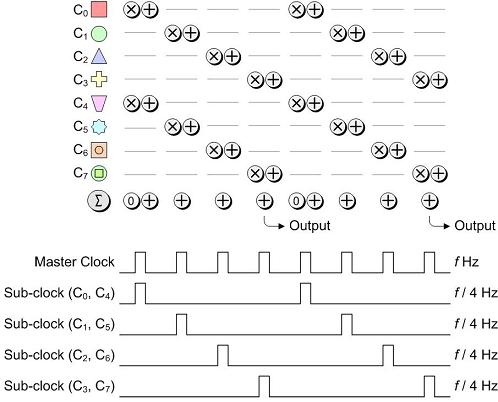

使用子滤波器减少了可能的饱和/溢出(发生任何饱和/溢出通常只需要在最后的函数求和时进行处理)。另外,使用子滤波器具有一个直接有效的优点,因为在执行滤波操作之前,我们有效地“抽取”了数据。这也意味着,我们的四个子滤波器中的每个都能有效地以F ÷ 4Hz的频率运行,如图13所示。

图13 4 × 2抽头多相滤波器的运行情况

除了任何寄存器和一般用途的逻辑,常规8抽头FIR滤波器中的每个抽头包含一个乘法器和一个加法器,当然为我们提供了总共8个乘法器和8个加法器。滤波器之后需要一些额外的逻辑,以便丢弃任何不想要的样本。

同样,在我们最初的4 × 2抽头多相实现中的每一个抽头含有一个乘法器和一个加法器,再次为我们提供了总共8个乘法器和8个加法器。在多相实现中,需要实现“旋转开关”送入滤波器的逻辑数量大约相当于在常规8抽头FIR滤波器中丢弃不要的样本所需的逻辑。

当然,多相实现还需要一些额外的逻辑和一个加法器累加来自四个子滤波器的结果。因此,最终的结果是,最初的多相实现需要比传统的8抽头FIR滤波器更多一点的逻辑。

然而,对于传统的8位FIR滤波器,在每个时钟都要执行8次乘和8次加。相比最初的多相实现的情况,在任何主时钟时刻,只有一个子滤波器是工作的。由于在这个例子中每个子滤波器含有两个抽头,这意味着这个功能的滤波器部分在每个时钟只进行两次乘法和两次加法。

当然,从四个子滤波器收集结果的求和功能还必须在每个主时钟进行加(在每4时钟周期开始时,这个累加器清零;它从四个子滤波器收集结果; 在每4时钟周期结束时,它产生一个新的值)。

这意味着,最初的多相实现的每个子滤波器有效地以常规8抽头FIR滤波器1/ 4的频率运行。反过来,这意味着最初多相实现只在每个主时钟进行两次乘法和三次加法(包括加法器的加操作),从而大大节省了功耗。

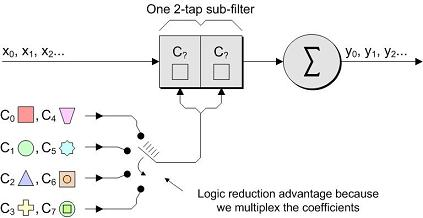

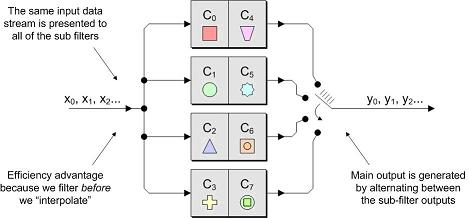

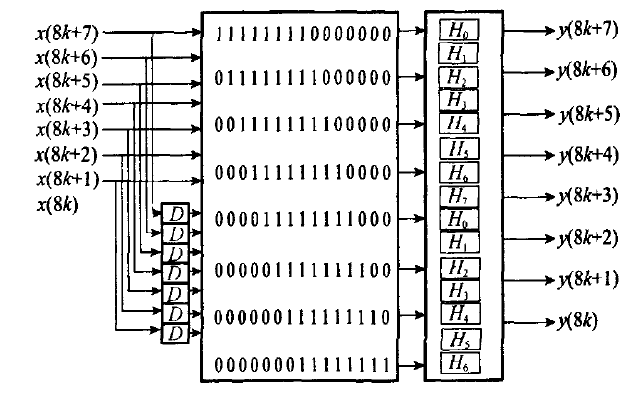

此外,在最初的多相实现中,由于四个子滤波器的每个只用了1/4的时间,这意味着在任何特定时间,我们实际上只需要其中的一个,这使我们更加完善了实现方法,如图14所示。

图14 更完善的基于多相滤波器的抽取器实现方案

在这种情况下,我们采用了单一的2抽头子滤波器,每个抽头含有乘法器和加法器。在每个主时钟,我们选择合适的系数对。每一个抽头需要额外的寄存器和用于维护的逻辑,但与减少的乘法器和加法器相比,与我们的最初多相实现相比,这是微不足道的。

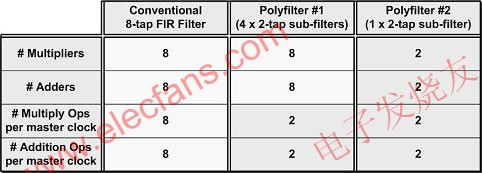

当然,在我们原来的多相实现中,我们仍然要在每个主时钟时刻执行两次乘法和三次加法,。这些抽取实现例子的总结如表1所示。

表1抽取实现实例的总结

利用多相FIR滤波器进行内插

现在让我们来考虑内插的情况。首先让我们先考虑一个基于常规8抽头FIR滤波器的内插子系统的符号表示,如图15所示。

图15传统的基于8抽头FIR滤波器的内插器的符号表示

针对这些例子的用途,我们假设内插因子为L = 4,主时钟频率为FHz。正如先前所讨论的,向上采样(插入零值样本的过程)发生在滤波操作之前。

现在让我们来考虑一个最初的多相实现,我们原来的8抽头FIR滤波器被分成四个2 抽头子滤波器,如图16所示。

图16 基于4 × 2抽头多相滤波器的内插器的符号表示

在这种情况下,相同的输入数据流面向所有的四个子滤波器,在子滤波器输出之间轮流产生主输出数据流。最终的结果是,多相实现含有如同我们的常规8抽头FIR滤波器相同数量的乘法器和加法器。然而,因为在内插之前进行了滤波,子滤波器只需要以1 / 4的主时钟频率运行,从而大大节省了功耗(这里主时钟用于子滤波器输出之间的采样)。

此外,多相实现不需要向上采样(零值插入)的逻辑。当然,我们可以用完全运行于主时钟频率和复用系数的单个2抽头子滤波器取代原来的多相滤波器实现。

内插实现的这些例子的总结见表2 。

表2内插实现实例的总结

总结

所有这一切都意味着,多相基于滤波器的抽取器、内插器和重采样功能是非常适合用更小的中档FPGA来实现,如Lattice半导体公司的拥有SERDES功能的LatticeECP3系列,它具有高性能的sysDSP模块。它的特点是有dual-slice结构,具有级联/链接DSP slice和模块的功能,增强的DSP指令集使LatticeECP3系列能够引人注目地用于范围广泛的数字信号处理的应用,包括那些需要传统的FIR和基于多相的滤波功能。

-

FPGA

+关注

关注

1629文章

21748浏览量

603814 -

滤波器

+关注

关注

161文章

7833浏览量

178233 -

多相滤波

+关注

关注

0文章

10浏览量

10318

原文标题:FPGA进行多路并行插值滤波(多相滤波)的实现原理

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于DSP Builder的CIC梳状滤波器该怎么设计?

如何设计基于中档FPGA多相滤波器?

基于FPGA的多相滤波实现

如何使用FPGA实现实现高速并行FIR滤波器

如何使用FPGA实现实现高速并行FIR滤波器

如何使用FPGA实现图像的中值滤波算法

FPGA进行多路并行插值滤波(多相滤波)的实现原理

FPGA进行多路并行插值滤波(多相滤波)的实现原理

评论