一、主时钟create_clock

1.1 定义

主时钟是来自FPGA芯片外部的时钟,通过时钟输入端口或高速收发器GT的输出引脚进入FPGA内部。对于赛灵思7系列的器件,主时钟必须手动定义到GT的输出,对于Ultrascale和Ultrascale+系列的器件,定时器会自动地接入到GT的输出。

1.2 约束设置格式

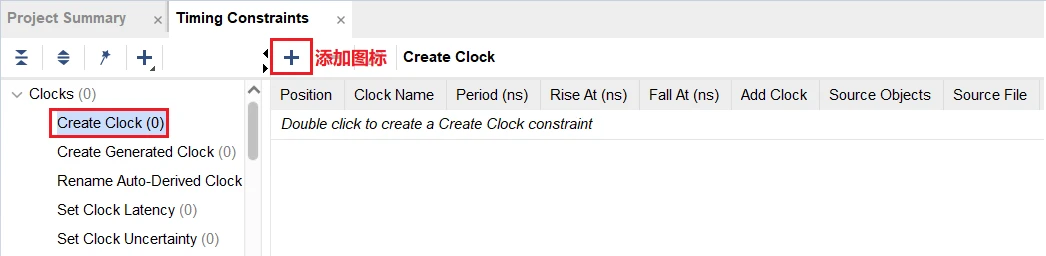

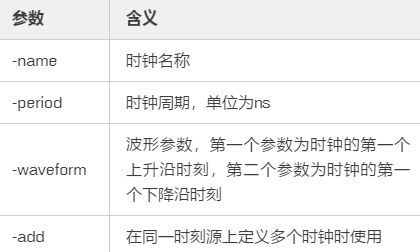

主时钟约束使用命令create_clock进行创建,进入Timing Constraints窗口,clocks选择Create Clock,单击添加图标或双击Create Clock,进入创建窗口

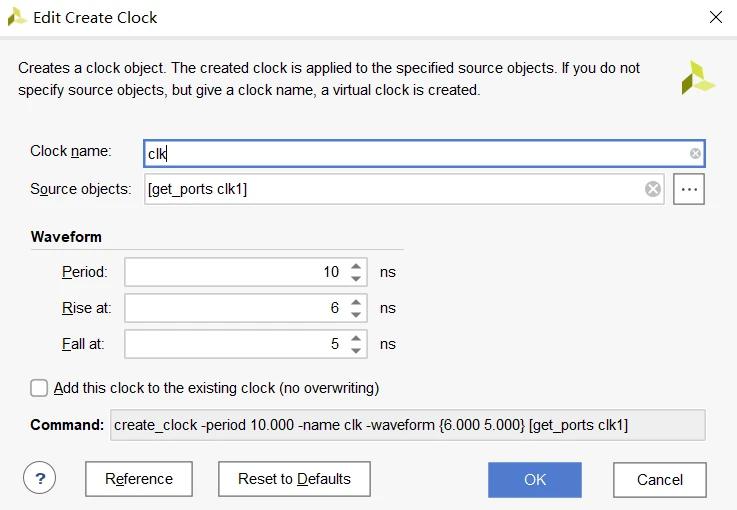

Create Clock窗口中,Clock name为时钟约束命名,Source objects设置约束的对象类型,可以是ports,nets,pin,Waveform设置波形的形状,Period为波形周期,Rise at设置时钟的上升沿位置,Fall at设置时钟的下降沿位置。command后面为根据上述的设置自动生成对应的约束命令。

1.3Add this clock to the existing clock

Add this clock to the existing clock勾选后,对于如果某个对象已创建时序约束,再次创建时将不会将之前的约束覆盖。

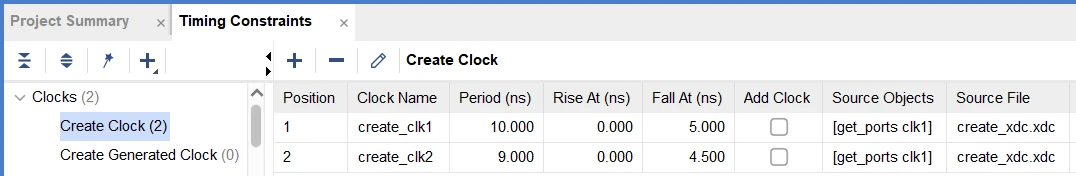

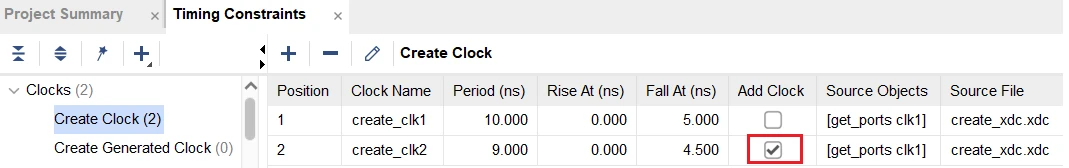

下面两条约束create_clk1和create_clk2的约束对象source objects都是clk1,约束内容不同,未勾选Add this clock to the existing clock时,约束如下

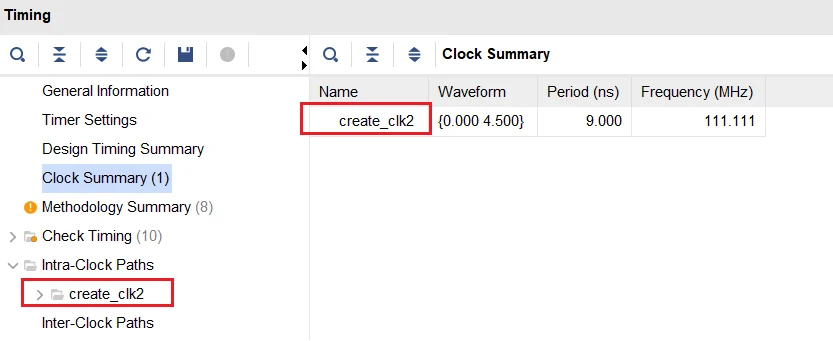

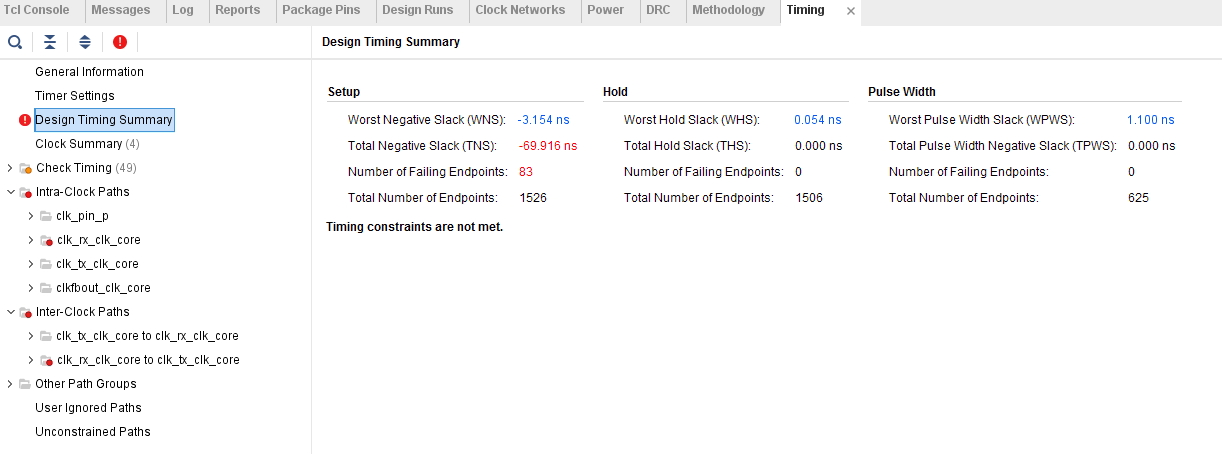

查看时序分析结果,只有create_clk2的信号,create_clk1已被覆盖

勾选Add this clock to the existing clock

时序分析报告中,create_clk1和create_clk2都存在

1.4 示例

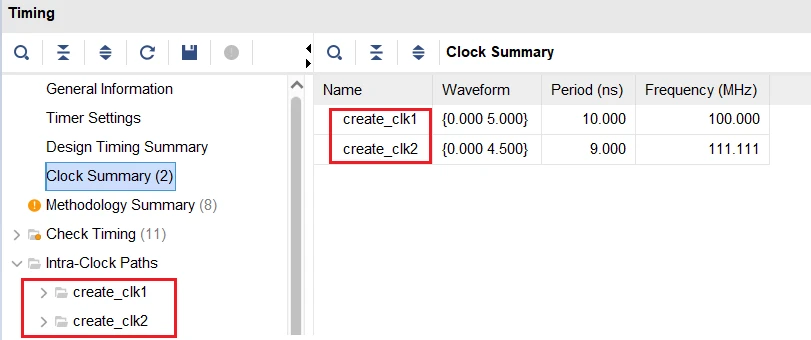

以时钟输入端口为例,时钟信号周期为10ns,占空比为50%,通过输入缓冲器和全局时钟缓冲器BUFG到达寄存器的时钟输入端口。

约束命令:create_clock -period 10 [get_ports sysclk]

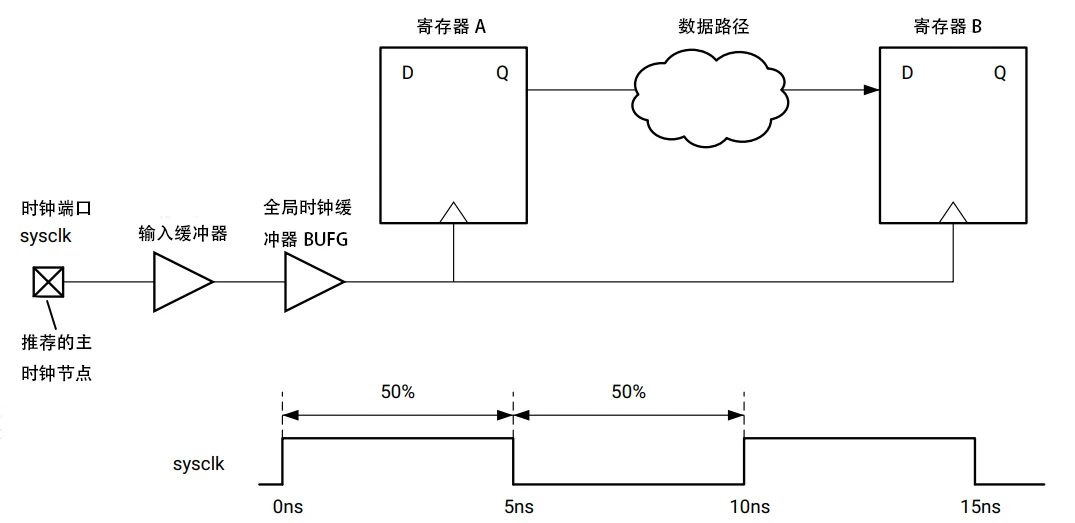

来自高速收发器GT的时钟rxclk,周期为3.33ns,50%的占空比,经过时钟管理单元MMCM,生成不同的分频时钟信号,分频时钟信号再传输到寄存器。

约束命令:create_clock -name rxclk -period 3.33 [get_pins gt0/RXOUTCLK]

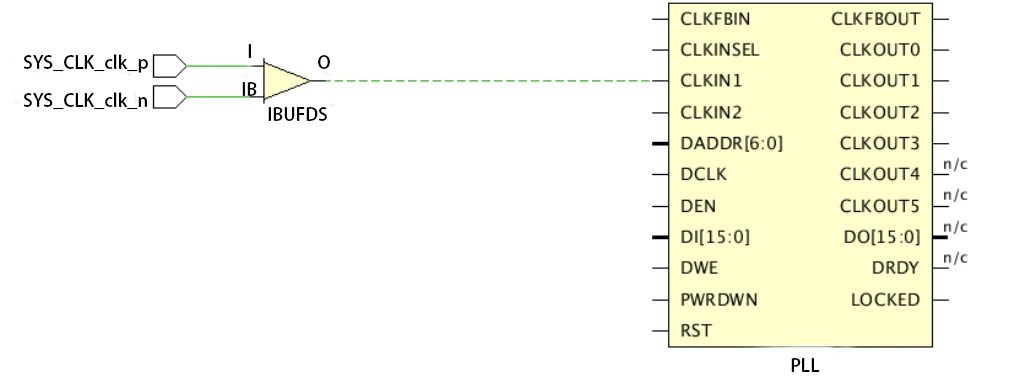

1.5 差分信号

约束命令:create_clock -name sysclk -period 3.33 [get_ports SYS_CLK_clk_p]

差分信号作为主时钟输入时,以一个差分信号输入到PLL的时钟输入端口CLKIN1为例,主时钟必须约束到差分端口的输入正极(sys_clk_clk_p)

二、生成时钟generate_clock

2.1 定义

生成时钟通常来源于设计内部的时钟管理单元,如MMCM,PLL等,生成时钟是与主时钟相关,其来源来自主时钟或其他生成时钟。因此,需先定义主时钟,再定义生成时钟。优点是主时钟变化时会同步进行变化。

生成时钟与主时钟关系可以是分频,倍频,非整数倍频率,相移,占空比切换,以及上述关系的组合。

2.2 格式

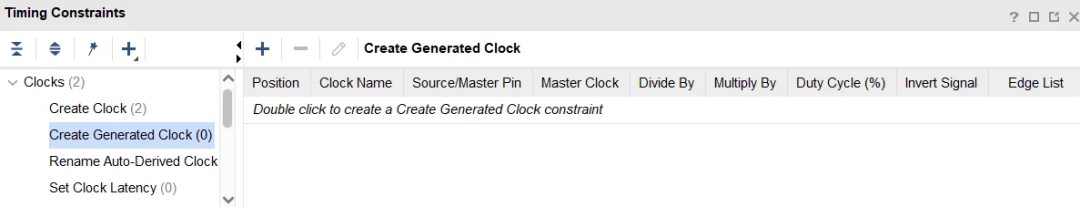

在Timing Constraints中,左侧选择Create Generated Clock,

在Create Generated Clock可以看到生成时钟的相关参数设置

clock name: 设置生成时钟的名称

Master pin(source):设置生成时钟的来源,可以是IO ports或cells pin

Master clock:设置生成时钟的源时钟

Source objects:指定指定生成时钟的实际对象,可以是I/O ports,cell pins或nets.

Do not override clocks already defined on the same Source object:勾选后,如果Source objects上有其他时钟约束,将不会被覆盖,不勾选,则覆盖原先的约束信息

Derive from source clock waveform:设置生成时钟波形与源时钟的关系,有频率相关和边沿相关两种方式,见2.2.1和2.2.2

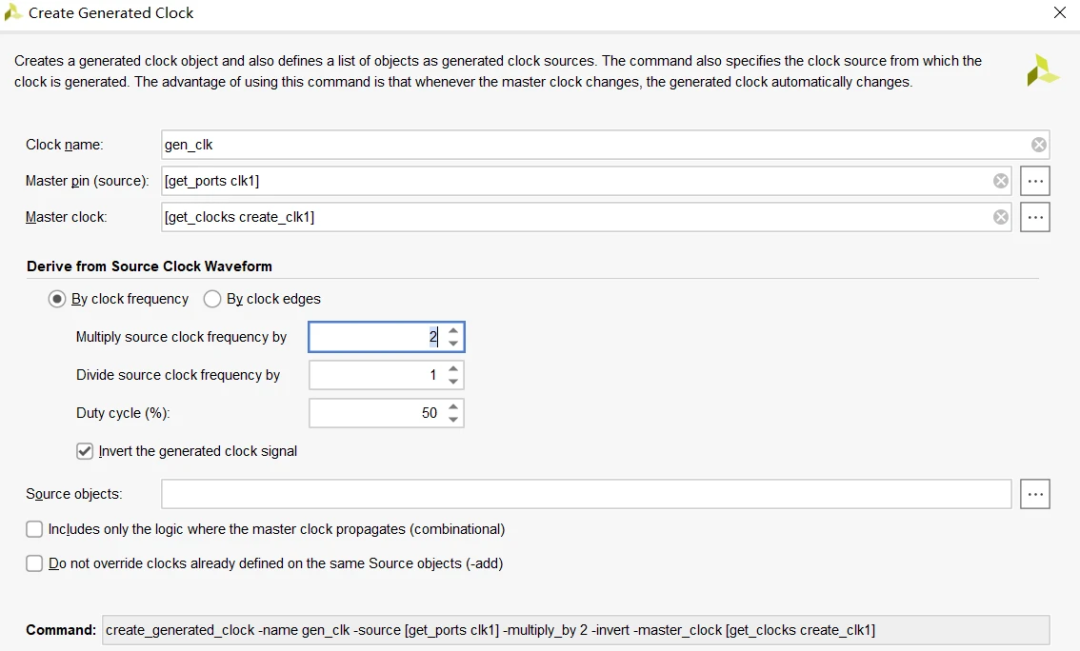

2.2.1 by clock frequency

Multiply source clock frequency by:生成时钟是源时钟的倍频关系,值大于或等于1

Divide source clock frequency by:生成时钟是源时钟的分频关系,值大于或等于1

Duty cycle:设置生成时钟的占空比

Invert the generated clock signal:勾选后对生成信号进行倒置,即高低电平互换,0变1,1变0

下图设置的命令为:create_generated_clock -name gen_clk -source [get_ports clk1] -multiply_by 2 -invert -master_clock [get_clocks create_clk1]

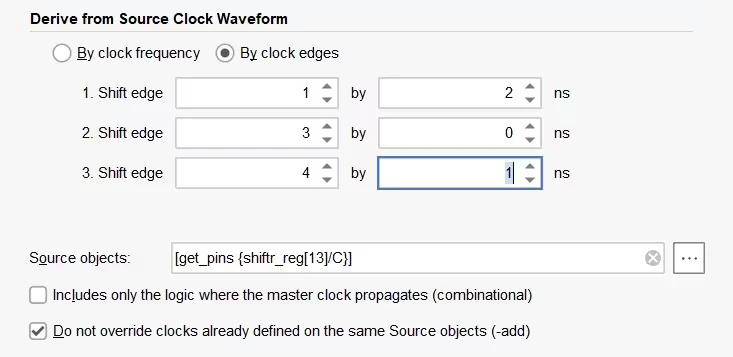

2.2.2by clock edges

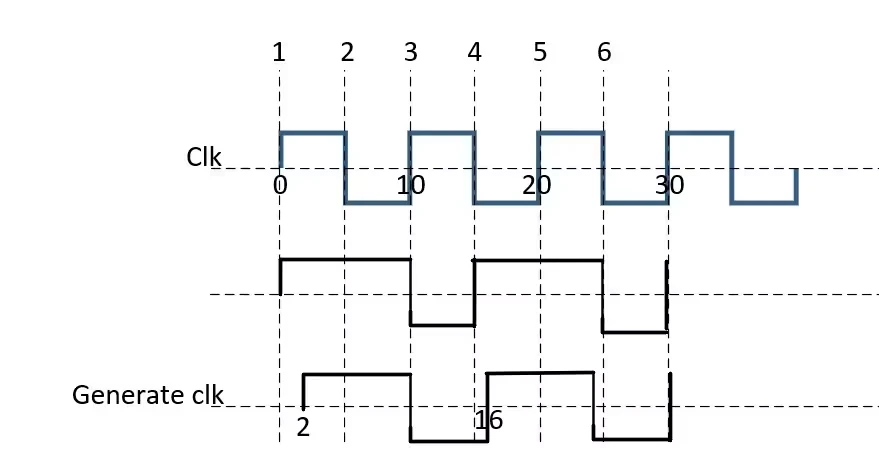

通过源时钟的边沿设置生成时钟,以下图为例。

对应的命令为create_generated_clock -name gen_clk -source [get_pins clk_IBUF_BUFG_inst/O] -edges {1 3 4} -edge_shift {2.0 0.0 1.0} -add -master_clock [get_clocks "*"] [get_pins {shiftr_reg[13]/C}]

含义解释:-edge {1,3,4}即生成时钟的第1个上升沿位置,第1个下降沿位置,第2个上升沿位置分别对应源时钟的第1,3,4个变化边沿,-edge_shift的3个值为在源时钟基础上的偏移。假设源时钟clk周期为10ns,占空比为50%,从0时刻开始,统计了边沿变化的数目,-edge {1,3,4}如中间波形所示,对应了clk第1,3,4的边沿;Generate clk即为各个边沿的偏移值,分别是0+2,10+0,15+1,即为Generate clk的波形。

2.2.3 示例

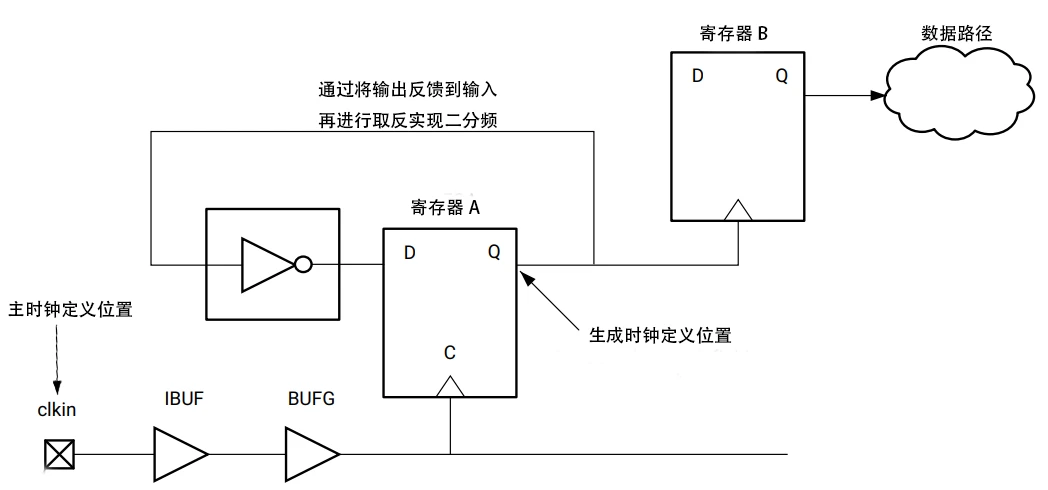

a)二分频的生成时钟实现用寄存器实现

主时钟周期为10ns,对应的约束命令为

create_clock -name clkin -period 10 [get_ports clkin] #创建主时钟 create_generated_clock -name clkdiv2 -source [get_ports clkin] -divide_by 2 [get_pins REGA/Q] #创建生成时钟

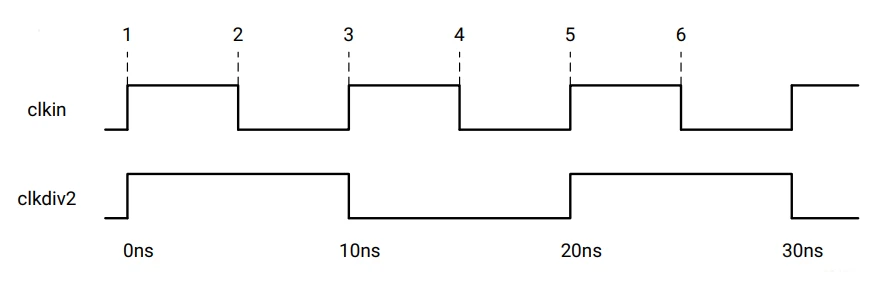

b)边沿生成时钟

时钟边沿设置生成时钟,对应命令为,由波形可看出生成时钟的3个边沿刚好对应主时钟的第1,3,5,因为无偏移,故不需要-edge_shift,

create_generated_clock -name clkdiv2 -source [get_pins REGA/C] -edges {1 3 5} [get_pins REGA/Q]

生成时钟的波形clkdiv2如下图所示

c)非整数倍频生成时钟

通过同时设置倍频和分频可以设置非整数倍的生成时钟频率,如果需要生成一个4/3倍频的生成时钟,先用倍频参数multiply_by 4,再用分频参数divide_by 3。

create_generated_clock -name clk43 -source [get_pins mmcm0/CLKIN] -multiply_by 4 -divide_by 3 [get_pins mmcm0/CLKOUT]

2.2.4 自动生成时钟

Vivado在某些场景下会根据已定义的主时钟自动产生生成时钟,将生成时钟约束到时钟修正块(CMB:clock modifying blocks)中,CMB可以是MMCM,PLL,BUFR等,在UltraScale器件中,还包括GT_COMMON/GT_CHANNEL/IBUFDS_GTE3,ISERDESE3,BITSLICE_CONTROL / RX*_BITSLICE。

如果用户在需自动产生生成时钟的网表对象中设置了约束,则不会产生生成时钟。自动产生的生成时钟是以定义位置连接net的最顶层的部分名来命名。

以下图连接示例,主时钟clkin驱动MMCM实例化为clkip/mmcm0的CLKIN,自动产生的生成时钟名称为cpuclk,约束到clkip/mmcm0/CLKOUT

2.2.5重命名生成时钟

对于自动生成的生成时钟,可以使用约束对其进行重命名,命令格式如下

new_name:重命名的名称

source_object:为自动生成时钟的源对象

source/master_clock:在源对象source_object存在其他时钟时,必须加上该参数,避免冲突或产生歧义

create_generated_clock -name new_name [-source master_pin] [-master_clock master_clk] source_object

并不是生成时钟都可以重命名,自动生成时钟重命名于来源的pin,例如MMCM/PLL的输出端口,不能重命名于BUFG的输出端口,并且用户定义的生成时钟不能重命名。

-

时序

+关注

关注

5文章

388浏览量

37346 -

主时钟

+关注

关注

0文章

8浏览量

6005

原文标题:时序约束一主时钟与生成时钟

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

错误时钟偏移计算导致错误时序收敛的解决方案

FPGA主时钟约束详解 Vivado添加时序约束方法

时序约束一主时钟与生成时钟

时序约束一主时钟与生成时钟

评论