来源:电子制造工艺技术

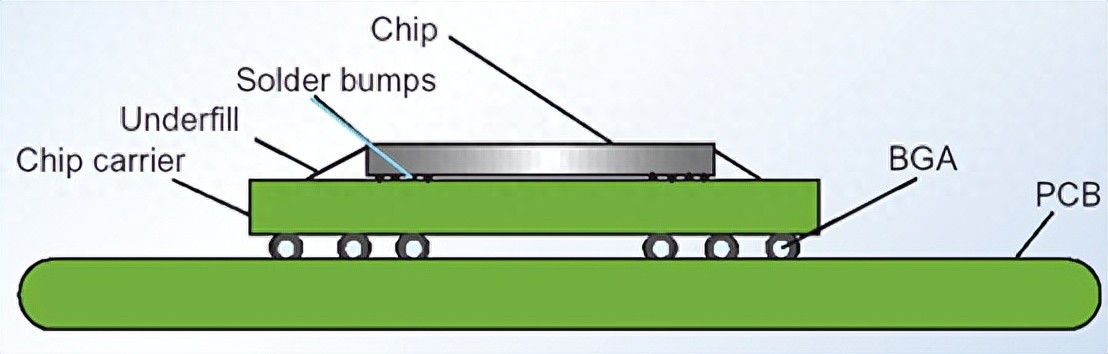

倒装芯片(Flip chip)是一种无引脚结构,一般含有电路单元。设计用于通过适当数量的位于其面上的锡球(导电性粘合剂所覆盖),在电气上和机械上连接于电路。

倒装芯片原理:Flip chip又称倒装片,是在I/O pad上沉积锡铅球,然后将芯片翻转加热利用熔融的锡铅球与陶瓷基板相结合此技术替换常规打线接合,逐渐成为未来的封装主流,当前主要应用于高时脉的CPU、GPU(Graphic Processor Unit)及Chipset 等产品为主。与COB相比,该封装形式的芯片结构和I/O端(锡球)方向朝下,由于I/O引出端分布于整个芯片表面,故在封装密度和处理速度上Flip chip已达到顶峰,特别是它可以采用类似SMT技术的手段来加工,因此是芯片封装技术及高密度安装的最终方向。

倒装片连接有三种主要类型C4(Controlled Collapse Chip Connection)、DCA(Direct chip attach)和FCAA(Flip Chip Adhesive Attachement)。但实际制造工艺分很多种如下:

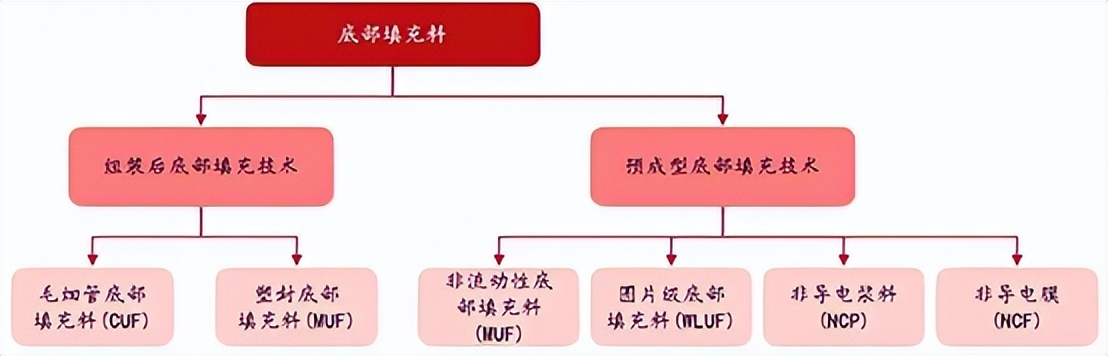

毛细管底部填充(CUF)技术依赖毛细作用将材料填充在芯片和芯片载体之间。首先,在带有凸点的基板上涂覆一层助焊剂,然后将芯片焊料凸点对准基板焊盘,加热使焊料回流,实现上下凸点的互连。

随后,通过溶剂喷雾等方式清洗助焊剂,然后沿着芯片边缘注入底部填充料。底部填充料借助毛细作用会被吸入芯片和基板的空隙内,最后进行加热固化。目前,市场上大部分底部填充料采用毛细管底部填充技术,广泛应用于手机等许多电子器件的小尺寸芯片封装中。

塑封底部填充(MUF)技术将底部填充料的填充和器件塑封两个步骤合二为一。在进行塑封的同时,底部填充料进入芯片和基板之间的空隙,在随后的固化过程中完成填充和密封。相较于毛细管底部填充工艺,塑封底部填充工艺(MUF)更为简便快速。

非流动底部填充料(NUF)工艺不依赖于液体的毛细作用。在芯片和基板互连之前,首先在基板表面涂覆非流动底部填充料,然后在焊料回流过程中同时完成焊球互连和底部填充料的加热固化。这一工艺省去了毛细管底部填充工艺中助焊剂的涂覆和清除步骤,提高了生产效率。晶片级底部填充料(WLUF)是针对晶片级封装而设计的填充方式。在晶圆上,通过适当的涂覆工艺(如层压或涂覆)添加一层底部填充料,并对其进行加热以去除溶剂以进行预固化。随后,通过平整化处理露出互连凸点,然后对晶圆进行切割,以获得带有凸点的单个组件。最后,这些组件通过表面安装工艺与基板连接起来。

非导电浆料(NCP)工艺可以通过热压的方式直接让凸点和焊盘接触,实现电互连,省去了与助焊剂相关的步骤。该材料在固化后主要用于形成机械连接,并维持凸点和焊盘的接触压力。

非导电膜(NCF)材料具有柔软性,可作为卷材夹在塑料薄膜(如PET)中使用,适用于圆片级封装。NUF与NCP/NCF有所不同,NUF的非流动性在焊料回流过程中同时实现封装材料和助焊剂等与焊球的互连。而NCP/NCF是一种非导电材料(膜),通过倒装键合的热压方式完成焊球的互连和封装材料的固化过程。

倒装芯片的主要工艺步骤包括:底部金属层UBM(Under Bump Metallurgy),凸点制作(Bumping),互连(Interconnection),底部填充(Underfilling)和固化(Curing)

总结:倒装芯片在产品成本,性能及满足高密度封装等方面 体现出优势,它的应用也渐渐成为主流。由于倒装芯片的 尺寸小,要保证高精度高产量高重复性,这给我们传统的设备及工艺带来了挑战,具体表现在以下几个方面:

1.基板(硬板或软板)的设计方面;

2.组装及检查设备方面;

3.制造工艺 ,芯片的植球工艺, PCB 的制造工艺,SMT 工艺;

4.材料的兼容性图11 助焊剂浸蘸工艺

全面了解以上问题是成功进行倒装芯片组装工艺的基础

倒装芯片算先进封装吗?倒装芯片可以算得上半个先进封装,一只脚踩在先进封装的门里,一只在门外,算是传统封装与先进封装的过渡产物。与当今的2.5D/3D IC封装相比,倒装芯片仍是2D封装,并不能垂直堆叠。但是与wire bonding相比又具有极大的优势。倒装芯片有哪些封装形式?FCBGA,FCCSP。

未来倒装芯片技术发展:

近年来,随着半导体技术的不断发展,芯片的处理性能运算能力提升得越来越快。以及2.5D与3.5D等3D异构芯片的普及,正装与倒装及键合技术将会打破原有秩序,进行重新组合与融合,形成新的3D立体异构芯片智能制造工艺技术。如下图

文章来源于网络整理

声明:本网站部分文章转载自网络,转发仅为更大范围传播。 转载文章版权归原作者所有,如有异议,请联系我们修改或删除。联系邮箱:viviz@actintl.com.hk, 电话:0755-25988573

审核编辑 黄宇

-

倒装芯片

+关注

关注

1文章

124浏览量

16868 -

Flip

+关注

关注

0文章

11浏览量

10131 -

先进封装

+关注

关注

2文章

561浏览量

1057

发布评论请先 登录

AI时代算力瓶颈如何破?先进封装成半导体行业竞争新高地

CoWoS(Chip-on-Wafer-on-Substrate)先进封装工艺的材料全景图及国产替代进展

芯片封装:Wire Bond与Flip Chip并非代际关系

对话飞凯材料 | 锚定先进封装核心赛道,支撑AI算力增长

半导体“倒装芯片(Flip - Chip)”焊界面退化的详解;

Flip Chip水溶性助焊膏:高良率 · 低空洞 · 易清洗 · 适用于先进封装

FCCSP驱动下的半导体封装新格局

未来半导体先进封装PSPI发展技术路线趋势解析

聊聊倒装芯片凸点(Bump)制作的发展史

倒装芯片(flip chip)算先进封装吗?未来发展怎么样?

倒装芯片(flip chip)算先进封装吗?未来发展怎么样?

评论