本文介绍了SiO2薄膜的刻蚀机理。

干法刻蚀SiO2的化学方程式怎么写?刻蚀的过程是怎么样的?干法刻氧化硅的化学方程式?

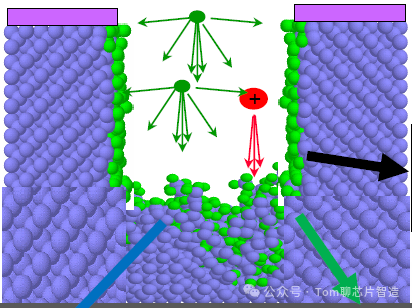

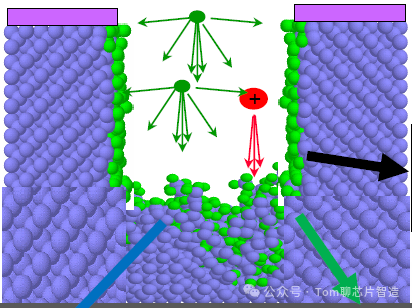

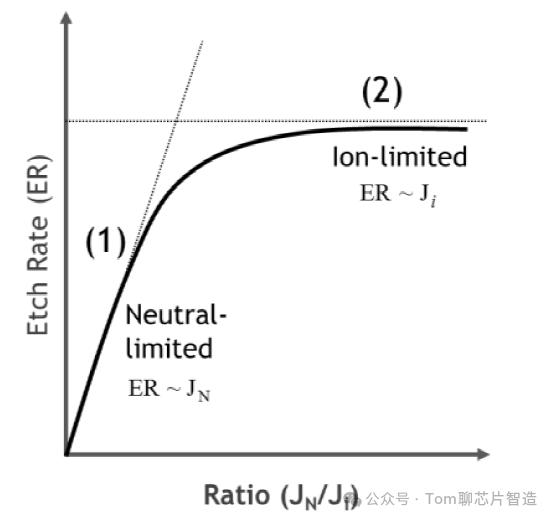

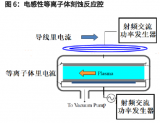

如上图,以F系气体刻蚀为例,反应的方程式为: SiO2(s)+ CxFy +Ar(+)>SiF4 (g)+ CO(g) CxFy是来自刻蚀气体(如CF₄、CHF₃)解离产生的氟自由基,用于氧化硅的化学刻蚀。 Ar(+)是被加速的高能离子,起到物理轰击的作用。 SiF4 :四氟化硅,气相形式的挥发性产物。 CO:一氧化碳,副产物。 红色箭头代表离子轰击,高能离子轰击表面,破坏SiO₂分子的键,为自由基提供更多反应位点,同时起到“方向性”作用,使刻蚀更具各向异性。 绿色箭头代表氟自由基,即CxFy。Ar离子轰击与化学刻蚀的结合,才能显著提高刻蚀速率。单一的物理或化学机制均不足以实现高效刻蚀。 离子与中性粒子比值对反应速率的影响

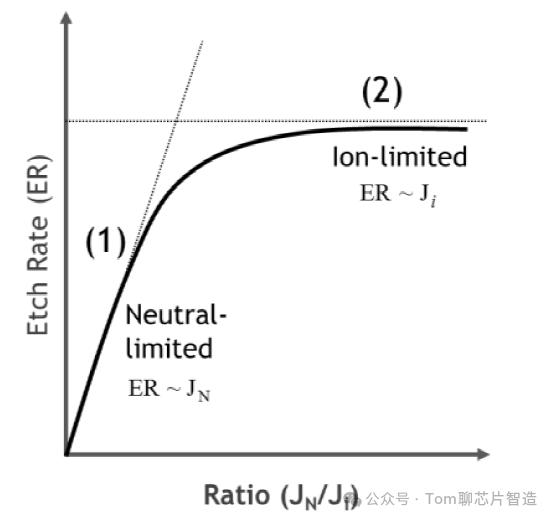

如上图: 中性粒子(自由基)浓度:Ar(+)浓度:当比值较低时,刻蚀速率主要受自由基的浓度限制。在高比值时,Ar离子轰击成为限制因素,刻蚀速率趋于饱和。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

原文标题:SiO2薄膜的刻蚀机理

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

相关推荐

等离子体刻蚀和湿法刻蚀是集成电路制造过程中常用的两种刻蚀方法,虽然它们都可以用来去除晶圆表面的材料,但它们的原理、过程、优缺点及适用范围都有很大的不同。 1. 刻蚀原理和机制的

![的头像]() 发表于

发表于 01-02 14:03

•212次阅读

芯片湿法刻蚀方法主要包括各向同性刻蚀和各向异性刻蚀。为了让大家更好了解这两种方法,我们下面准备了详细的介绍,大家可以一起来看看。 各向同性刻蚀 定义:各向同性

![的头像]() 发表于

发表于 12-26 13:09

•146次阅读

、湿法刻蚀过程中,使用的化学溶液与待刻蚀的晶圆材料发生化学反应,将固体材料转化为可溶于水的化合物。这种化学反应需要高选择性的化学物质,以确保只有需要去除的部分被刻蚀,而其他部分保持不变。 2

![的头像]() 发表于

发表于 12-23 14:02

•225次阅读

一层原子。 ALE的刻蚀原理 如上图,是用Cl2刻蚀Si的ALE反应示意图。 第一步:向工艺腔中通入刻蚀气体Cl2,Cl

![的头像]() 发表于

发表于 12-20 14:15

•200次阅读

。 腔室压力由什么决定的? 1,气体流量越高,压力越大。 2,真空泵排气,泵速越高,腔室压力越低。 腔室压力对于刻蚀的影响 1,离子轰击能量。低压力,分子平均自由程大,离子的碰撞几率小,能量耗散少,故能量高。 2,离子与自由基的

![的头像]() 发表于

发表于 12-17 18:11

•208次阅读

说到湿法刻蚀了,这个是专业的技术。我们也得用专业的内容才能给大家讲解。听到这个工艺的话,最专业的一定就是讲述湿法刻蚀步骤。你知道其中都有哪些步骤吗?如果想要了解,今天是一个不错的机会,我们一起学习

![的头像]() 发表于

发表于 12-13 14:08

•160次阅读

本文介绍了刻蚀工艺参数有哪些。 刻蚀是芯片制造中一个至关重要的步骤,用于在硅片上形成微小的电路结构。它通过化学或物理方法去除材料层,以达到特定的设计要求。本文将介绍几种关键的刻蚀参数,包括不完全

![的头像]() 发表于

发表于 12-05 16:03

•569次阅读

:晶圆表面不同区域的温度由于加热器分布不均可能会有差异,导致局部区域刻蚀速率不同,从而影响刻蚀均匀性。 2,气体:气体化学组成,气体比例,气体流量 气体化学组成:干法刻蚀的腔室中可以选

![的头像]() 发表于

发表于 12-02 09:56

•474次阅读

PDMS(聚二甲基硅氧烷)是一种常见的弹性体材料,广泛应用于微流控芯片、生物传感器和柔性电子等领域。在这些应用中,刻蚀工艺是实现微结构加工的关键步骤。湿法刻蚀和软刻蚀是两种常用的刻蚀方

![的头像]() 发表于

发表于 09-27 14:46

•256次阅读

SiO₂薄膜在集成电路中扮演着至关重要的角色,其作用主要包括以下几个方面: 绝缘层 :SiO₂薄膜作为良好的绝缘材料,被广泛应用于集成电路中作为绝缘层。它能够有效地隔离金属互连线和晶体

![的头像]() 发表于

发表于 09-27 10:19

•1163次阅读

SiO₂薄膜的厚度量测原理主要基于光的干涉现象。具体来说,当单色光垂直照射到SiO₂薄膜表面时,光波会在薄膜表面以及

![的头像]() 发表于

发表于 09-27 10:13

•477次阅读

SiO₂膜层镀膜过程中出现的膜裂问题,可以通过多种方法来解决。以下是一些主要的解决策略: 1. 优化镀膜工艺 蒸发速度控制 :蒸发速度的设置对膜层厚度有直接的影响,进而影响膜层的应力和均匀性。需要

![的头像]() 发表于

发表于 09-27 10:08

•690次阅读

刻蚀可以分为湿法刻蚀和干法刻蚀。湿法刻蚀各向异性较差,侧壁容易产生横向刻蚀造成刻蚀偏差,通常用于

![的头像]() 发表于

发表于 04-12 11:41

•5134次阅读

刻蚀过程中形成几乎完全垂直于晶圆表面的侧壁,是一种各向异性的刻蚀。刻蚀后的侧壁非常垂直,底部平坦。这是理想的刻蚀形态,它能够非常精确地复制掩膜上的图案。

发表于 03-27 10:49

•721次阅读

HS-DR-5瞬态平面热源法热导热系数测试仪的核心部件就是超薄膜式探头,探头的材料是由刻蚀后的电热金属镍丝,其结构是由多圈双螺旋构成,同时做为加热和传感器,探头用聚酰亚胺薄膜封装,一方面可以防止电热

![的头像]() 发表于

发表于 03-13 10:06

•273次阅读

SiO2薄膜的刻蚀机理

SiO2薄膜的刻蚀机理

评论