AMD Vitis Networking P4 工具 ( VNP4 ) 是一种高级设计环境,针对 FPGA 和自适应 SoC 的包处理数据平面,可实现简化设计的效果。它能够将用 P4 编写的设计转换为设备就绪的 RTL 代码,以实现最佳的硬件实现。使用 VNP4,您可以显著减少开发基于设备的数据包处理系统所需的工程工作量,同时仍能实现每 LUT 或每 RAM 的高性能。本白皮书概述了使用 VNP4 进行设计的优点。

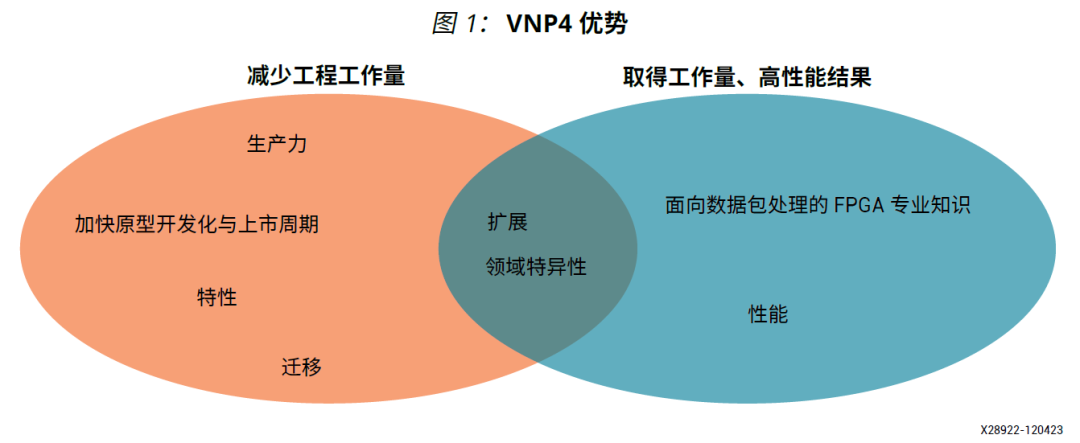

VNP4 的优势大致可分为两类:减少工程工作量和取得高质量、高性能结果。

1

生产力:解决方案可以减少开发工作量。

2

加快原型开发与上市周期:加快设计周期有助于您的产品更早上市。实现多个设计选项的迭代更为简便、快速。

3

特性:广泛的特性有助于您实现产品差异化,包括 User Metadata 和 User Externs 中的选项。

4

迁移:设计意图可以从一个 FPGA 或 SoC 迁移到另一个。

5

扩展:由 VNP4 生成的数据包处理块可以并行或串行部署,以支持诸如多级解析和多数据流水线系统等功能。

6

领域特异性:这种高级抽象解决方案具有领域特异性,使您能够在不牺牲性能情况下充分发挥抽象的优势。

7

面向数据包处理的 FPGA 专业知识:此解决方案以及硬件实现的质量印证了着我们在高吞吐量数据包处理领域深耕高速 FPGA 设计与存储器子系统多年的经验。

8

性能:此系统已经进行全新设计,以确保高吞吐量、低时延和最低资源占用。

编程协议不受数据包处理影响

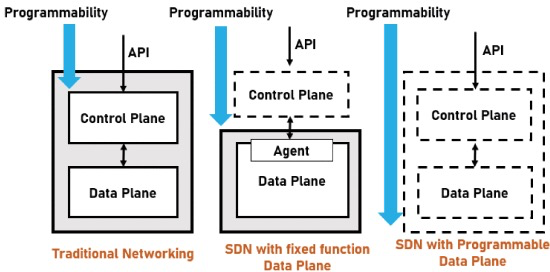

P4 是一种行业标准的、领域特定的编程语言,用于需求捕获且不依赖变成协议。VNP4 可以将 P4

设计意图转换为 AMD FPGA 或自适应 SoC 的设计解决方案,并支持程序员通过明确指定报头与数据包处理要求创建新的数据平面。为了实现 P4 的设计,编译器将预期功能映射到 VNP4 RTL 引擎与软件驱动程序的定制数据平面架构上。该映射选择适当的引擎类型,并根据 P4 指定的处理对其进行定制。用于实现此目标的专用引擎包括解析引擎、匹配操作引擎和反向解析引擎,均根据应用特定的需求生成。

生成的 RTL 集成到 AMD Vivado 设计套件的封装 IP 中,可以立即与其它标准 IP(如媒体访问控制器)结合使用,以创建完整的设备设计。然后对设计进行综合,并为目标设备生成 bit 文件。即使在生成综合设计数据之前,也可以获得关键的设计指标,如所需的时延和存储器资源。

现有 AMD 解决方案基于数百个客户反馈意见以及从早期迭代收集的信息优化而成。最新一代工具的三大特点包括:

原生支持 P416 语言

算法内容可寻址存储器技术

致力于实现高效资源利用和可靠时序收敛

-

FPGA

+关注

关注

1629文章

21748浏览量

604001 -

soc

+关注

关注

38文章

4173浏览量

218425 -

数据包

+关注

关注

0文章

262浏览量

24407 -

Vivado

+关注

关注

19文章

812浏览量

66624

原文标题:白皮书 | 利用 P4 与 Vivado 工具简化数据包处理设计

文章出处:【微信号:赛灵思,微信公众号:Xilinx赛灵思官微】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

mtu配置步骤详解 mtu与数据包丢失的关系

鞍山163.18平米户外P4条栅屏安装完工

利用P4与Vivado工具简化数据包处理设计

利用P4与Vivado工具简化数据包处理设计

评论