一、桥连现象概述

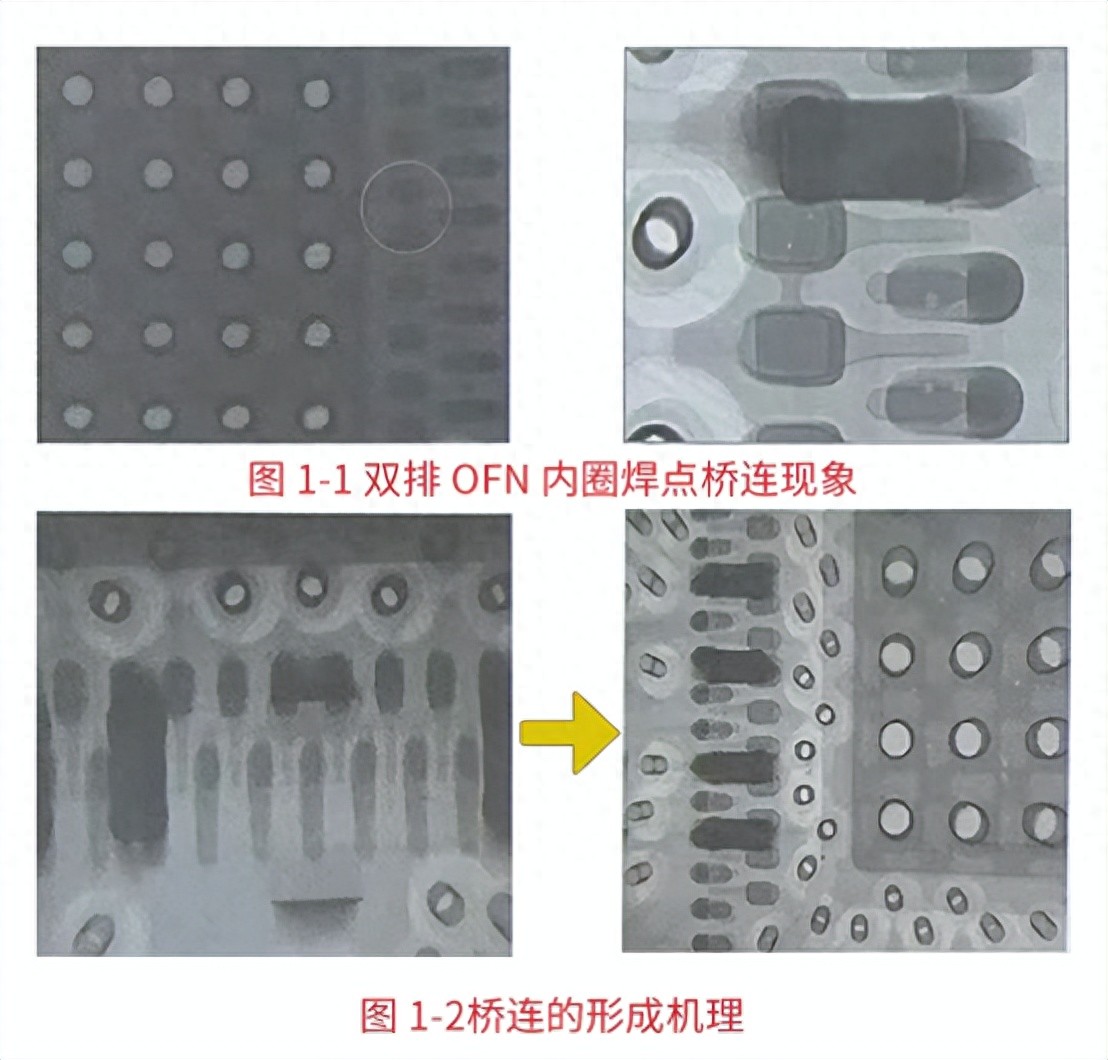

QFN封装中的桥连现象,尤其在双排QFN的内排焊点间较为常见,而单排QFN则相对较少出现。桥连是由于焊料被挤压到非润湿面而形成的,这通常会导致电气短路,严重影响电路的性能和可靠性。如图下图所示。

二、产生原因

焊料挤压:QFN封装底部有一个大面积的热沉焊盘,它决定了焊缝的高度。热沉焊盘上的焊膏通常不是印刷成一个整体图形,而是采用窗格式或条纹式,以排气并控制焊缝中的空洞。然而,这种设计减小了焊膏的覆盖面积,减少了焊膏的总量。在QFN再流塌落时,引脚焊料会向外挤压,容易引发桥连。

QFN变形:QFN封装的变形也是导致桥连的原因之一。当QFN内外排焊点的高度相差较大时(有时相差十多微米),焊料在再流过程中更容易受到挤压和流动,从而增加桥连的风险。

空洞率与桥连的对应关系:通常,桥连与信号焊盘的空洞率有对应关系。桥连率高时,往往空洞也会更多。这进一步证明了焊料挤压和排气不良是导致桥连的主要原因。

三、改进建议

针对QFN封装桥连现象的产生原因,我们可以从以下几个方面进行改进:

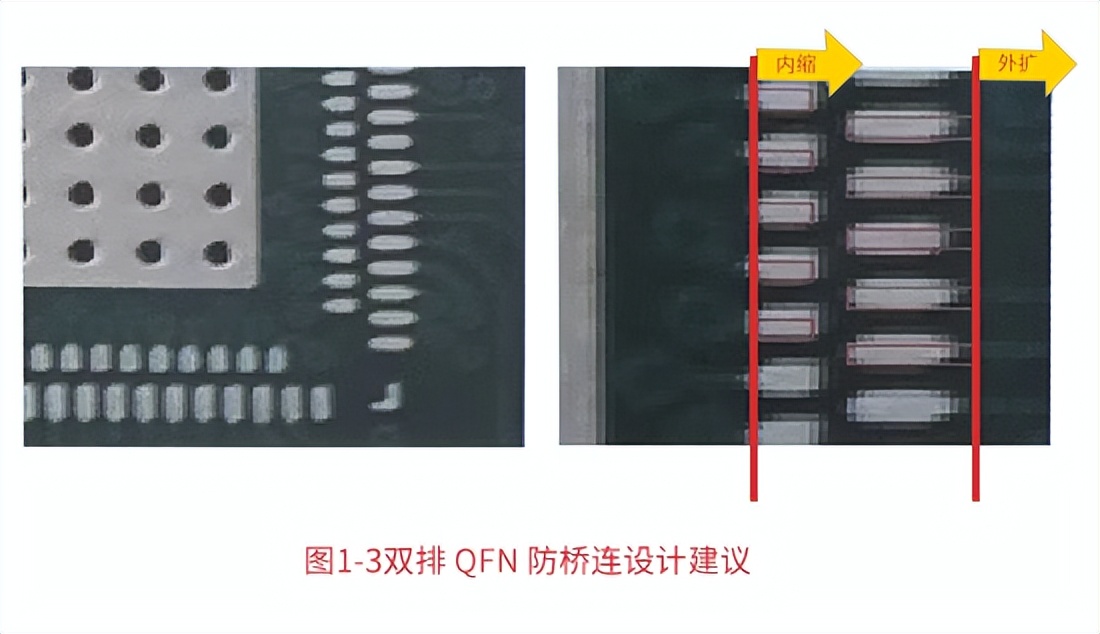

减少内圈焊膏印刷量:理论上,应根据热沉焊盘的焊盘覆盖率设计同等量的漏印面积。考虑到QFN本身焊盘比较小、印刷难度大,通常可以通过缩减内圈焊盘开口的尺寸来减少焊膏量。这样可以降低焊料在再流过程中的挤压程度,减少桥连的风险。双排 QFN 防桥连设计建议如下图所示

提供容锡空间:通过焊盘间去阻焊设计、宽焊盘窄开口工艺设计以及热沉焊盘阻焊定义等方法,为焊料提供更多的容锡空间。这有助于减少焊料在再流过程中的挤压和流动,从而降低桥连的风险。然而,需要注意的是,对于小焊盘而言,过度增加容锡空间可能会导致应力集中问题,因此需要谨慎设计。

综上所述,QFN封装桥连现象的产生原因主要包括焊料挤压、QFN变形以及空洞率与桥连的对应关系。针对这些问题,我们可以从减少内圈焊膏印刷量和提供容锡空间两个方面进行改进。通过合理的工艺设计和优化,我们可以有效降低QFN封装桥连的风险,提高电路的性能和可靠性。

审核编辑 黄宇

-

封装

+关注

关注

126文章

7843浏览量

142837 -

qfn

+关注

关注

3文章

189浏览量

56180

发布评论请先 登录

相关推荐

ads1291 QFN封装的散热PAD接AVSS还是DGND?

QFN封装中焊点形成的过程

如何解决Smt锡膏贴片加工中的桥连问题

分析波峰焊时产生连锡(短路)的原因以及解决办法

采用小型直流/直流转换器进行设计:HotRod™ QFN与增强型HotRod™ QFN封装

电机驱动单片机 PY32MD310,QFN32封装 ,主频最高48M

整流桥参数对封装的影响

引线框架贴膜工艺在QFN封装制程中的应用

QFN封装引脚间距较小问题的产生原因与解决方案

QFN封装对国产双轴半自动划片机的性能有哪些要求?

什么是QFN封装?手动焊接QFN封装方式

QFN封装桥连现象分析与改进建议

QFN封装桥连现象分析与改进建议

评论