01研究背景

短沟道效应严重制约了硅基晶体管尺寸的进一步缩小,限制了其在先进节点集成电路中的应用。开发新材料和新技术对于维系摩尔定律的延续具有重要意义。以二硫化钼 (MoS2) 为代表的二维半导体,即使在单层厚度下依然具有优异的电学性能,展现出在短沟道电子器件中的巨大应用潜力。然而,本征 MoS2作为 n 型半导体,本身不足以构建低功耗互补金属氧化物半导体 (CMOS) 电路,因此实现 MoS2中的 p 型载流子通道对于构建 CMOS 电路具有重要意义。掺杂是改变半导体极性的常用策略,V、Nb 和 Ta 等第五副族元素比 Mo 少一个价电子,是常见的 p 型掺杂剂。然而,目前人们对于掺杂 MoS2在短沟道下的电学特性仍然缺乏必要的认识。

02研究内容

近日,上海科技大学纪清清教授课题组通过使用密度泛函理论 (DFT) 和量子输运模拟,以 VS2-MoS2-VS2 面内异质结为模型体系构建二维晶体管,揭示了 V 掺杂位点在短沟道下具有辅助隧穿效应和杂质散射的双重电子学功能。

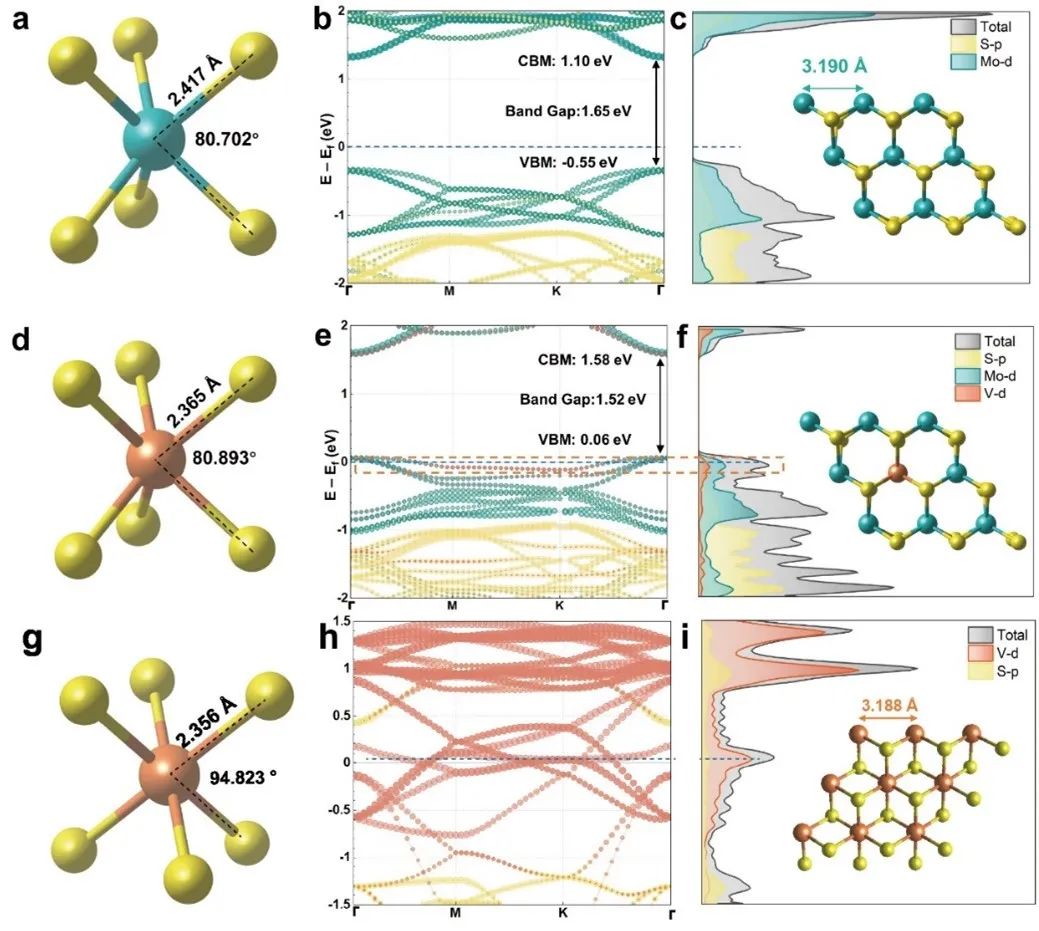

图1MoS2、V 掺杂 MoS2以及 VS2 的电子结构。

文章首先通过 DFT 计算了 MoS2,V 掺杂 MoS2以及 VS2 的电子结构,如图1所示,相比于本征 MoS2,V 掺杂对 MoS2电子结构的主要影响表现为在价带顶引入了新的电子态。

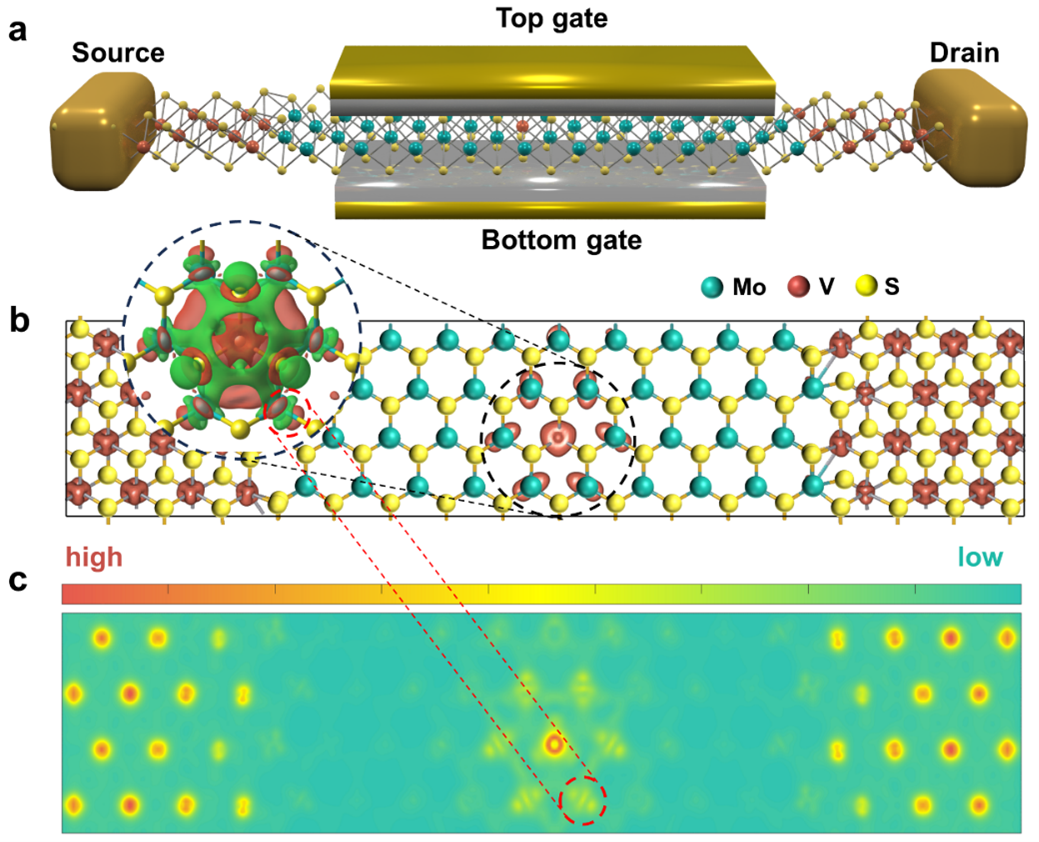

图2 以 VS2 和 V-MoS2 面内异质结为基础构建晶体管,EOT = 0.5 nm (a)。b, c 为价带顶的 LDOS 图。

紧接着,作者以 VS2, V-MoS2, VS2 面内异质结为基础构建晶体管 (EOT = 0.5 nm),以此来研究 V 掺杂位点在短沟道时对电输运的影响。文章首先计算了沟道区域的差分电荷密度,结果表明,V 原子只与最近邻的 Mo 原子发生了电子交换。该结果同样反映在价带顶的 LDOS 中,如图2b, c 所示,在 V 掺杂位点及其最近邻 Mo 原子上有电子态分布,而其他沟道区域则没有。

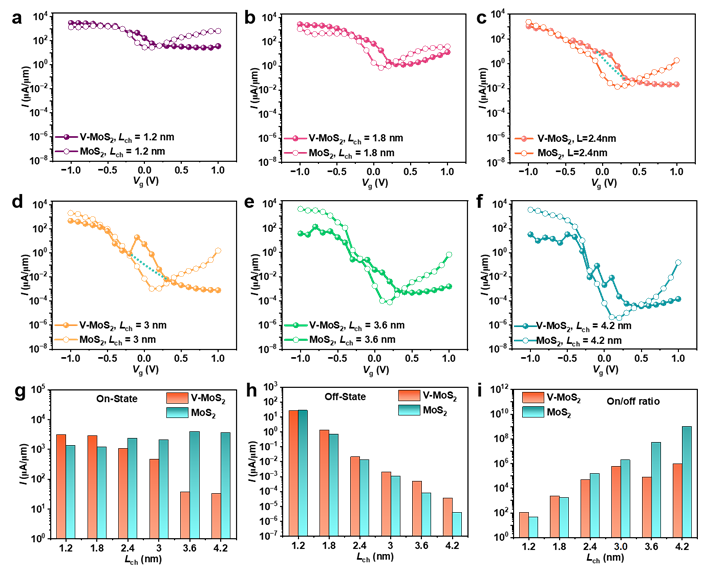

图3不同沟道长度下器件的转移特性曲线,以及从中提取的开、关态电流及开关比。

作者进一步通过 NEGF-DFT 对不同沟道长度下的本征 MoS2及 V-MoS2做电学输运模拟。研究发现,在沟道长度小于1.8 nm 时,V-MoS2 相比于本征 MoS2具有更高的阈值电压和更大开态电流。而当沟道长度增加到 2.4 nm 时,V-MoS2转移曲线的亚阈值区间出现跨导峰,这一迹象在沟道长度为 3 nm 时得到了极致体现。当沟道长度进一步增大时,V-MoS2的转移曲线变得不再光滑。

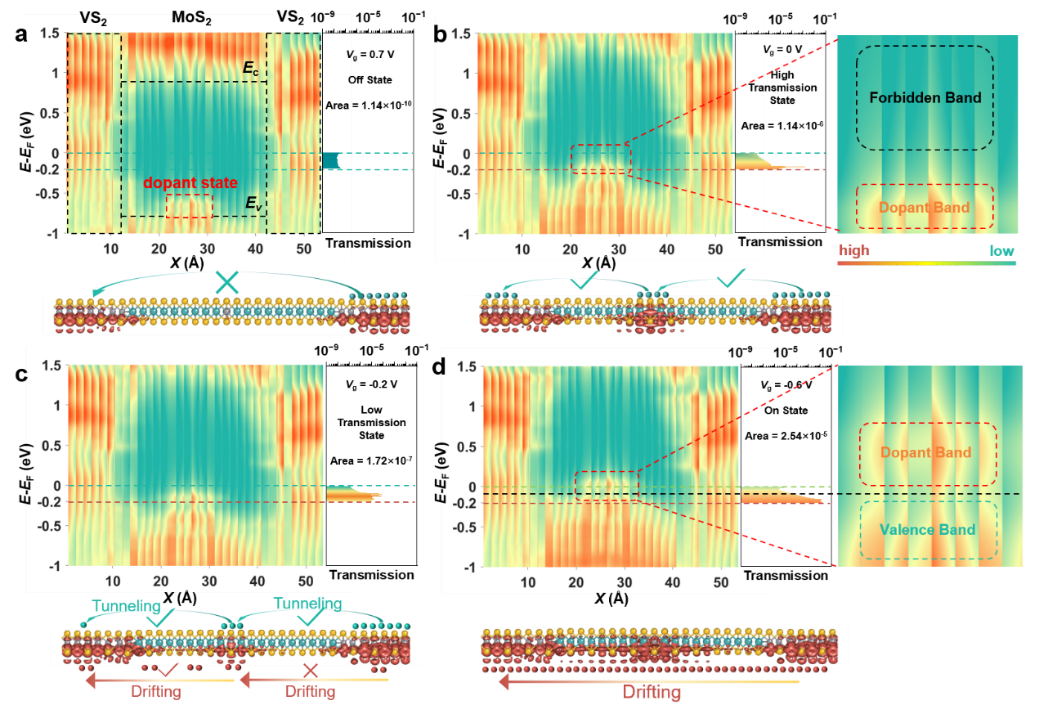

图4Lch = 3 nm 时,不同栅压下的 PDOS 及对应的电子透射谱。

为了深入理解这一现象,作者以沟道长度为 3 nm 的器件为例,分析了不同栅压下的 PDOS。如图4所示,随着栅压的减小,沟道区域的电子态被逐渐拉高,首先进入偏置窗口的是 V 掺杂位点的电子态。在该沟道长度下,载流子可以首先隧穿到 V 掺杂位点处,再隧穿到另一端电极,从而形成电流通道,在亚阈值区间表现为一个显著的拐点。

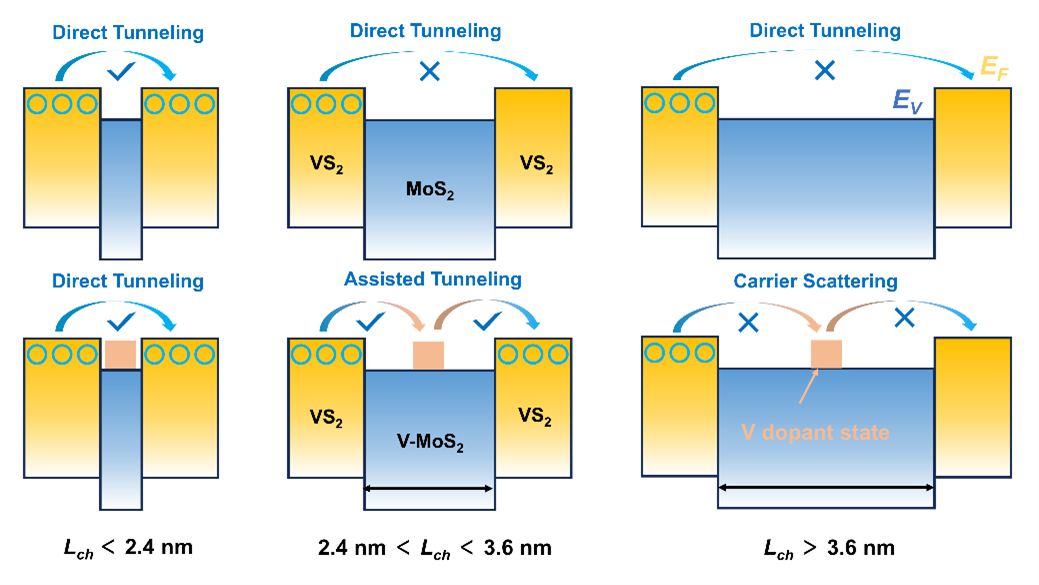

图5 不同沟道长度下 V 掺杂位点作用机制示意图。

作者绘制了不同沟道长度下 V 掺杂位点作用机制示意图以更加直观的说明其作用原理。如图5所示,当沟道长度小于 1.8 nm 时,载流子可以直接在两侧电极之间隧穿,而V掺杂态则提供了更多的隧穿机会,表现为开态电流增大。当沟道长度介于 2.4 nm 和 3 nm 之间时,载流子无法在两侧电极之间直接隧穿,但是可以通过 V 掺杂位点实现间接隧穿,即载流子先从一侧电极隧穿到 V 掺杂位点上,再隧穿到另一侧电极。在该沟道长度下,V 掺杂位点表现出辅助隧穿的作用,在亚阈值区间出现显著的拐点。当沟道长度进一步增加时,由于 V 掺杂位点距离两端电极过远,载流子无法实现从电极到掺杂位点的隧穿,所以此时 V 掺杂位点表现为人们所熟知的载流子散射作用,阻碍载流子的传导,使得转移曲线不光滑。

03总结展望

这项工作使用 NEGF-DFT 揭示了短沟道二维晶体管中杂原子掺杂的电子效应,发现了 MoS2中 V 掺杂位点的双重电子学功能,即辅助隧穿增大源漏电流以及作为散射中心阻碍载流子传导。这两种相互竞争的电子效应可以通过在 5 nm 以下的范围内改变沟道长度来进行调制。这项工作加深了人们对于掺杂二维材料短沟道电学特性的认识。上海科技大学物质学院博士生鲁跃和硕士生李晨雨为本文的共同第一作者,纪清清教授为独立通讯作者。

05通讯作者简介

纪清清,上海科技大学物质科学与技术学院助理教授、研究员、博士生导师,致力于化学途径实现下一代低维电子学。已在 Sci. Adv.,J. Am. Chem. Soc.,Adv. Mater.,Nano Lett. 等期刊上发表60余篇研究论文(第一或通讯作者论文20余篇),谷歌学术总引用6000余次,H-index=38。

-

集成电路

+关注

关注

5464文章

12671浏览量

375621 -

CMOS

+关注

关注

58文章

6231浏览量

243365 -

半导体

+关注

关注

339文章

31203浏览量

266364 -

晶体管

+关注

关注

78文章

10436浏览量

148552

原文标题:上海科技大学纪清清团队 | 短沟道二维晶体管中的掺杂诱导辅助隧穿效应

文章出处:【微信号:hzwtech,微信公众号:鸿之微】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

晶体管掺杂和导电离子问题原因分析

场效应晶体管的分类及作用

什么是鳍式场效应晶体管?鳍式场效应晶体管有哪些优缺点?

东芝面向超低功率MCU开发隧穿场效应晶体管

隧穿场效应晶体管是什么_隧穿场效应晶体管的介绍

一文详细了解高电子迁移率晶体管

准费米能级相空间及其在双极型二维场效应晶体管中的应用

二维半导体晶体管实际沟道长度的极限

隧穿晶体管的原理及优势

短沟道二维晶体管中的掺杂诱导辅助隧穿效应

短沟道二维晶体管中的掺杂诱导辅助隧穿效应

评论