绝缘体上硅(SOI)技术的基本思想是通过将承载电子器件的晶片表面的薄层与用作机械支撑的块晶片电绝缘来解决器件和衬底之间的寄生效应。

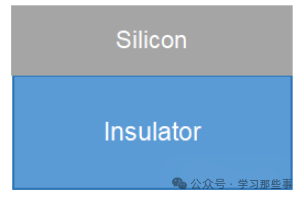

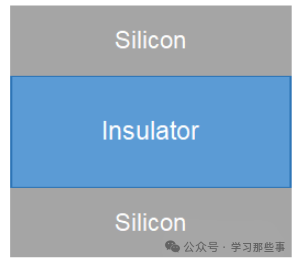

大多数微电子器件仅利用硅晶圆顶部前几百纳米用于电路传输。晶片厚度的其余几百微米几乎完全用作器件的机械支撑。器件和衬底之间的电相互作用可能会导致许多有害的寄生效应。绝缘体上硅(SOI)技术的基本思想是通过将承载电子器件的晶片表面的薄层与用作机械支撑的块晶片电绝缘来解决这个问题。这可以通过将器件层放置在由绝缘材料制成的晶片上来实现(见图1),或者通过使用绝缘夹层将器件层与硅块分离(见图 2)。大多数当前的SOI方法都集中在绝缘夹层结构上。

图1硅器件层在绝缘体上

图2埋层绝缘体层将表面 Si 层与Si衬底分隔开

为什么要使用SOI?

①避免器件和衬底之间相互作用而产生不必要的寄生效应,主要是降低源极和漏极与衬底之间产生的寄生电容。

②防止闩锁,由于在CMOS工艺中形成寄生pnp和npn 双极型晶体管,导致Vdd和Vss轨道之间产生低阻抗路径。这些BJT形成具有正反馈的pnpn结构,将电源轨道短路至接地,从而导致过大电流流动,造成器件损坏。

③器件的完全电介质隔离降低了寄生电容,从而提高了性能。克服了亚微米器件固有的短沟道效应。

④随着晶体管的缩小,栅极的长度也随之减小。栅极对通道区域的控制也随之减小,从而降低了晶体管的性能。SOI使用体偏置来提供对通道的更多控制。

⑤减少因亚阈值漏电和二极管漏电流而增加的漏电功率。

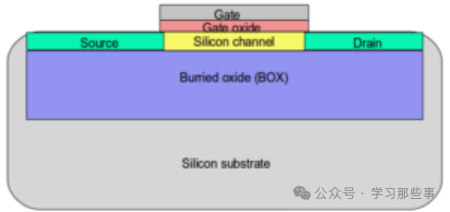

SOI 晶圆的结构

SOI晶圆结构具有三个基本特征:

顶部硅器件层:该超薄层能够形成有源器件,一般5nm~2μm;

埋氧层(BOX):隔离器件层,一般5nm~2μm;

硅衬底:提供机械强度和支撑,一般200~700μm。

-

硅晶圆

+关注

关注

4文章

267浏览量

20631 -

晶片

+关注

关注

1文章

403浏览量

31463 -

SOI

+关注

关注

4文章

69浏览量

17633

原文标题:为什么要用SOI(Silicon-on-insulator)

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

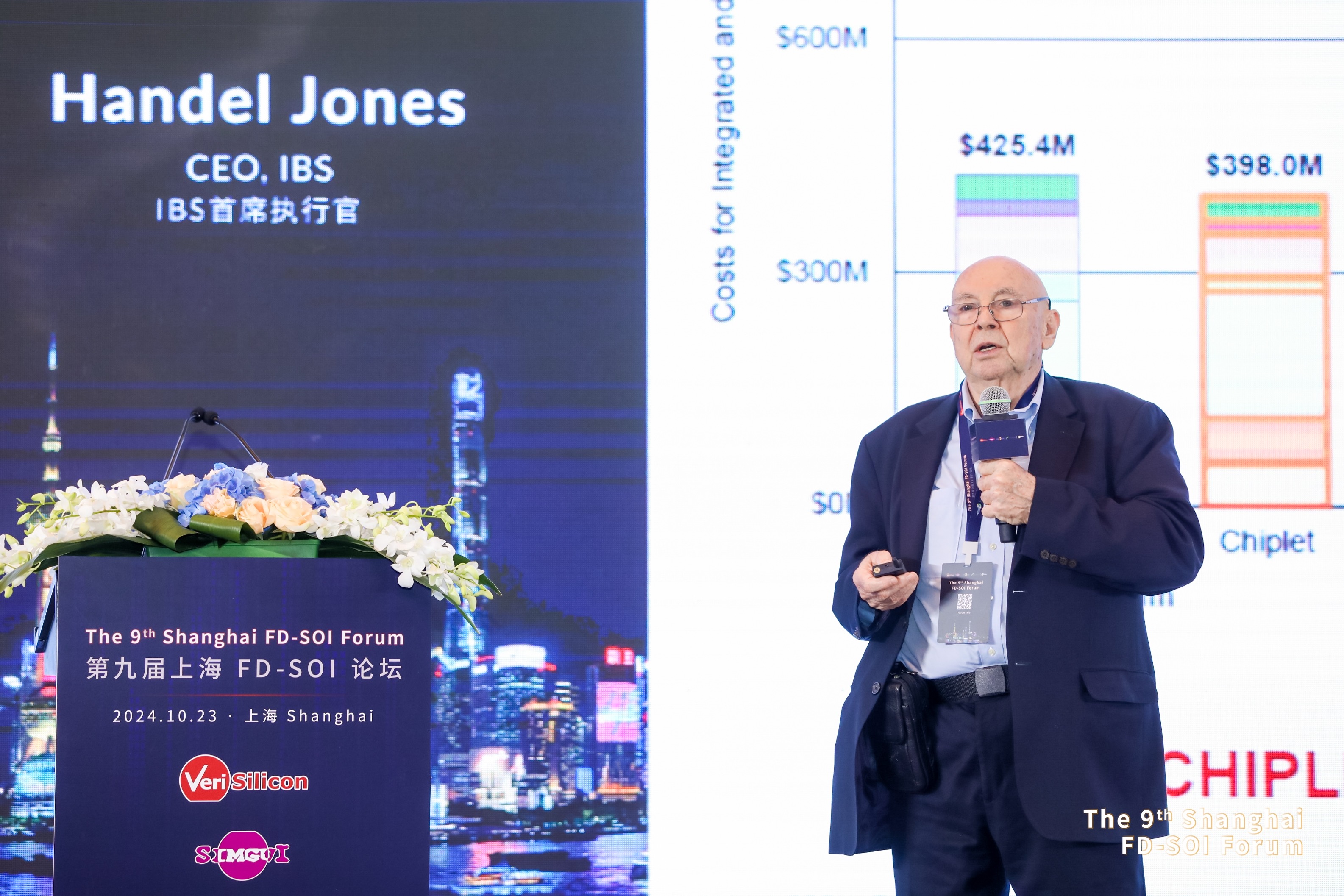

IBS首席执行官再谈FD-SOI对AI的重要性,在≥12nm和≤28nm区间FD-SOI是更好的选择

示波器探头接地的重要性

NLP技术在人工智能领域的重要性

论RISC-V的MCU中UART接口的重要性

模拟前端电路的重要性

蜂鸣器的用途和重要性

射频前端底层技术的卓越性能,RF-SOI为5G赋能

PLC网关的重要性

一文看懂SOI的重要性

一文看懂SOI的重要性

评论