加速系统功能扩展

对高性能计算、下一代服务器和AI加速器的需求迅速增长,增加了处理更大工作负载的需求。这种不断增加的复杂性带来了两个主要挑战:可制造性和成本。从制造角度来看,这些处理引擎正接近光刻机可以蚀刻的光罩的最大尺寸;而随着芯片尺寸的增大和相应的良率降低,单个芯片的成本可能会显著增加。

戈登·摩尔曾说过:“将大型系统由较小的功能构建,分别封装并互连,可能更经济。”在芯片设计中,为了满足性能提升的需求,行业正在从系统级芯片(SoC)转向使用晶圆级封装的系统级封装(SiP)。

异构SoC涉及在IO或核心级别对SoC进行分区,使用模块化方法与不同的构建块。这提供了几个优势,包括支持超出光罩尺寸的SoC,提高芯片良率,并实现设计模块化。然而,异构芯片引入了新的挑战,包括由于芯片之间和封装的紧密交互而增加的设计复杂性,支持跨装配和制造过程的可测试性,以及由于芯片的接近性而进行的热管理。3D集成能够实现使用不同技术和材料制造的IC芯片的异构集成,从而实现高性能、低成本和紧凑尺寸要求的集成、复杂和多功能微系统。

封装的进步使多芯片系统成为可能

需要处理大量数据的新兴半导体应用正在推动先进封装的发展。各种先进封装技术,包括并排放置或垂直放置,已经成为异构集成技术实施的一部分。2.5D和3D封装作为重要的解决方案获得了普及,每种技术都提供了独特的优势和挑战,使其成为半导体制造商和开发者的重要考虑因素。

在2.5D封装中,两个或多个芯片并排放置,通过中介层将一个芯片连接到另一个芯片。中介层充当桥梁,连接单个芯片并提供高速通信接口,允许在单个封装上更灵活地结合不同功能。通过在中介层上堆叠芯片,2.5D封装减少了封装的整体占地面积(与2D相比),使其非常适合更小和更薄的设备。中介层和桥提供了大量高密度的BUMPs和走线,有助于增加带宽。

在3D IC技术中,通过垂直堆叠进行芯片连接,提高了封装的整体性能和功能。这允许集成具有多层和多功能的芯片。特别是对于混合键合等3D封装技术,这种集成趋势导致芯片之间的BUMPs间距急剧缩小,从而减少了相应的互连距离和相关寄生效应。

可扩展性:互连

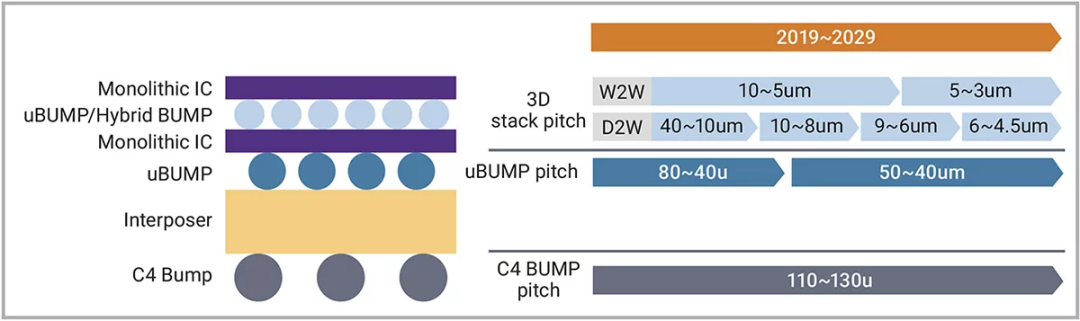

由于对更高带宽的需求和制造过程及封装技术的进步,互连从传统的铜uBUMP到最先进的40um间距uBUMP,再进一步缩小到10um(图2)发生了显著变化。

▲图2BUMPs间距的缩小(来源:先进封装的现状-2023年6月,Yole Intelligence)

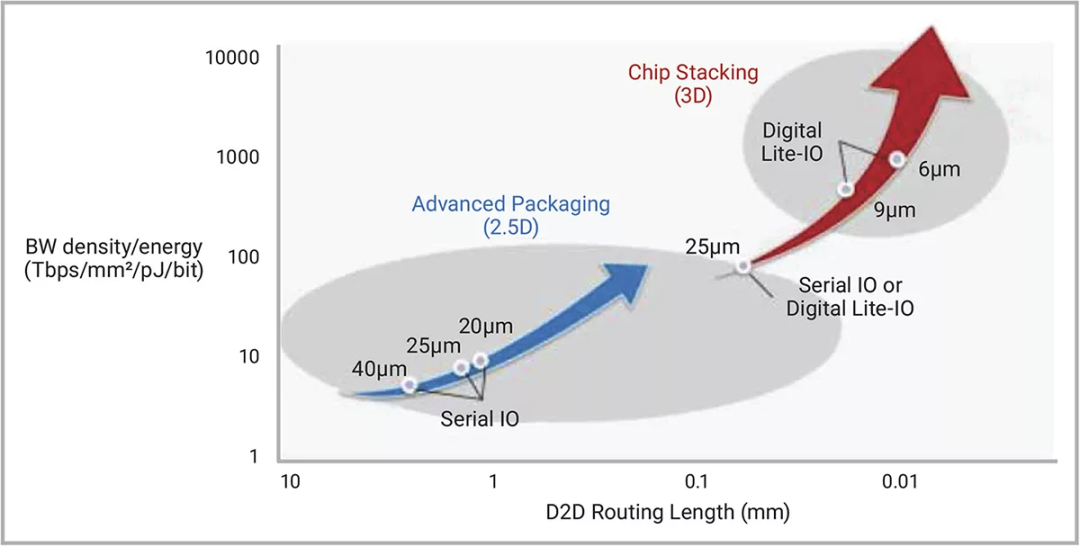

在2.5D场景中,通过中介层上的重分布层(RDL)进行芯片之间的连接,芯片之间的距离通常在100um左右。随着3D场景中芯片堆叠技术的进步,使用uBUMP进行芯片的垂直堆叠允许芯片之间直接连接,将距离减少到不到40um。这显著减少了基板的尺寸。此外,在3D集成中,传输的IO信号不再需要放置在芯片的边缘。此外,通过在集成芯片系统中使用混合键合技术(SoIC,3D),芯片之间的垂直连接更加紧密。混合键合通过微小的铜对铜连接(<10um)连接芯片。混合键合的较小BUMPs间距允许在相同区域内具有数千个IO通道,进一步提高集成度和性能。这一进步显著提高了数据带宽,即使在较低的工作频率下(与2.5D相比)。因此,鉴于这一技术进步,选择基于简单数字IO的解决方案,如新思科技 3DIO(图3),不仅提高了IO电路的可靠性,还在面积效率方面显示出比串行IO更好的结果质量。

▲图33DIC互连的全景图(来源:3DIC时代的互连,台积电,IEEE,2022年)

新思科技 3DIO平台提供灵活性、可扩展性和最佳性能

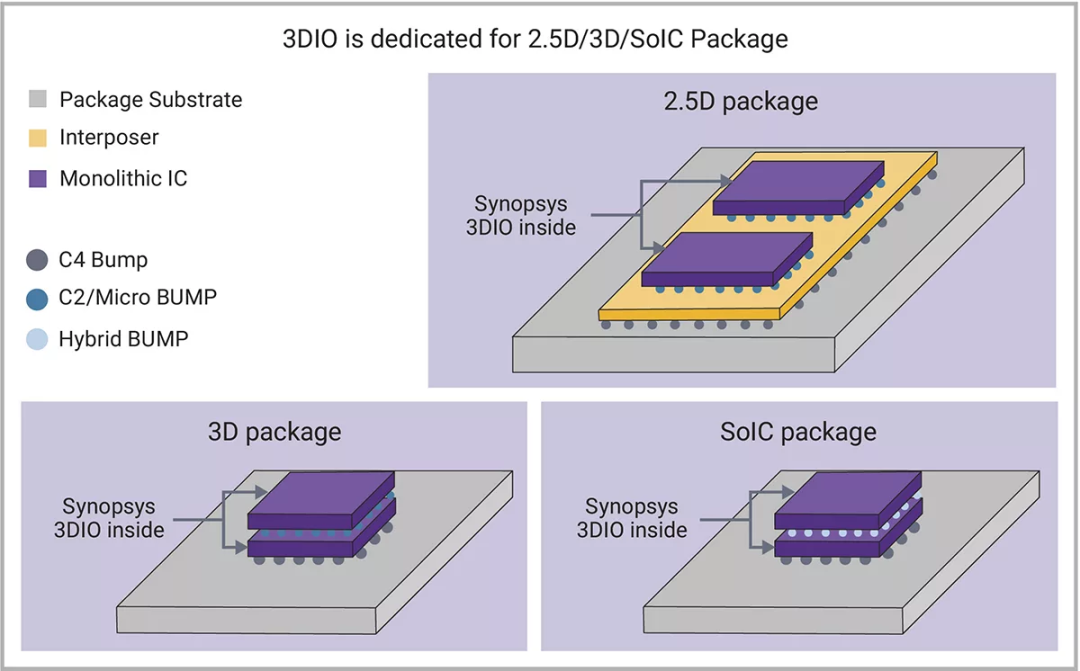

新思科技 3DIO平台(图4)专为多芯片异构集成而调整,提供多功能解决方案,实现3D堆叠中功率、性能和面积(PPA)的最佳平衡,以满足新兴封装需求。此外,该平台还能加快时序收敛,这是芯片对芯片集成中的关键挑战。

▲图4新思科技 3DIO平台架构支持2.5D、3D和SoIC封装

新思科技 3DIO平台包括以下内容:

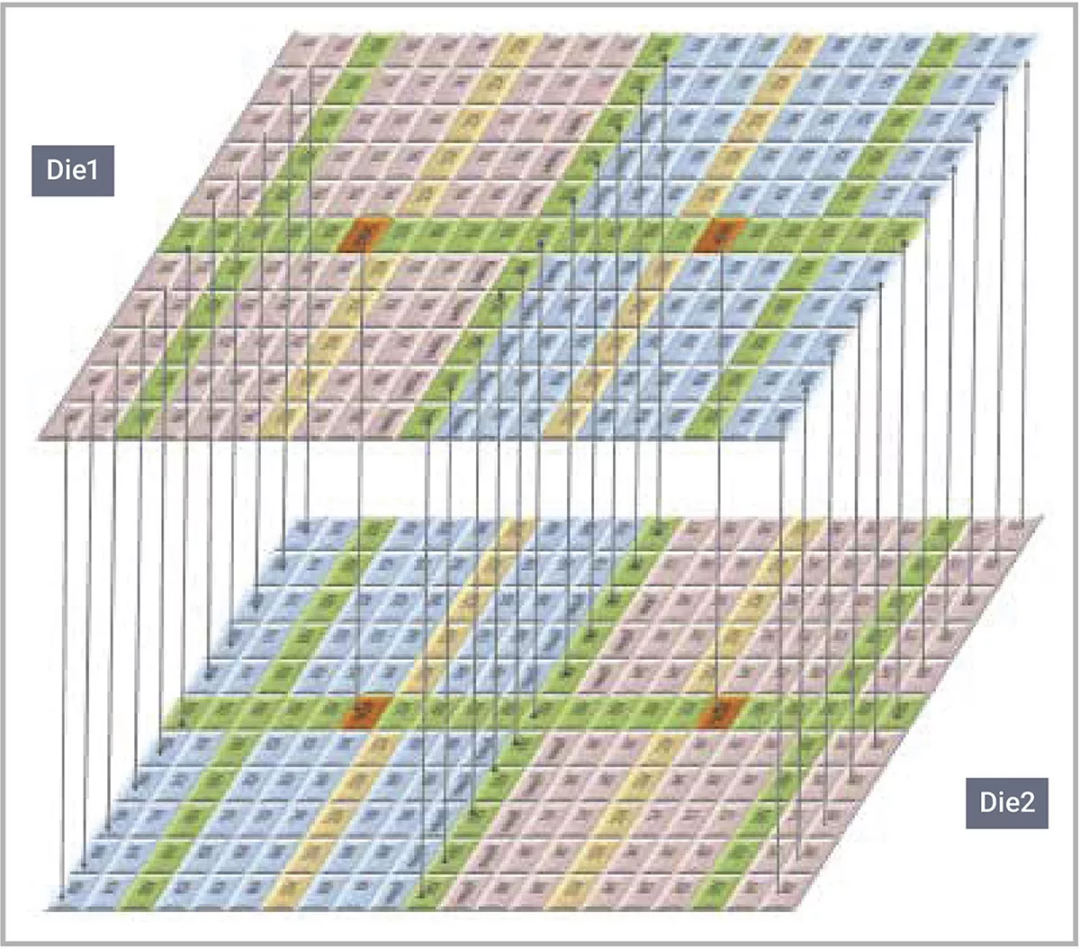

新思科技可综合3DIO包括与新思科技标准单元库兼容的可综合Tx/Rx单元和用于最佳ESD保护的可配置充电设备模型(CDM)。随着IO通道数量的急剧增加,优化的新思科技 3DIO解决方案利用自动布置和布线(APR)环境直接在BUMPs上布置和布线IO。该解决方案支持使用微BUMP和混合BUMP的2.5D和3D封装。新思科技 3DIO单元支持高数据速率,并提供最低功耗解决方案,面积优化以适应混合BUMP区域。新思科技源同步3DIO(SS3DIO)扩展了可综合的3DIO单元解决方案,具有时钟转发功能,以帮助降低比特错误率(BER)并简化芯片之间的时序收敛。SS3DIO提供可扩展性,以创建具有最佳PPA和ESD的自定义大小宏。TX、RX和时钟电路支持匹配的数据和时钟路径,数据在发送时钟边沿发射,并在相应的接收时钟边沿捕获。新思科技源同步3DIO PHY是一个64位硬化PHY模块,具有内置冗余,优化以实现最高性能。具有CLK转发的3DIO PHY降低了BER,并简化了实现以及POWER/CLK/GND BUMP的最佳布置(图5)。

▲图5新思科技同步3DIO PHY视图(来源:同步3DIO PHY横截面视图)

结语

随着封装技术的进步和互连密度的增加,给定芯片面积的IO通道显著增加。相应的IO通道长度减少提高了性能,但也增加了对更精简接口的需求。新思科技 3DIO平台为客户提供多功能解决方案,以实现可调的集成多芯片设计结构。新思科技 3DIO平台的最优面积经过精心设计,以适应BUMPs,在实现和信号布线方面提供显著优势。在3D堆叠技术中,用于信号传输的源同步时钟设计可以帮助客户实现更低的BER并简化时序收敛。新思科技 3DIO平台专为多芯片集成而量身定制,使客户能够创建高效的芯片设计,并加快上市时间,利用新思科技 3DIC编译器加速集成并为给定技术提供优化的PPA。除了3DIO平台外,新思科技多芯片解决方案还包括UCIe IP和HBM3 IP。

-

soc

+关注

关注

38文章

4156浏览量

218125 -

封装技术

+关注

关注

12文章

547浏览量

67981 -

新思科技

+关注

关注

5文章

794浏览量

50333 -

3D封装

+关注

关注

7文章

133浏览量

27116

原文标题:新思科技3DIO全方位解决方案,推进2.5D/3D封装技术

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

2.5D/3D芯片-封装-系统协同仿真技术研究

分享一下小芯片集成的2.5D/3D IC封装技术

3D封装结构与2.5D封装有何不同?3D IC封装主流产品介绍

新思科技3DIO平台助力2.5D/3D封装技术升级

新思科技3DIO平台助力2.5D/3D封装技术升级

评论