文章来源:半导体与物理

原文作者:jjfly686

本文简单介绍了两种新型的选择性刻蚀技术——高氧化性气体的无等离子体刻蚀和原子层刻蚀。

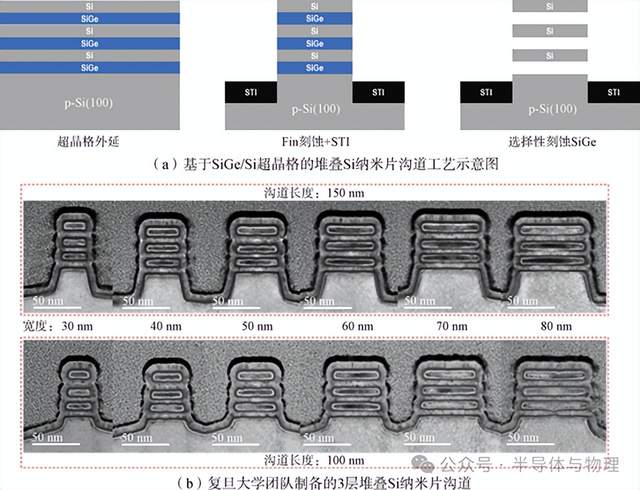

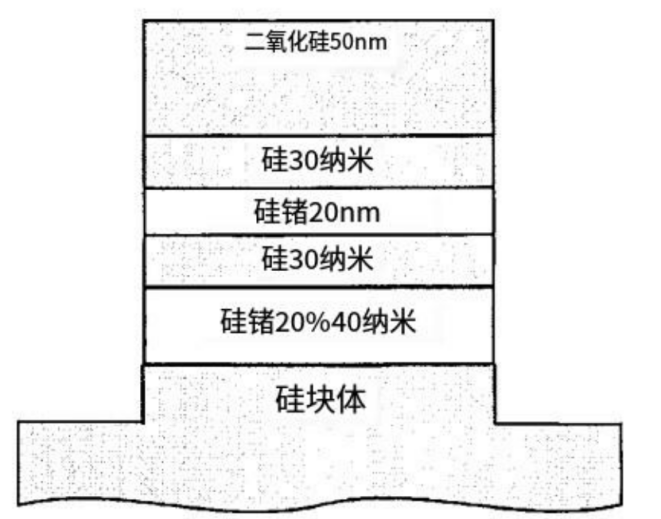

全环绕栅极晶体管(Gate-All-Around FET, GAAFET)作为一种有望替代FinFET的下一代晶体管架构,因其能够在更小尺寸下提供更好的静电控制和更高的性能而备受关注。在制造n型GAAFET的过程中,一个关键步骤是在内隔层沉积之前对Si-SiGe堆叠纳米片进行高选择性的SiGe:Si蚀刻,以产生硅纳米片并释放沟道。

本文将探讨这一过程中涉及的选择性刻蚀技术,并介绍两种新型的刻蚀方法——高氧化性气体的无等离子体刻蚀和原子层刻蚀(ALE),它们为实现高精度、高选择性的SiGe刻蚀提供了新的解决方案。

GAA结构中的SiGe超晶格层

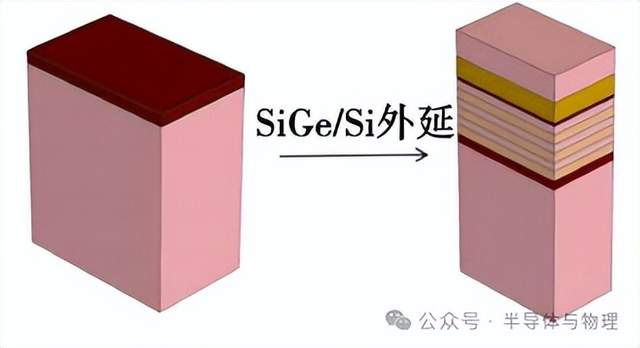

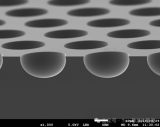

在GAAFET的设计中,为了增强器件性能,通常会在硅衬底上交替生长Si和SiGe层,形成多层结构,即所谓的超晶格。这些SiGe层不仅能够调整载流子浓度,还能通过引入应力来改善电子迁移率。然而,在后续的工艺步骤中,需要精确地去除这些SiGe层,同时保留硅层,这就要求有高度选择性的刻蚀技术。

选择性刻蚀SiGe的方法

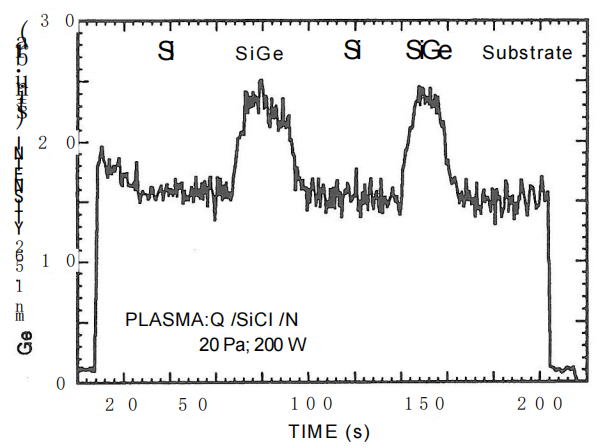

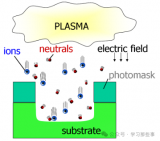

1.高氧化性气体的无等离子体刻蚀

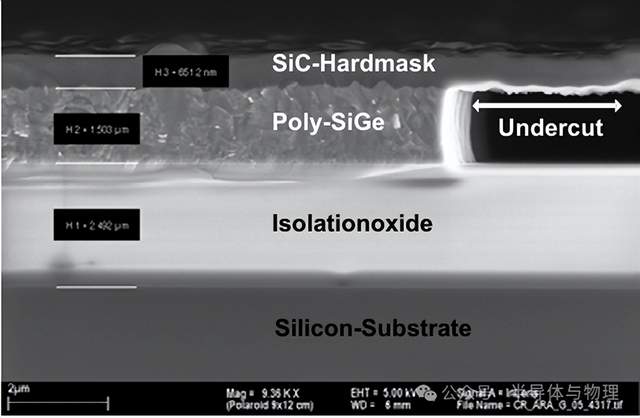

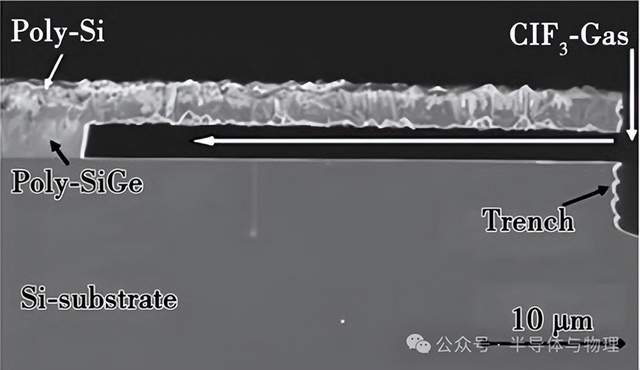

ClF3气体的选择:这种刻蚀方法采用具有极高选择性的高氧化性气体,如ClF3,SiGe:Si选择比可达到1000-5000。并且可以在室温下完成刻蚀,且不会造成等离子体损伤。

低温高效:最佳温度大约在30°C左右,实现了低温条件下的高选择性刻蚀,避免了额外热预算的增加,这对保持器件性能至关重要。

干燥环境:整个刻蚀过程处于完全干燥条件下进行,消除了结构粘连的风险。

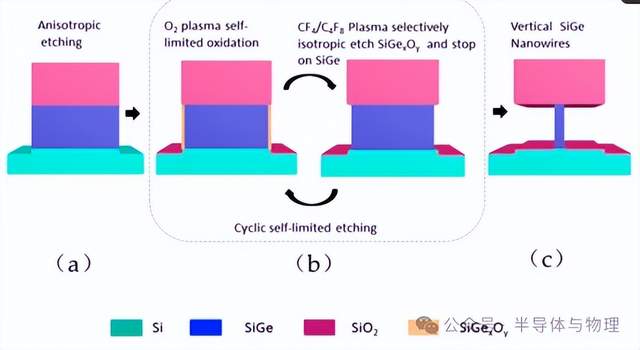

2.原子层刻蚀(ALE)

自限制特性:ALE是一种基于两步循环工艺的刻蚀技术,首先对所要刻蚀材料表面的第一层进行改性,然后将改性层去除而不影响未改性的部分。每一步都具有自限制性,保证了每次仅去除几个原子层的精确度。

循环刻蚀:不断重复上述两步工艺,直到达到所需的刻蚀深度。这一过程使得ALE能够实现内侧墙中小尺寸空腔的原子级别精度刻蚀。

声明:本网站部分文章转载自网络,转发仅为更大范围传播。 转载文章版权归原作者所有,如有异议,请联系我们修改或删除。联系邮箱:viviz@actintl.com.hk, 电话:0755-25988573

审核编辑 黄宇

-

SiGe

+关注

关注

0文章

62浏览量

23460 -

刻蚀

+关注

关注

2文章

178浏览量

13081

发布评论请先 登录

相关推荐

选择性沉积技术介绍

晶圆表面温度对干法刻蚀的影响

矿井电网选择性绝缘在线监测

过电流保护的选择性是靠什么来实现的

交流二元继电器如何具有相位选择性和频率选择性

在smt贴片加工厂中选择性波峰焊存在的作用和意义

浅谈矿井电网选择性绝缘在线监测技术研究

SMT加工厂用选择性波峰焊有什么优点吗?

锗化硅(SiGe)和硅(Si)之间的各向同性和选择性蚀刻机制

电子制造业中的选择性波峰焊有哪些优缺点?

Si/SiGe多层堆叠的干法蚀刻

韩国科学技术院开发Micro LED选择性转移印刷技术

SiGe与Si选择性刻蚀技术

SiGe与Si选择性刻蚀技术

评论