随着人工智能、高性能计算为代表的新需求的不断发展,先进封装技术应运而生,与传统的后道封装测试工艺不同,先进封装的关键工艺需要在前道平台上完成,是前道工序的延伸。CoWoS作为英伟达-这一新晋市值冠军的GPU中采用的先进封装技术如今变得愈发重要。

据有关报告称:CoWoS封装技术的产能继续是制约AI芯片供应的最大瓶颈,也是AI芯片需求能否被满足的关键。

DIGITIMES Research最新报告显示,受云端AI加速器需求旺盛推动,2025年全球对CoWoS及类似封装产能的需求或将增长113%。

DIGITIMES Research认为,英伟达正在显著增加高端GPU的出货量,以满足其GB200系统的需求,并为台积电的CoWoS产能下了大量订单。与此同时,为谷歌和亚马逊提供ASIC设计服务的博通和Marvell等公司也在不断增加晶圆订单。

CoWoS简介

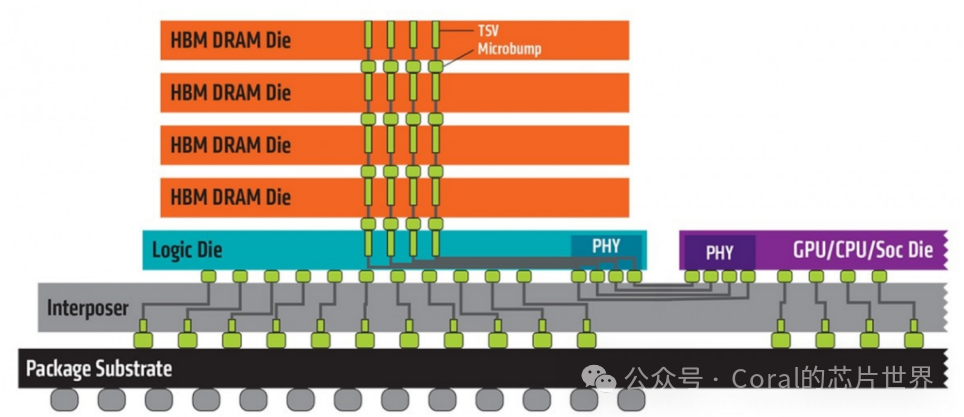

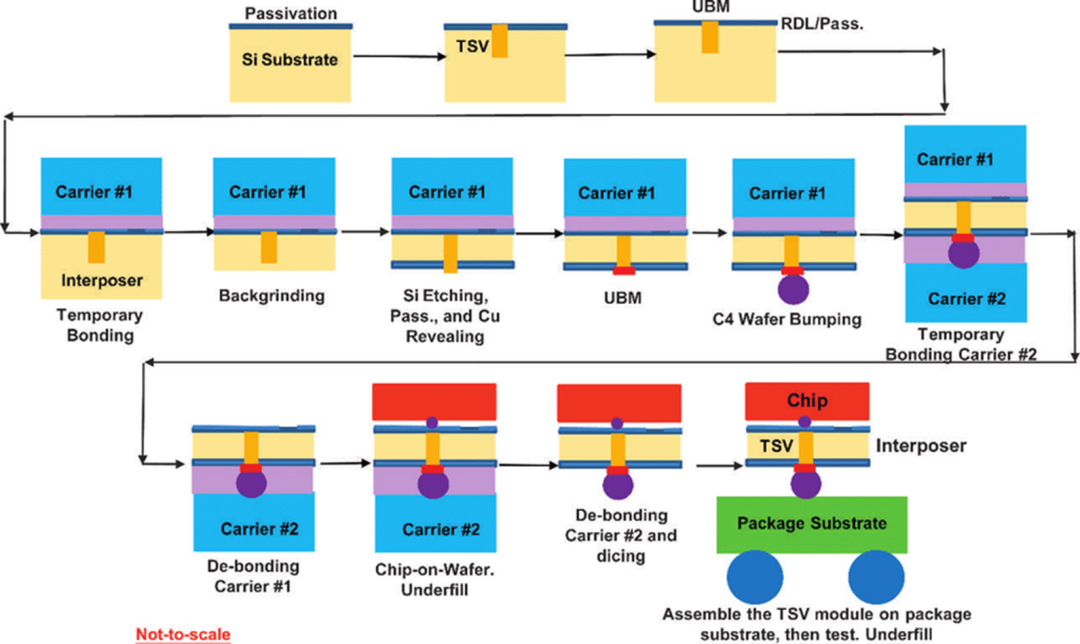

CoWoS 的全称为Chip on Wafer on Substrate。简单来说是先将逻辑芯片与存储芯片一同放在硅中介层上,使用Chip on Wafer(CoW)的封装制程连接至底层基板上。这种封装模式可以使多颗芯片可以封装到一起,通过Si Interposer互联,达到了封装体积小,功耗低,引脚少的效果。在高性能计算领域具有巨大的优势。

目前台积电提供三种CoWoS封装服务,分别为CoWoS-S,CoWoS-R,CoWoS-L。随着英伟达Blackwell系列GPU的大规模生产,台积电将从2025年第四季度开始从CoWoS-S过渡到CoWoS-L工艺,使CoWoS-L成为台积电CoWoS技术的主要工艺。

CoWoS S

CoWoS-S平台为人工智能 (AI) 和超级计算等超高性能计算应用提供一流的封装技术。该晶圆级系统集成平台在较大的硅中介层区域上提供高密度互连和深沟槽电容器,以容纳各种功能性顶部晶片/晶片,包括逻辑芯片,并在其上堆叠了高带宽内存 (HBM) 立方体。目前,最大 3.3 倍掩模尺寸(或 ~2700mm2)的中介层已准备好投入生产。对于大于 3.3X 标线尺寸的中介层,建议使用 CoWoS-L和 CoWoS-R 平台。不同的互连选项提供了更大的集成灵活性,以满足性能目标。

CoWoS R

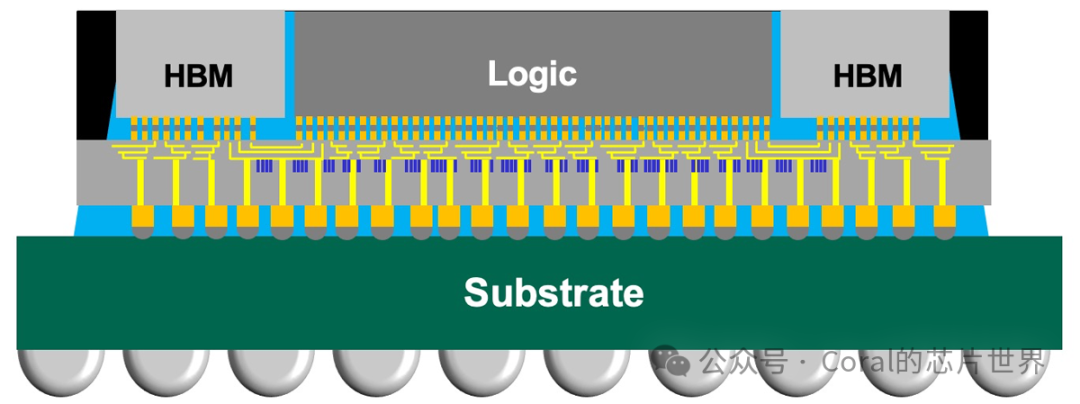

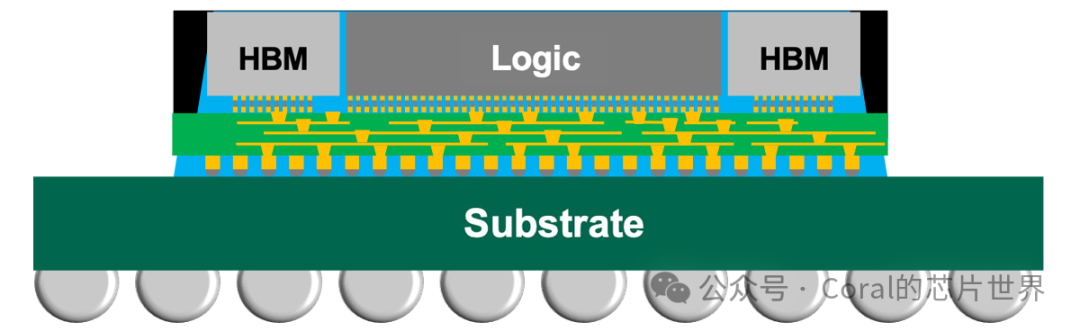

CoWoS-R是 CoWoS先进封装系列的成员,它利用再分布层 (RDL) 中介层作为片上系统(SoC) 和/或高带宽内存 (HBM) 之间的互连,以实现异构集成。RDL 中介层由聚合物和铜走线组成,相对灵活。这增强了 C4 接头的完整性,并允许封装扩展其尺寸以满足非常复杂的功能需求。

CoWoS L

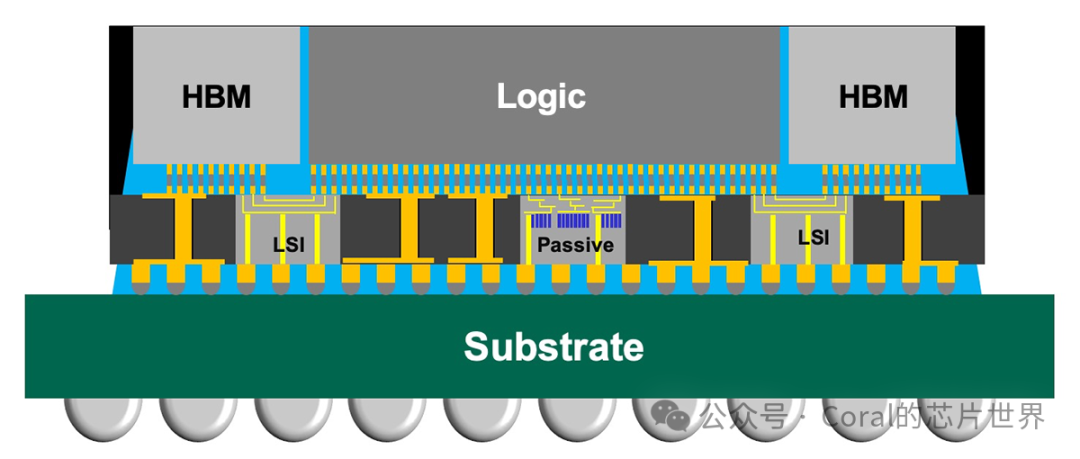

CoWoS-L 是 CoWoS平台上的后芯片封装工艺之一。它结合了 CoWoS-S 和 InFO(扇出型)技术的优点,使用中介层和本地硅互连 (LSI) 芯片进行晶粒间互连,并使用 RDL 层进行电源和信号传输,从而提供最灵活的集成。

-

CoWoS

+关注

关注

0文章

137浏览量

10484 -

先进封装

+关注

关注

2文章

398浏览量

241

原文标题:CoWoS-先进封装技术

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

CoWoS工艺流程说明

CoWoS先进封装技术介绍

CoWoS先进封装技术介绍

评论