本文介绍了7纳米工艺面临的各种挑战与解决方案。

一、什么是7纳米工艺?

在谈论7纳米工艺之前,我们先了解一下“纳米”是什么意思。纳米(nm)是一个长度单位,1纳米等于10的负九次方米。对于半导体芯片来说,纳米通常指的是晶体管的最小尺寸,或者是构成芯片中各个功能单元的最小结构尺寸。因此,7纳米工艺指的是在芯片上制造出其最小结构为7纳米的晶体管。

随着晶体管尺寸不断缩小,芯片的集成度、运算速度和能效得以大幅提升。但这些技术突破的实现,并非一帆风顺,而是需要解决一系列从设计到材料、工艺到制造的技术难题。

二、为什么突破7纳米工艺这么难?

突破7纳米工艺的困难,实际上可以从多个维度进行拆解。为了更好地理解,我们将其比喻为搭建一个越来越精细、复杂且高效的机器。想象一下,你正在尝试制造一个高精度的时钟,每个齿轮和零件都必须非常小且精准,甚至每个细节的误差都可能导致整体功能失效。对于半导体制造工艺来说,7纳米工艺正是这样一个极限的挑战。

1. 物理极限的逼近

随着晶体管尺寸的不断减小,已经逼近了物理层面的一些极限。晶体管的尺寸一旦小于10纳米,量子效应开始显现。比如,电子在这些微小的晶体管中会表现出量子隧穿效应(quantum tunneling),即电子可以穿过晶体管的“阱”,导致电流泄漏,从而影响芯片的性能和功耗。

为了克服这些问题,芯片设计师需要依靠一些创新技术,比如使用更高质量的材料(如高介电常数材料),或者采用更先进的晶体管结构(如FinFET)。然而,这些技术的引入并不是简单的升级,而是面临材料、制造和工程方面的重大挑战。

2. 光刻技术的挑战

光刻技术是半导体制造过程中最关键的环节之一。光刻是通过将设计图案投影到硅晶片上的光敏材料上,从而刻画出芯片的结构。然而,随着晶体管尺寸的不断缩小,传统的光刻技术(如深紫外光刻,DUV)无法满足如此精细的制造需求。

为了解决这个问题,业界引入了极紫外光刻(EUV)技术,它能够使用更短的光波长,从而提升光刻精度。然而,EUV技术本身也面临很多问题:首先,EUV光源的开发难度大,需要更高的功率才能达到足够的曝光效果;其次,EUV曝光过程的成像精度对设备要求非常高,且光刻胶材料的研发也处于不断进步之中。

因此,光刻技术的突破不仅需要先进的设备支持,还需要材料科学、光学等领域的多学科协作。

3. 材料与器件设计的挑战

随着7纳米工艺的推进,单纯依靠硅材料已难以满足高效能的要求。材料科学的限制让我们不得不考虑其他替代材料,如高介电常数(High-K)材料以及新的半导体材料(如氮化镓、碳纳米管等)。这些新材料在提高芯片性能方面有潜力,但它们的兼容性、稳定性以及与现有生产工艺的结合仍是难题。

此外,7纳米工艺要求晶体管的栅长非常短,这对器件的设计提出了更高的要求。设计师需要通过精确控制每个器件的尺寸和布局,以避免因为误差导致电流泄漏、热效应过高等问题。

4. 制造精度和成本控制

制造7纳米工艺的芯片需要超高精度的设备和工艺流程。例如,硅片的处理、薄膜的沉积、刻蚀等工艺都要求极高的精度,这对生产设备的要求极为苛刻。此外,由于7纳米工艺的晶体管尺寸极小,即便是极微小的制造误差也可能导致整个芯片性能的严重下降,因此在生产过程中每一步都要严格把控。

制造过程中的高精度要求和复杂的工艺链条意味着成本的显著提高。例如,使用EUV光刻技术需要更昂贵的设备,而且制造的良率较低,生产过程中很容易出现缺陷,从而导致芯片报废。

5. 功耗和热管理问题

在芯片尺寸越来越小的情况下,集成的晶体管数量越来越多,而每个晶体管仍需要消耗电力。随着晶体管数量的增加,功耗问题逐渐显现。虽然7纳米工艺相比传统工艺的能效有所提升,但芯片内各个部分的功耗管理变得更加复杂。

此外,功耗与热量是紧密相关的,芯片内部的热量无法有效散出时,可能会导致芯片的过热,从而影响性能甚至烧毁器件。因此,如何设计高效的热管理系统,避免功耗过高带来的热效应,也是7纳米工艺面临的关键问题之一。

三、解决方案与未来发展

尽管突破7纳米工艺存在诸多挑战,但半导体行业已经通过多个创新解决方案取得了初步突破:

极紫外光刻技术(EUV):EUV光刻技术正在逐步成熟,未来它将成为实现更小制程节点(如5纳米、3纳米甚至更小)的主要技术手段。

三维集成电路(3D IC):为了突破平面布局的物理极限,许多半导体公司开始研究三维集成电路(3D IC)技术,通过垂直堆叠晶体管、存储器等元件,来进一步提升芯片的集成度和性能。

新型半导体材料:除了硅,业界还在探索其他新型半导体材料,例如碳纳米管、石墨烯等,以解决传统硅材料在尺寸缩小过程中遇到的物理限制。

量子计算:虽然量子计算离广泛应用还有一段距离,但作为未来计算架构的潜在替代方案,量子计算有望打破传统硅基计算的瓶颈。

四、总结

突破7纳米工艺的难度不仅仅是技术层面的突破,更涉及到材料科学、物理学、化学和工程学等多个学科的综合应用。

-

工艺

+关注

关注

4文章

591浏览量

28772 -

光刻技术

+关注

关注

1文章

146浏览量

15814 -

7纳米

+关注

关注

0文章

55浏览量

14857

原文标题:7纳米晶圆制造工艺为什么那么难?

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

康耐视AI解决方案助力打造高效电动汽车生产线

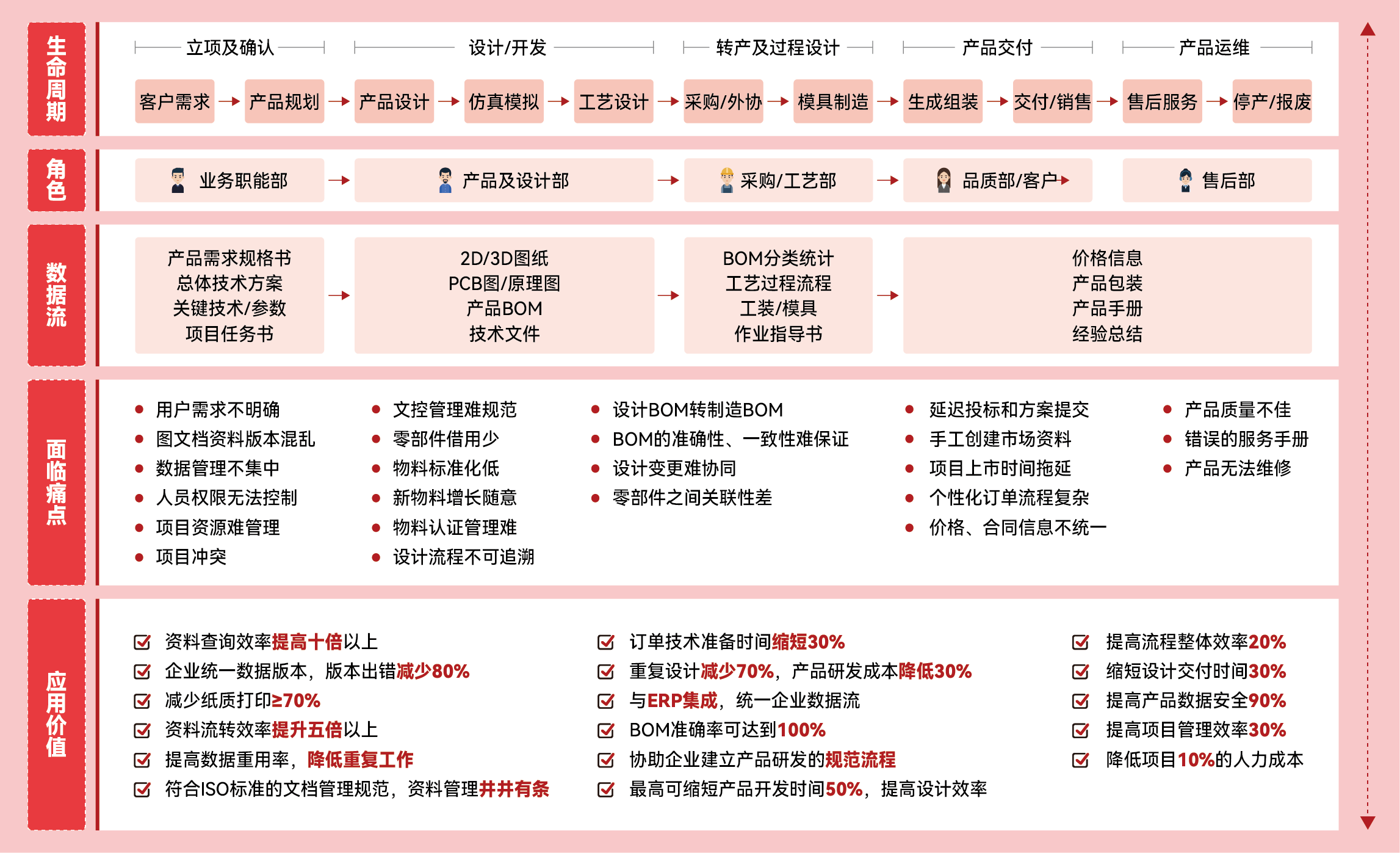

PLM制造业解决方案:应对挑战,提升效率与竞争力

边缘计算的技术挑战与解决方案

施耐德电气全方位配电服务解决方案助力轻松应对各种挑战

FPGA设计面临的挑战和解决方案

瑞萨基于IEC61508的功能安全解决方案介绍(1)

深圳比创达电子|EMI一站式解决方案:提升企业电磁兼容性的路径.

underfill工艺常见问题及解决方案

7纳米工艺面临的各种挑战与解决方案

7纳米工艺面临的各种挑战与解决方案

评论