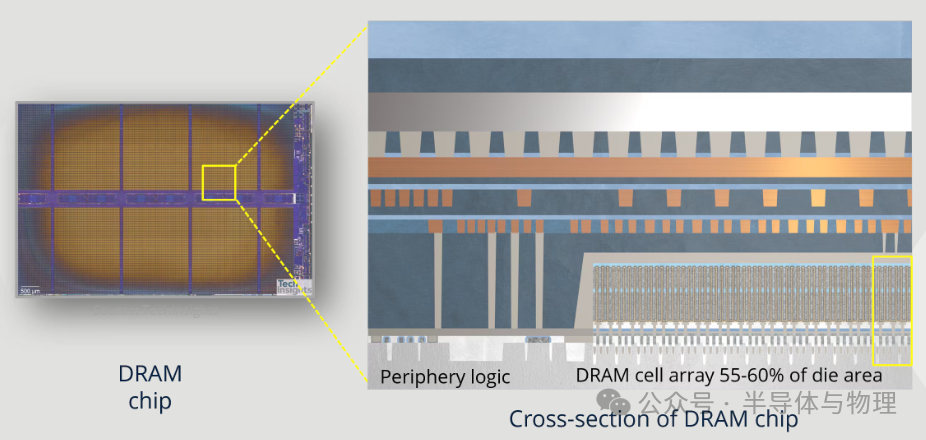

本文介绍了动态随机存取器DRAM的基本结构与工作原理,以及其在器件缩小过程中面临的挑战。

DRAM的历史背景与发展

动态随机存取器(Dynamic Random Access Memory,简称DRAM)是计算机系统中用于短期数据存储的一种半导体存储器。它由IBM的研究员罗伯特·H·登纳德(Robert H. Dennard)于1967年发明,并在随后的几十年间成为了计算机和电子设备中最常用的内存类型之一。由于其高密度、低成本的特点,DRAM被广泛应用于个人电脑、服务器、移动设备等各种计算平台。

DRAM的基本构造与工作原理

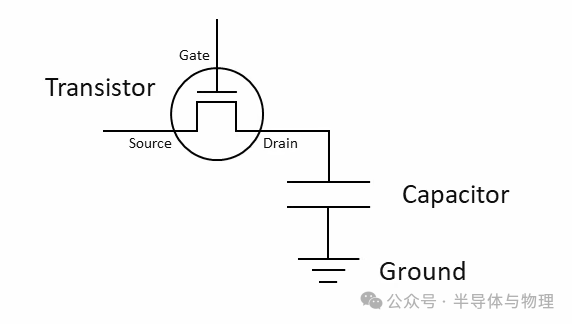

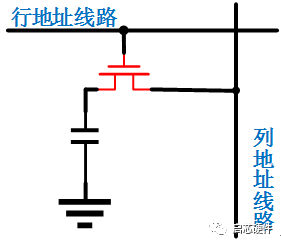

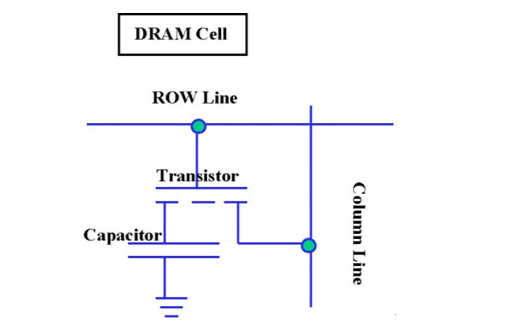

一个典型的DRAM单元包含两个主要组件:一个作为访问的晶体管和一个用于数据存储的电容器。这种设计允许每个存储单元仅需占用极小的空间,从而实现高密度的数据存储。

访问晶体管(Access Transistor):这是一个MOSFET晶体管,负责控制外部电路是否可以读取或写入到相连的电容器中。当晶体管导通时,它可以将电荷加载到电容器上或者从电容器中释放电荷;而当晶体管关闭时,则阻止任何电流通过,保持电容器中的电荷状态不变。

存储电容器(Storage Capacitor):电容器是用来实际保存信息的地方。电容器充电代表逻辑值“1”,未充电则代表逻辑值“0”。为了确保数据的正确性,电容器需要定期刷新,这是因为电容器会逐渐失去其上的电荷,这就是所谓的“动态”特性。

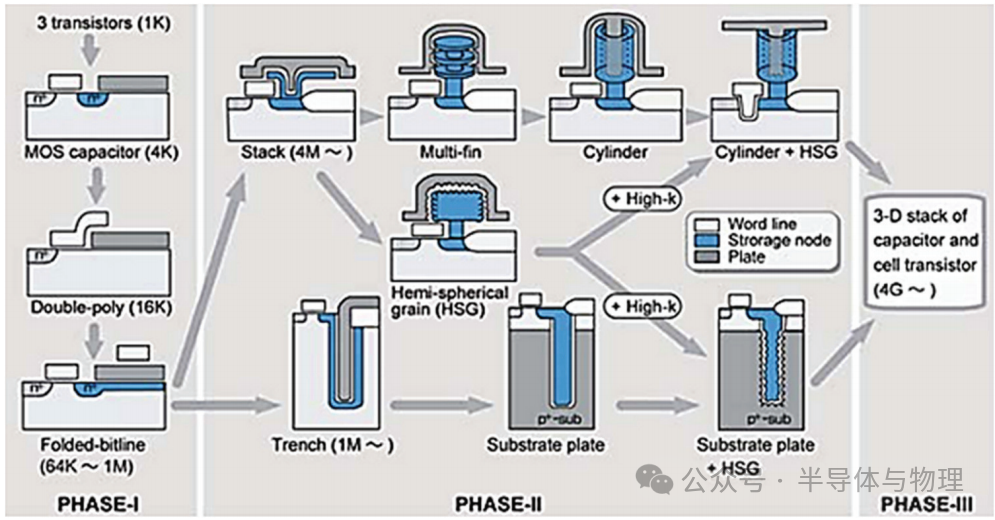

最初,这些器件都是平面型的,使用二氧化硅作为栅极绝缘层和电容器介质。随着技术的进步,为了在减小特征尺寸的同时保持足够的电容值C不变,工程师们开始采用高介电常数(high-k)材料如氮化硅来替代传统的二氧化硅,以及使用氧化物/氮化物/氧化物(ONO)堆栈来解决应力问题。

DRAM三维结构的引入

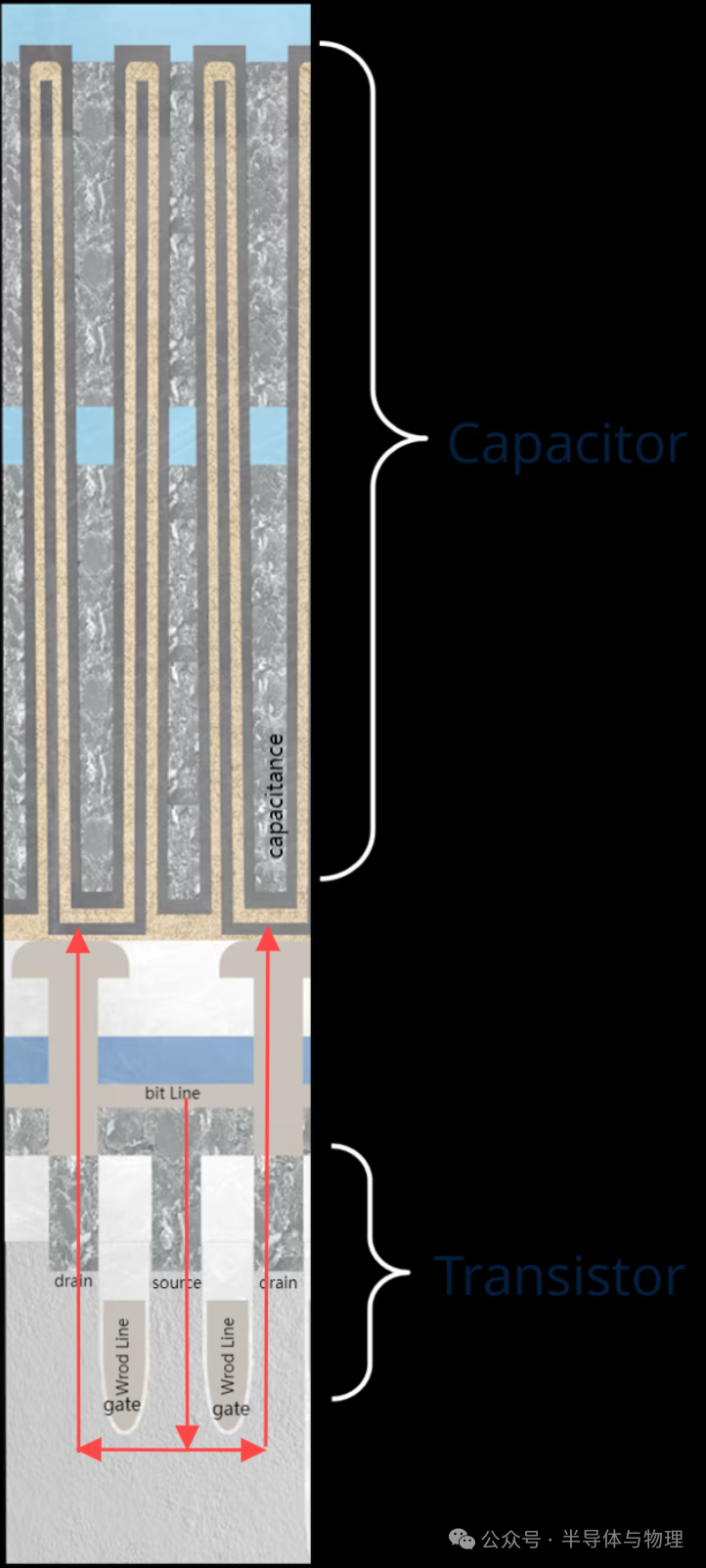

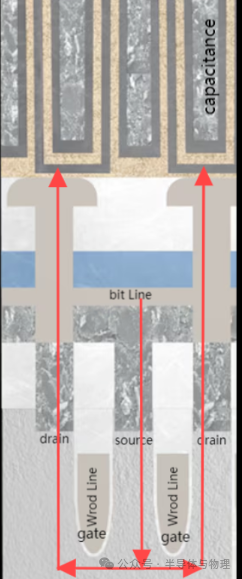

随着工艺节点的不断缩小,特别是进入80纳米以下后,短沟道效应导致了更高的源漏泄漏电流和更短的数据保留时间。为了解决这些问题,DRAM访问晶体管从平面结构转变为三维结构,例如引入了凹槽栅极(Recessed Gate, RG)晶体管和埋入式字线(Buried Word-Line, BWL)技术。这些改进增加了通道长度,有助于减少泄漏并维持数据保持时间,同时通过增加通道宽度提高了驱动电流,且不需要增大器件的特征尺寸。

此外,为了进一步压缩存储单元面积,人们还开发出了各种形状复杂的电容器,如深沟槽电容器和堆叠柱状电容器。前者利用硅片内部的空间构建电容器,后者则是将多个电容器垂直堆叠起来,以此来提高单位面积内的电容值而不必增加芯片的物理尺寸。

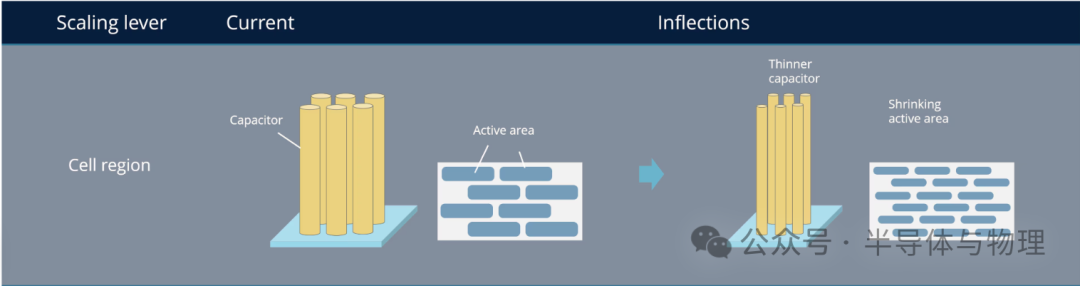

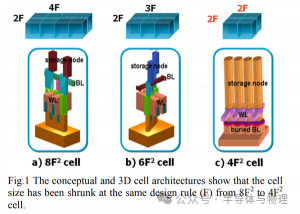

缩放挑战与解决方案 随着制造技术的发展,DRAM的特征尺寸不断缩小,但随之而来的是新的挑战。例如,当DRAM的特征尺寸按照的比例缩小时,如果要保持电容C、介电常数k和距离d不变,则圆柱形电容器的高度必须相应地增加,以补偿直径上的减少。这意味着长宽比(aspect ratio)会加倍,给制造带来了新的挑战。因此,研究人员一直在寻找具有更高介电常数的新材料,以降低所需电容值,并优化晶体管的设计以减少关闭状态下的泄漏电流。

6F2架构DRAM简介

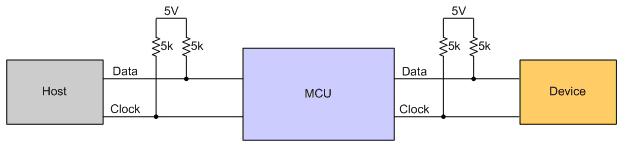

如今业界所制造最先进的DRAM采用的是6F2架构,就是每个最小bit的单元占6倍最小线宽的的平方面积。即一个BitLine可以为两个电容充电,如下图红色箭头bit Line电流从source由Word Line gate流向drain,从而对电容进行充电或放电。

参考文献:[1]DRAM [2]3D IC devices, technologies, and manufacturing / Hong Xiao.

-

DRAM

+关注

关注

40文章

2309浏览量

183420 -

存储器

+关注

关注

38文章

7481浏览量

163751

原文标题:DRAM(动态随机存取器)

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

DRAM的工作原理 DRAM存储数据和读取数据过程说明

【内存知识】DRAM芯片工作原理

电磁继电器的构造及工作原理

MOS管的构造/工作原理/特性

DRAM存储器的工作原理详细介绍

硬盘的工作原理和内部构造

DRAM的基本构造与工作原理

DRAM的基本构造与工作原理

评论