主要介绍了一种用于完整的直接数字频率合成器 AD9850 的分立、低相位噪声、125MHz 晶振解决方案,具体内容如下:

*附件:用于完整的直接数字频率合成器AD9850的分立、低相位噪声、125MH晶振.pdf

- 背景 :AD9850 是一款低成本高速数字频率合成器,但使时钟频率保持在最高值 125MHz 存在挑战,市场上缺乏低成本商用时钟振荡器,而巴特勒振荡器电路是一种成本较低且相位噪声性能较好的替代方案。

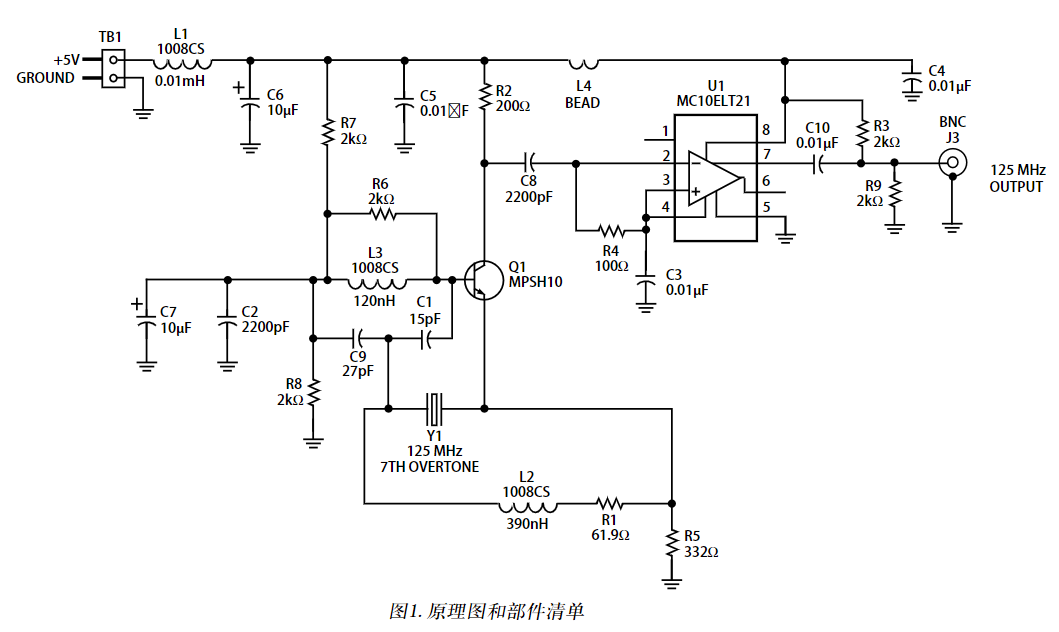

- 巴特勒振荡器电路实现

- 部件与成本 :采用单电源(+5V)供电,集成 TTL 输出级,部件单位成本 20 至 25 美元,包括芯片电容、芯片电阻、芯片电感等,Q1 可选用高频 NPN 晶体管,晶体为第七泛音、串联谐振模式,PECL 转 TTL 转换器 U1 采用摩托罗拉 ECLinPS “Lite” 表面贴装器件。

- 电路描述 :L2/R1 与晶体杂散电容谐振防止寄生振荡,含 L3 的振荡电路谐振频率接近 125MHz,R6 降低振荡电路 Q 防止自激振荡及频率对准误差,PECL 转 TTL 转换器输出交流耦合至 2.5V 中点电压,振荡器输出配置需高负载阻抗以维持偏置电压和信号摆幅,若需 TTL 电平可移除相关元件并焊接跳线。

- 相位噪声性能 :参考振荡器相位噪声与 AD9850 残余相位噪声构成总相位噪声,AD9850 在特定条件下残余相位噪声为 -134dBc,巴特勒振荡器对 AD9850 输出信号相位噪声贡献在不同频率条件下有所变化,随着 DDS 输出频率在参考振荡器频率中占比提高,振荡器贡献加大。

- 原型时钟振荡器特性 :采用 2"×2" 双面铜箔板,驱动 50Ω 负载输出为 2V p-p,驱动高阻抗负载输出略低于 4V p-p,全部采用贴片元件,数字示波器输出显示了其输出特性。

审核编辑 黄宇

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

合成器

+关注

关注

0文章

273浏览量

25353 -

晶振

+关注

关注

34文章

2858浏览量

67994 -

AD9850

+关注

关注

6文章

70浏览量

28305 -

数字频率

+关注

关注

0文章

17浏览量

12886

发布评论请先 登录

相关推荐

DP83869HM如何才能输出125MHz的时钟?

我司新开发一款产品,用到TI的DP83869HM这颗芯片,现在我们需要CLK_OUT(PIN40)输出125MHz时钟,看手册是可以有25MHz和125MHz两种频率的时钟输出。

我

发表于 12-03 06:11

FlexDDS-NG直接数字信号合成器(DDS)/波形发生器

盛铂科技FlexDDS-NG是一种单台机箱最多可达12个通道相位连续直接数字信号合成器 (DDS)。其输出频率可达400

14位,3.3V CMOS直接数字合成器-CBM99D10

CBM99D10BQ:1G高精度DDS,助力北斗信号接收CBM99D10BQ是一款内置14位DAC的直接数字频率合成器(DDS),支持高达1GSPS采样速率,可生成400MHz正弦波形

dds数字频率是怎么合成的 DDS数字频率信号发生器的设计

DDS(Direct Digital Synthesizer,直接数字频率合成器)是一种广泛应用于现代电子系统的频率合成技术,它通过

组合两个 LMX2820 合成器输出,以改善相位噪声应用说明

电子发烧友网站提供《组合两个 LMX2820 合成器输出,以改善相位噪声应用说明.pdf》资料免费下载

发表于 09-12 09:25

•1次下载

单节功率合成器工作原理是什么

是单节功率合成器的核心功能之一。在实际应用中,我们通常需要将多个功率放大器的输出信号进行合成,以实现更高的输出功率和更好的信号质量。信号合成的原理主要基于以下几个方面: 1.1 相位

锁相环频率合成器的特点和应用

锁相环频率合成器(Phase-Locked Loop Frequency Synthesizer, PLLFS)是一种利用锁相环(Phase-Locked Loop, PLL)技术实现频率合成

直接数字频率合成(DDS)技术的原理及优势

直接数字频率合成( DDS)是一种利用数字技术生成模拟信号的技术,广泛应用于电子测试设备、无线通信、数字信号处理等领域。

频率合成器和锁相环的区别有哪些?

频率合成器和锁相环是两种常见的电子设备,用于生成稳定的频率信号。尽管它们的功能都是产生特定频率的信号,但它们在工作原理和应用方面有着明显的区别。

完整的直接数字频率合成器 AD9850 的分立、低相位噪声、125MHz 晶振解决方案

完整的直接数字频率合成器 AD9850 的分立、低相位噪声、125MHz 晶振解决方案

评论