导读

在电路设计中,为了降低成本而忽视ESD防护和隔离设计可能导致严重后果。本文将探讨因不当添加元件而引发的电路问题,并逐一解析这些问题,提供实用的解决方案,以确保电路设计的可靠性和稳定性。

电路设计中,有的为了降低成本,没有进行任何ESD防护和隔离设计,这是不行的,为了提高可靠性和稳定性,增加保护器件,或者增强驱动能力是常用方法。但稍有不慎,就有可能适得其反,在一些关键电路上,增加一些元件后,会带来很大的负面影响:

- 如果添加的元件对电路时序产生了影响,这样的器件最好不要加。

- 在总线时钟信号线上增加了ESD保护器件,但器件选型没做好容性控制,这样会引起时钟信号波形畸变,影响正常通信;

- 在总线源端加22Ω电阻也是常用设计手段,但这一定要考虑总线整体电路。如果核心板上已经放置了22Ω的电阻,则在底板上则不需要再串联电阻,否则也会引起工作异常。

开机阶段闪屏

开机阶段闪屏

1. 现象描述

仪器设备在上电后在BootLoader和内核两个阶段出现闪屏现象。

先从软件方面着手,通过延迟打开背光,但并未完全解决,通过示波器观察,背光控制部分有明显延迟。

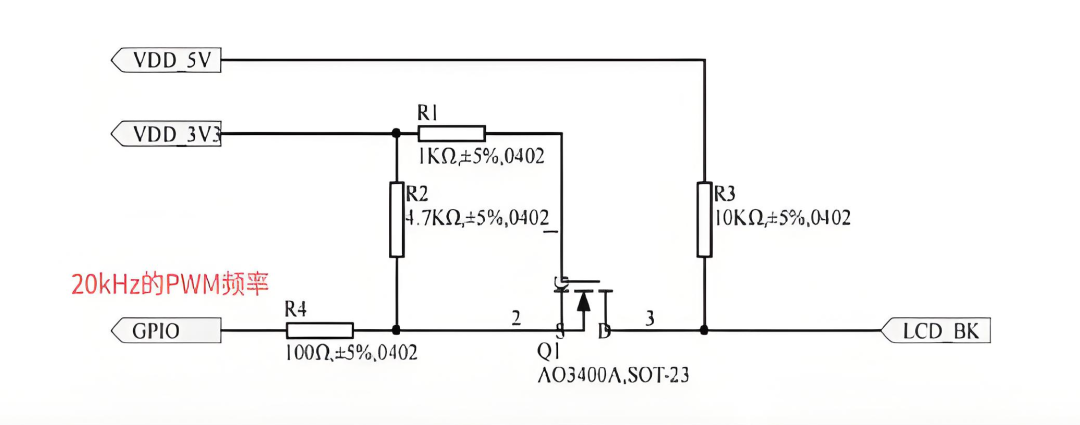

再从硬件着手分析,拿到的设备背光控制电路如图1所示,通过示波器观察,在设备上电时LCD_BK引脚会有一个高电平脉冲,之后维持低电平,最后阶段为20KHz的PWM波。

图1 客户的LCD背光控制电路

2. 分析过程

根据以上现象基本可以判断为上电时序问题,通过测量也可以发现VDD_5V早于VDD_3V3上电。当VDD_5V上电时,VDD_3V3未上电,系统没有启动,GPIO处于高组态,因此Q1的1、2引脚电平相同,Q1处于关断状态,LCD_BK信号会被R3拉高,导致背光被点亮,而当系统启动后,GPIO会输出低电平,控制背光关闭,由此出现屏闪现象。

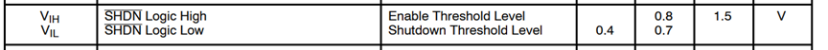

查看背光驱动芯片手册,使能引脚高电平阈值为1.5V,如图2所示,无需进行电平转换,元件Q1是多余的,直接使用3.3V GPIO既可驱动。

图2 使能引脚高电平阈值

3. 解决措施

去掉R1、R2、R3和Q1,并且把Q1的2、3引脚短接,设备上电启动时不会再出现闪屏现象。

TF卡无法识别

TF卡无法识别

1. 现象描述

这现象比较常见于TF卡所有信号线都加上了ESD保护器件的情形,常见问题为ESD器件选型不正确。

2.分析过程

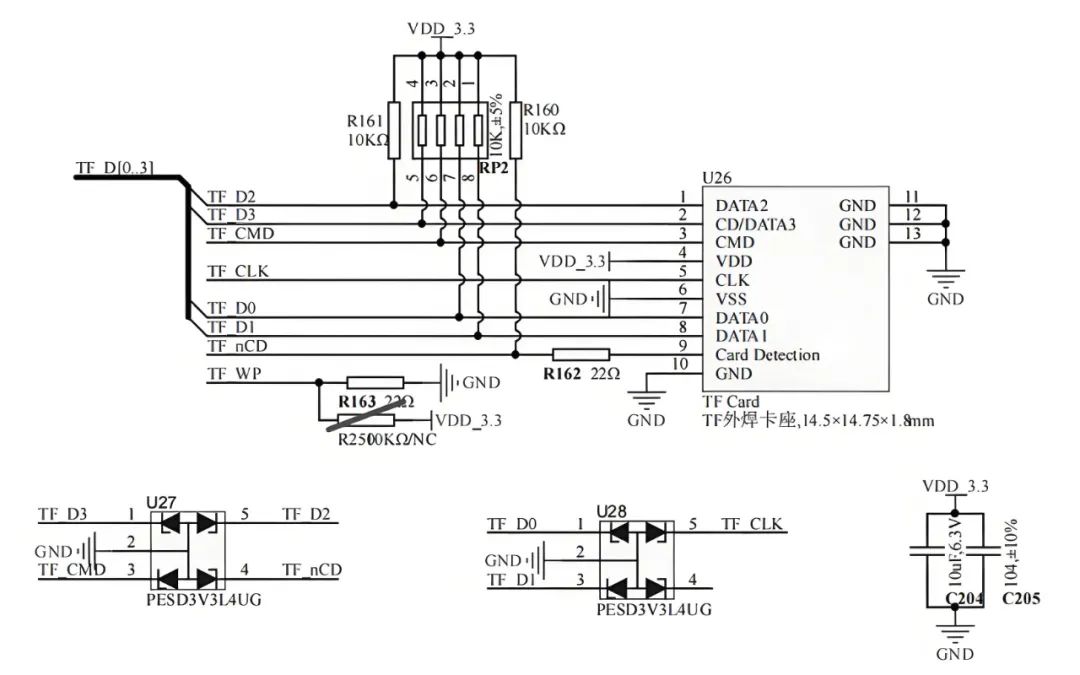

以图3所示的原理图为例进行分析。

图3 TF卡一般电路图

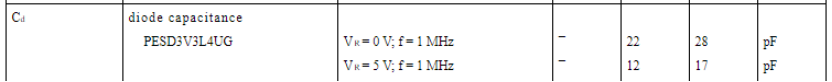

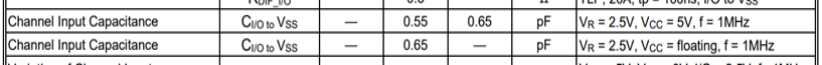

SD2.0对ESD器件寄生电容的要求为小于9pF,首先查看该ESD器件(PESD3V3L4UG)数据手册,发现该ESD器件寄生电容最高可到28pF(参见图 4),超过了SD2.0对寄生电容的要求。

图4 PESD3V3L4UG的寄生电容3. 解决措施断开CLK线上的ESD器件,或者换用小寄生电容的DT1446-04S-7,该器件寄生电容仅为0.65pF(参见图5),替换上去后TF卡正常识别。

图5 DT1446-04S-7的寄生电容

以太网匹配电阻

以太网匹配电阻

1. 现象描述

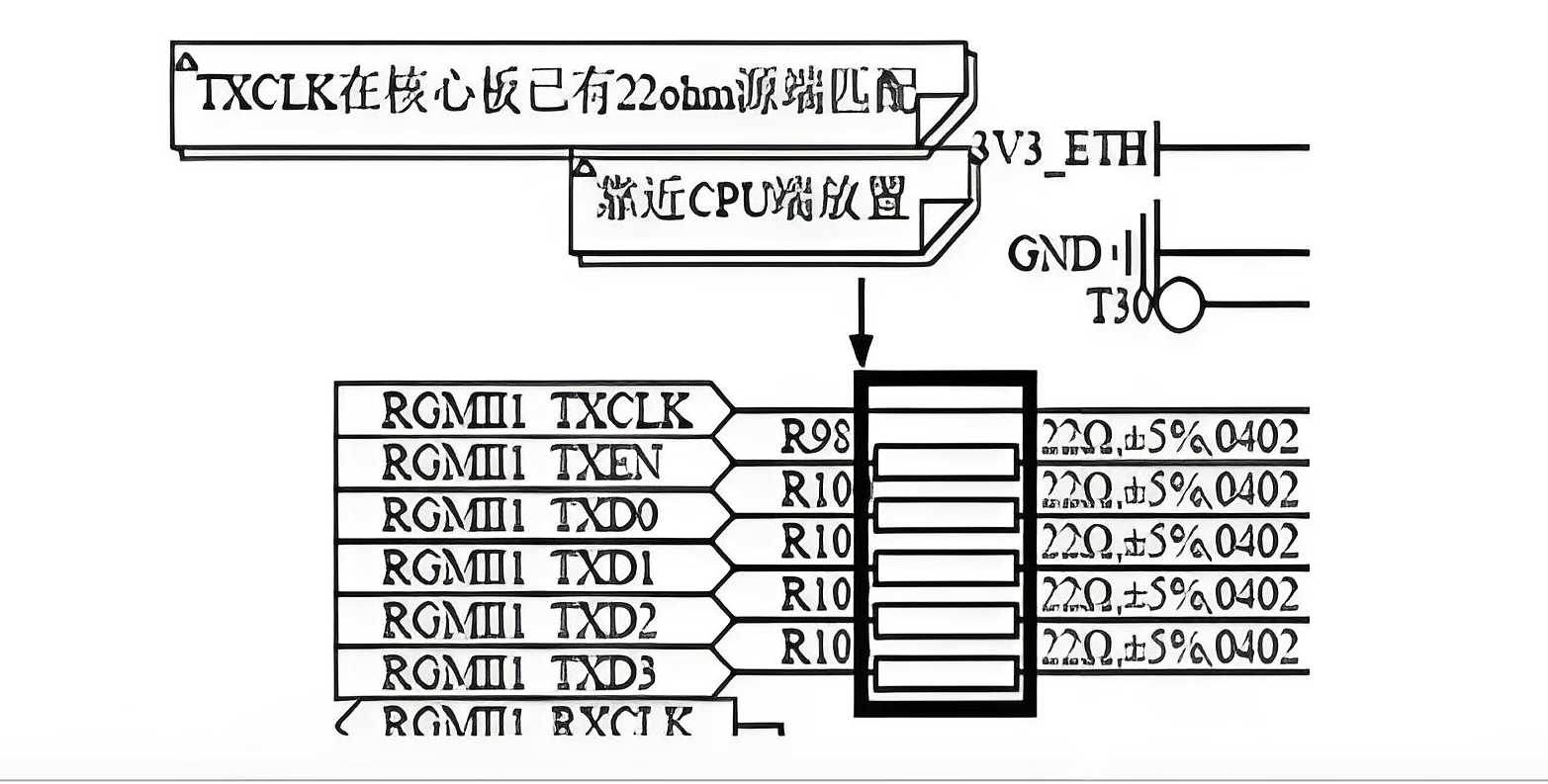

核心板上以太网TX_CLK信号线已有22Ω的源端电阻,客户在底板也加了22Ω的匹配电阻,引起以太网通信不稳定。

2. 分析过程

将同一块核心板插到评估板上,以太网通信正常,基本定位是底板原因。而后检查底板以太网电路原理图,发现TX_CLK引脚串接了22Ω匹配电阻。而致远电子官网给出的以太网参考电路里没有加匹配电阻,显然用户没有按照参考电路来设计。

图6 新能源

3. 解决措施

将底板的22Ω电阻换为0Ω,以太网即可正常通信。

4. 总结

以太网PHY和处理器端的数据线和控制信号要注意阻抗匹配,避免信号反射。在设计原理图时,一般建议源端串联22~33Ω电阻。但是,部分核心板已经在源端串接匹配电阻,设计底板时就不需要串接匹配电阻。使用核心板开发新产品时,建议参考致远电子官方硬件设计参考电路。

-

元器件

+关注

关注

112文章

4707浏览量

92198 -

嵌入式

+关注

关注

5082文章

19103浏览量

304693 -

电路设计

+关注

关注

6673文章

2450浏览量

204077 -

仪器设备

+关注

关注

1文章

104浏览量

10728

发布评论请先 登录

相关推荐

求嵌入式linux学习笔记

如何在嵌入式操作系统ARM Linux中实现ZLG7290的驱动?

嵌入式系统笔记

嵌入式Linux驱动笔记--转自风筝丶

从客户需求视角去认识ZLG | 为用户提供工业自动化及嵌入式领域生态产品

为何ZLG致远电子要推出LGA嵌入式核心板?

ZLG嵌入式笔记(连载08) | 那些不能随便添加的元器件

ZLG嵌入式笔记(连载08) | 那些不能随便添加的元器件

评论