本文介绍SiGe外延工艺及其在外延生长、应变硅应用以及GAA结构中的作用。

在现代半导体技术中,随着器件尺寸的不断缩小,传统的硅基材料逐渐难以满足高性能和低功耗的需求。SiGe(硅锗)作为一种复合材料,因其独特的物理和电学特性,在半导体芯片制造中得到了广泛应用。

SiGe外延工艺的重要性

1.1 外延工艺简介

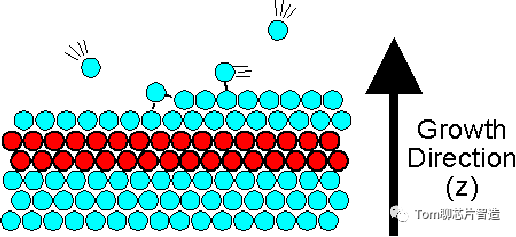

外延(Epitaxy, 简称Epi)是指在单晶衬底上生长一层与衬底具有相同晶格排列的单晶材料。外延层可以是同质外延层(如Si/Si),也可以是异质外延层(如SiGe/Si或SiC/Si)。实现外延生长的方法有很多,包括分子束外延(MBE),超高真空化学气相沉积(UHV/CVD),常压及减压外延(ATM & RP Epi)等。本文主要介绍广泛应用于半导体集成电路生产中衬底为硅材料的硅(Si)和锗硅(SiGe)外延工艺。

1.2 SiGe外延的优势

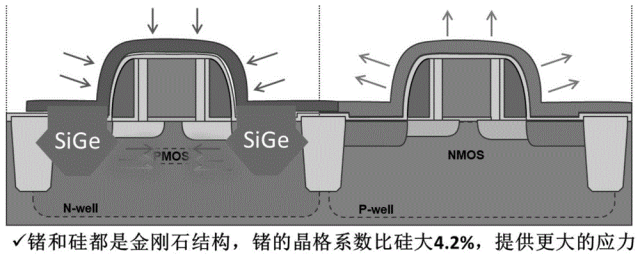

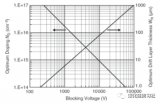

通过在外延过程中引入一定比例的锗(Ge),形成的SiGe单晶层不仅能够降低带隙宽度,还可以增大晶体管的特征截止频率fT(cut-off frequency),这使得它在无线和光通信高频器件方面应用十分广泛。此外,在先进的CMOS集成电路工艺中,利用Ge与Si的晶格常数失配(约4%)引入的晶格应力来提高电子或者空穴的迁移率,从而增大器件的工作饱和电流以及响应速度。

完整的SiGe外延工艺流程

2.1 预处理

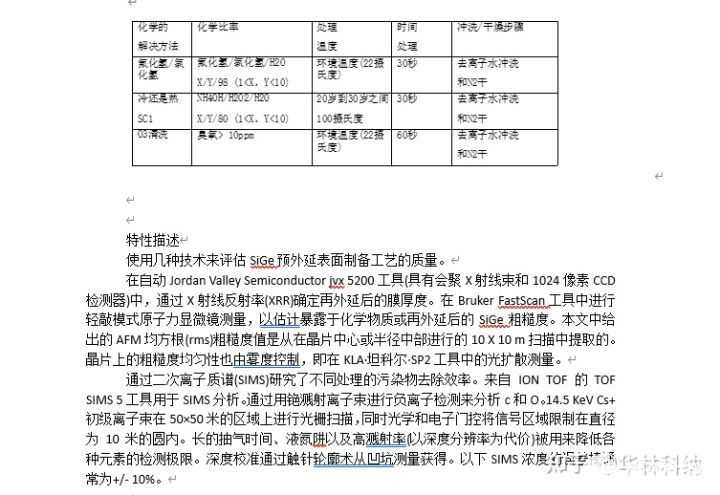

根据需要实现的工艺结果对硅片进行预处理,主要包括去除表面的自然氧化层及硅片表面的杂质。对于重掺杂衬底硅片,则必须考虑是否需要背封(backseal)以减少后续外延生长过程中的自掺杂现象。

2.2 生长气体与条件

含硅气体:硅烷(SiH₄)、二氯硅烷(DCS, SiH₂Cl₂)和三氯硅烷(TCS, SiHCl₃)是最常用的三种含硅气体源。其中,SiH₄适用于低温全外延工艺,而TCS因其快速生长率被广泛用于厚硅外延层的制备。 含Ge气体:锗烷(GeH₄)是添加锗的主要来源,它与硅源一起使用以形成SiGe合金。 选择性外延:通过调节外延沉积和原位刻蚀的相对速率大小来实现选择性生长,所用气体一般为含氯(Cl)的硅源气体DCS,利用反应中Cl原子在硅表面的吸附小于氧化物或者氮化物来实现外延生长的选择性;由于SiH₄不含Cl原子而且活化能低,一般仅应用于低温全外延工艺;而另外一种常用硅源TCS蒸气压低,在常温下呈液态,需要通过H₂鼓泡来导入反应腔,但价格相对便宜,常利用其快速的生长率(可达到5 μm/min)来生长比较厚的硅外延层,这在硅外延片生产中得到了广泛的应用

应变硅在外延层的应用

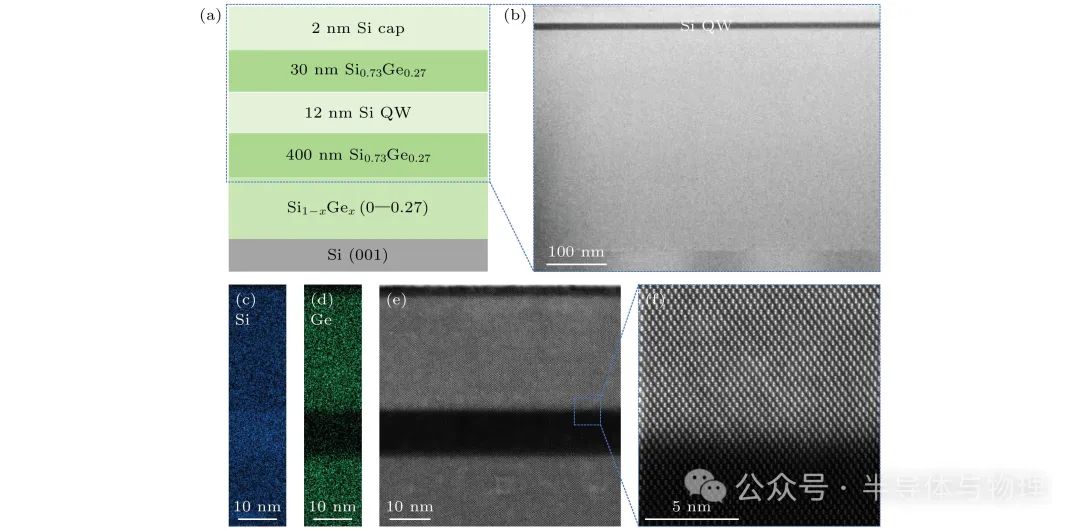

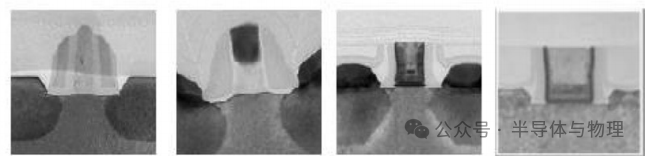

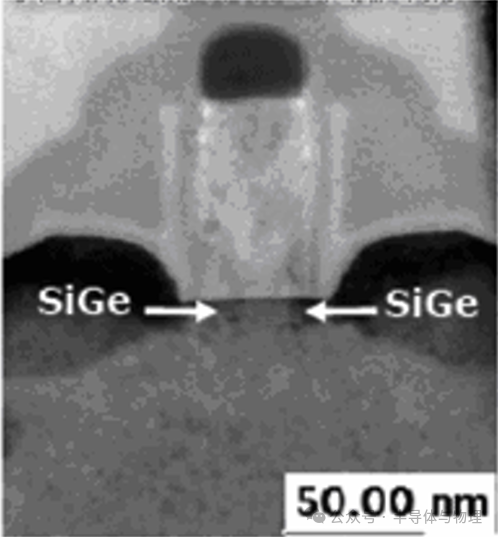

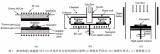

在外延生长过程中,在松弛(relaxed)的SiGe层上面外延一层单晶Si,由于Si与SiGe晶格常数失配,Si单晶层会受到下面SiGe层的拉伸应力,这使得NMOS晶体管中的电子迁移率得到显著提升。这种技术不仅提高了饱和电流(Idsat),还提升了器件响应速度。对于PMOS器件,则是在源漏极区域刻蚀后外延SiGe层来引入对沟道的压应力(compressive stress),以提高空穴(hole)的迁移率(mobility),实现了饱和电流的增加。

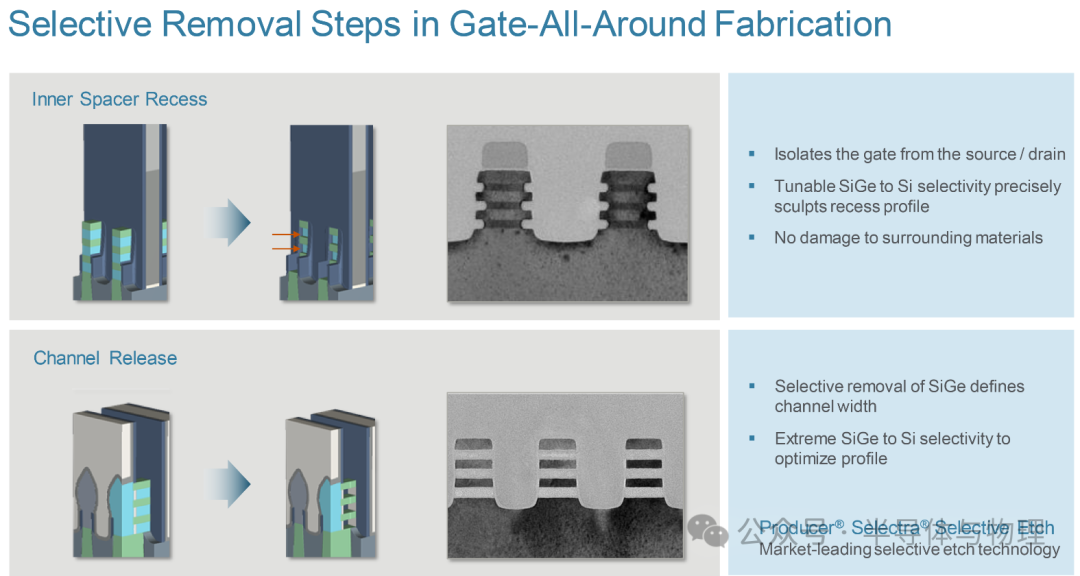

SiGe作为GAA结构中的牺牲层

在环绕栅极纳米片(Gate-All-Around, GAA)晶体管制造中,SiGe层扮演着牺牲层的角色。通过高选择性的各向同性刻蚀技术,如准原子层刻蚀(quasi-ALE),可以精确地去除SiGe层,形成纳米片或纳米线结构。

-

半导体

+关注

关注

334文章

27285浏览量

218000 -

工艺

+关注

关注

4文章

592浏览量

28779 -

SiGe

+关注

关注

0文章

63浏览量

23462

原文标题:芯片制造中的SiGe

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

SiGe外延工艺及其在外延生长、应变硅应用及GAA结构中的作用

SiGe外延工艺及其在外延生长、应变硅应用及GAA结构中的作用

评论