前言

现在的高速设计中我们不能只去单独的分析信号完整性,电源完整性或者是EMC, 而是要整体分析,才能保证设计的成功。

背景问题:当某层上的信号跨过相邻参考平面的分割区域时,讨论信号完整性总是会引起争论。有人说信号不应该跨分割,因为这将会增加串扰,并且很有可能过不了EMC,有人说如果小心设计层叠结构和电源/地平面上分割缝隙的宽度,应该不会有问题…那么应该是什么样的呢?当然最好的回答就是“it depends!”,本文就来讨论一下信号通过分割平面时的情况。

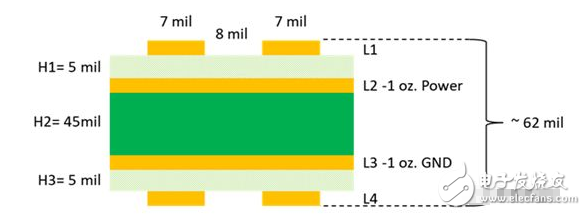

首先看一个典型的四层PCB层叠结构,总厚度是62mil,表层为信号层,内层为平面层,走线规则7/8mil,差分阻抗100ohm,单端阻抗56ohm。

图1

在现代电子产品设计中,一个产品存在多种电源轨是很正常的,这意味着在一个四层板中,电源平面肯定会被分割,因此布线的时候存在的跨分割也就不可避免。

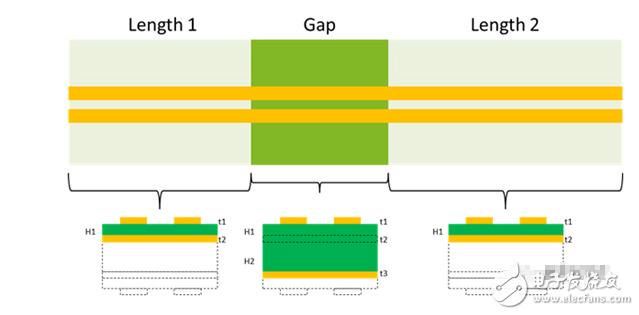

假设有一对表层的传输线跨过相邻层50mil宽的缝隙,如图所示为微带线在通过缝隙前后的横截面,从表层到参考电源层的介质厚度H1。由于缝隙处没有相邻的电源参考平面,下一个参考平面是地,与底层相邻,因此,缝隙处的介质厚度等于H1加上1oz厚的电源层,再加下一个介质层H2.如果电源层的厚度是1.2mil,那么间隙部分总的介质就是51.2mil。

该拓扑的一阶近似是具有两种不同阻抗的三段传输线段的组合。第一段和最后一段都是100ohm的差分阻抗和56ohm的单端阻抗,而缝隙部分的传输线的差分阻抗为134ohm,单端阻抗为103ohm,其阻抗比其他部分高,所以信号在这里是发生正反射。反射的高度和宽度是对应信号上升时间和缝隙几何形状的函数。上升时间越快,缝隙越宽,造成较的反射越大。图3为仿真结果:

图2

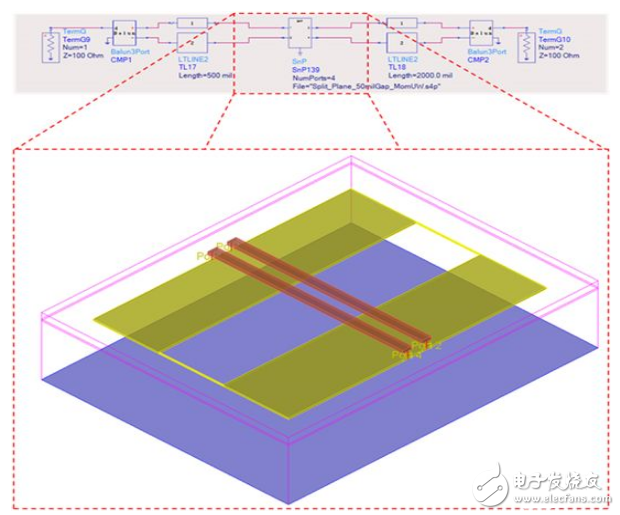

第一段和第三段传输线都是用的TLines-LineType的2D模型进行仿真求解(ADS),缝隙处的传输线采用的是3D电磁场求解器(Momentum或者EMPro)仿真获得,目的是为了得到信号通过时的电磁场效应,介质都是一样的。将S参数提取出来并用于原理图中。

拓扑的总长度为2.65inch,第一段传输线的长度L1为500mil,第三段传输线的长度L1为2inch,3D部分被分成三个50mil,以方便调整缝宽,并确保总长度保持不变。

两个缝隙宽度用来比较缝隙大小的影响。电源平面之间有50mil的缝隙是常见的,这里用作最坏的情况。5mil缝隙是最佳的情况,这也是传输线到焊盘的典型最小值。

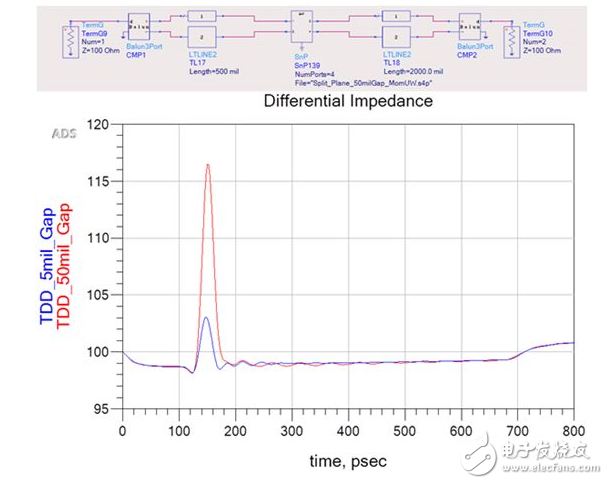

图3

从port1端加入差分激励源,差分阻抗的比较如图4所示,为了方便查看2端口阻抗,使用巴伦转换器,将4端口转换成2端口。红色的是50mil gap的结果,与5mil gap的结果(蓝色)相比有着较高的阻抗不连续性。这是因为发射脉冲的高度是由上升时间和间隙宽度共同决定的,由于上升时间在空间长度上要比间隙宽度小,仅改变上升时间达不到阻抗不连续的最大值。下面通过仿真来证明。

图4

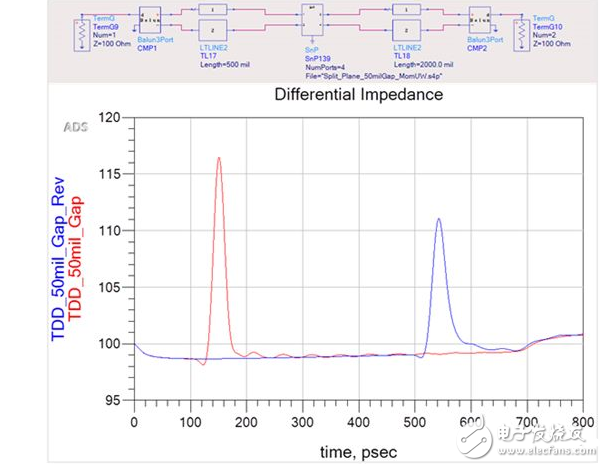

从port2端加入激励源,缝隙为50mil,与从port1端输入信号比较,如下图。由于gap之前有2.05inch的延迟,再加上传输线的损耗,信号边沿会较慢。正如预期的一样,反射的幅度的确较低。

图5

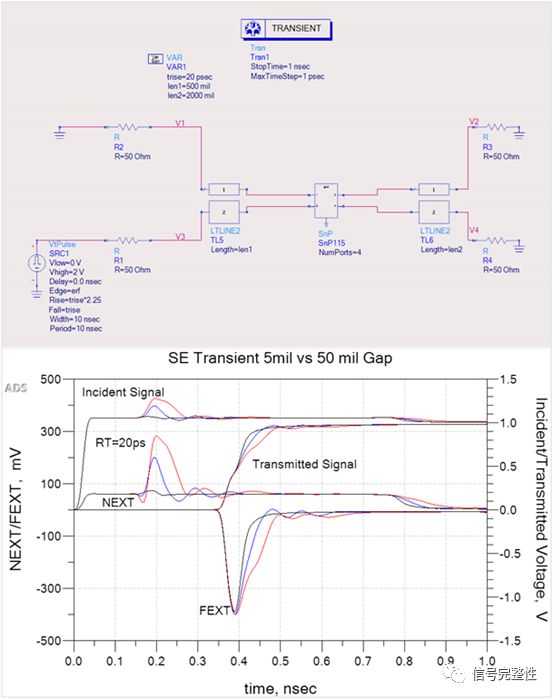

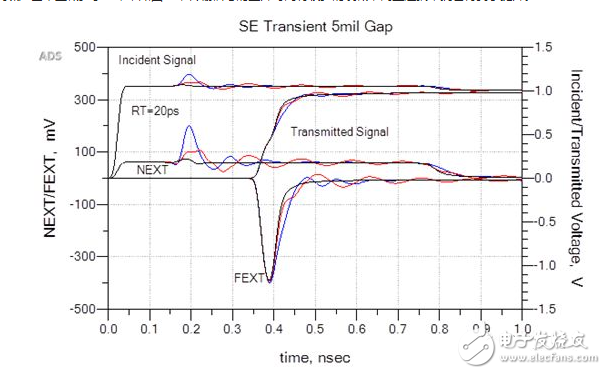

下面是对单端情况的分析,如图所示,红色曲线是gap为50mil,蓝色为5 mil,黑色为没有gap的情况。信号上升时间是20ps,同没有gap的情况相比,gap为50mil时的反射电压最高,此时传输信号的上升时间衰减,使传输线延迟略微增加。

三种情况都可以看到典型的近端串扰和远端串扰曲线变化。通过缝隙时,传输线间的紧耦合,使得较高的反射表现为较大的近端串扰。

图6

在50mil gap时近端串扰脉冲明显的增大,但是远端串扰却仅仅增大了一点点。与近端串扰电压不同,远端串扰电压的峰值随耦合长度而变化。在一定的时间延迟(TD)时,它的振幅在攻击线信号上升时间的50%左右时达到峰值。

同样的方式,攻击线的信号与远端串扰电压会耦合到受害线上,远端串扰和噪声又耦合回到攻击线,从而影响了上升时间。攻击线在远端的波形是远端串扰电压与原始信号电压的叠加,这时信号没有串扰。由于远端距离源端2.65inch,此时远端串扰已接近饱和。如果减少最后一段传输线的长度到100mil,如图7,更容易理解gap对远端串扰的影响。

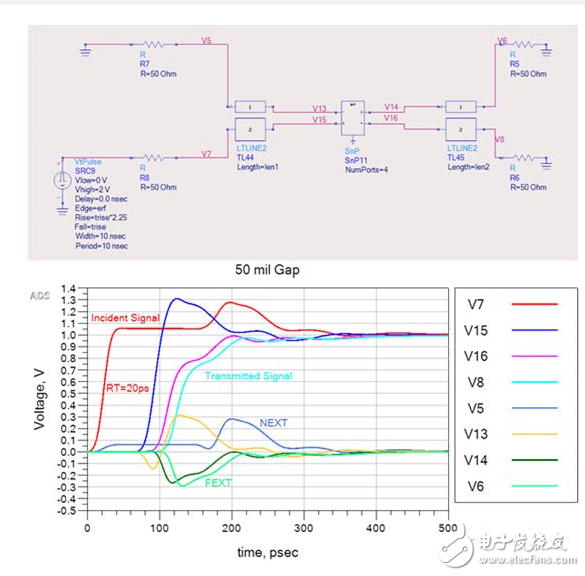

红色曲线是输入信号(V7),上升时间是20ps,蓝绿色曲线(V8)是传输信号到远端时的波形,亮蓝色(V5)是近端串扰,亮绿色(V6)是远端串扰,墨绿色(V15)是传输信号在经过TL44之后,结点V13的攻击信号。因为缝隙部的特性阻抗较高,在经过缝隙这段传输线上可以看到由反射增加引起的过冲。

橘色波形(V13)显示出远端负串扰脉冲,同V15端攻击线信号上升沿一致。近端串扰也同V15处的正反射一致。由于攻击信号在通过缝隙时会有延迟时,反射的额外电压摆幅增加了远端串扰脉冲的幅度,并且其反转形状反映了反射脉冲的形状,如墨绿色的波形(V14),然后远端串扰脉冲耦合回攻击信号并使上升时间衰减,直到离开耦合部分,如品红色曲线(V16)。

当攻击信号通过最后一段传输线TL45后,远端串扰脉冲幅度与线长成正比。因为最后一段传输线只有100mil,所以这里并未达到最大值。

本文的问题是:当信号通过分割平面时,传输信号会由于阻抗不连续引起正反射,反射的时间等于通过缝隙的时间,这就增加了信号的幅度及远端串扰脉冲的幅度,从而使传输信号上升时间变慢,与远端串扰的脉冲波形成比例。

图7

将分割平面和分割边缘处的多种回流一起考虑,此时产生了一个有效的槽型天线,并向外辐射噪声。为满足EMI FCC的B级辐射要求(3米场),辐射噪声在30-80MHz时,必须小于100mV/m,在216MHz-1GHz时小于200mV/m,在这些低电压下,EMC的失败不需要太多的电流。

微带线在通过分割平面时,由于回流路径不连续,又没有覆盖层,因此噪声会辐射到自由空间。可以想象能够通过3D仿真软件看到相邻参考平面上缝隙处返回电流的情况。

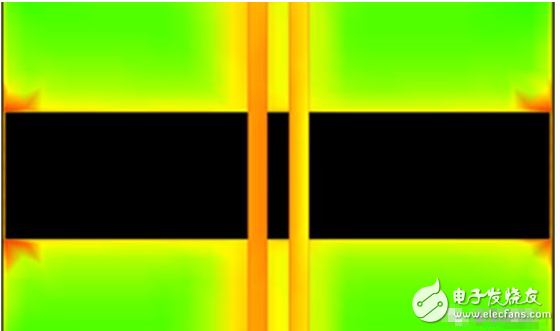

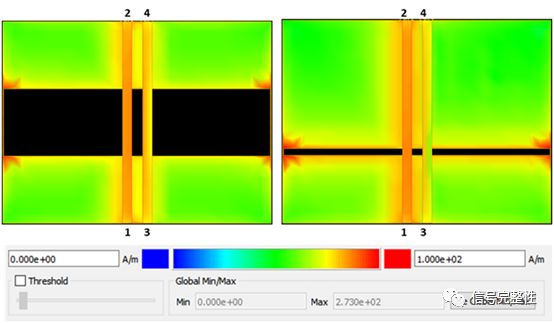

图8比较了单端信号在相邻参考平面上的返回电流密度,左边为一个4GHz正弦波通过50mil的缝隙,右边是5mil的缝隙。之所以选择4GHz信号,因为它是典型4层PCIe板上8 Gbps PCIe Gen 3的Nyquist频率。将驱动信号从端口1传到端口2,端口3、4上都做好端接,可以清楚的看到参考平面上返回电流密度在分割处的分布情况。

注意受害线在缝隙边缘处的电流密度略有增加。这表明相邻线上的返回电流造成了前边讨论的额外的远端串扰电压。仅从这个图中来看的话,单端线跨分割并不是一个好的方法。

图8

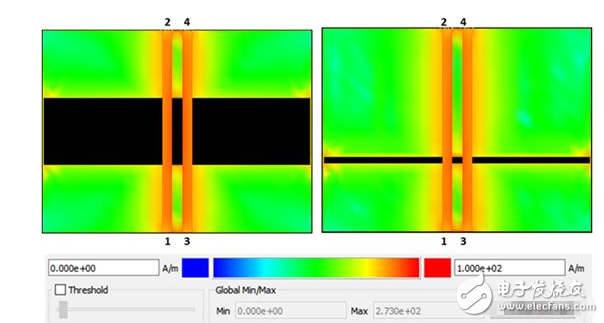

图9是4GHz的差分信号分别通过50mil(左)和5mil(右)缝隙时在参考平面上的返回电流密度。可以看出,两个差分对之间最大的电流密度集中在分割边缘处,只有一小部分沿着缝隙传出去了。

图9

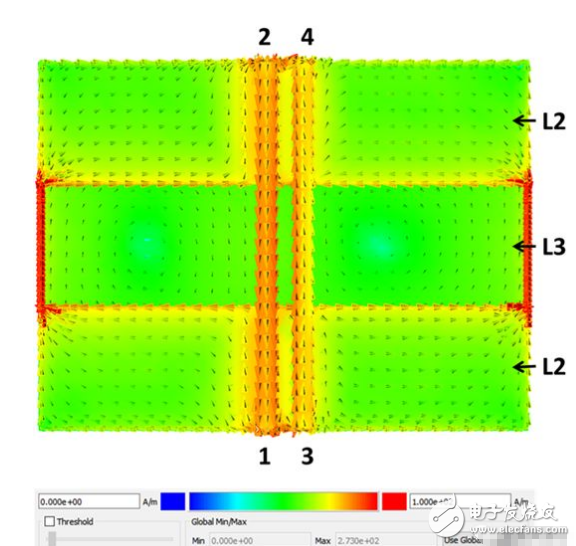

将单端信号从端口1输入到端口2,其他端口做好端接,图10显示了平面层L2和L3上电流的方向。可以看到当电流方向是从端口2到端口1时,L2上的返回电流在到达缝隙的远端时(端口1侧)被分成左右两部分。

同时也可以看到L3上有两个反向旋转电流,基本上都集中在间隙的左右两半部分,它们是由于沿着L2上缝隙边缘的反向旋转电流将EM能量注入到平面腔中引起的。注意L2和L3上的旋转电流方向是相反的。

图10

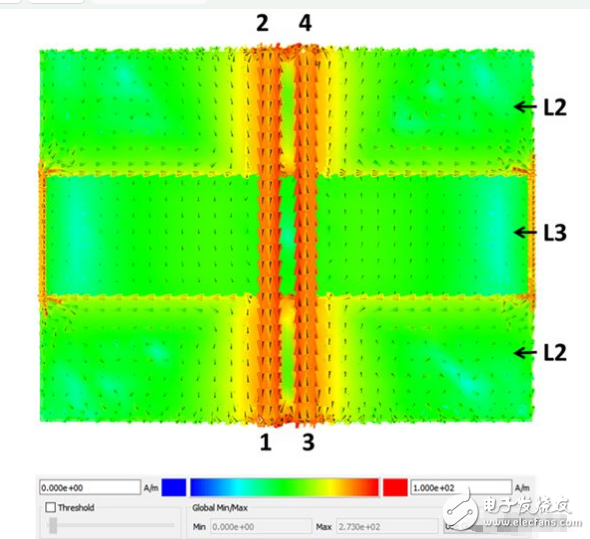

但是当在两根传输线上输入差分信号时,如图11,可以看到电流在缝隙边沿上的方向是相同的。同时也要注意旋转电流在L3上是一个方向的,集中在差分对和缝隙之间的部分。

问题是即使在两根传输线上输入差分信号,也会有电流流到间隙边缘处,从而将噪声引入平面腔,也会辐射到自由空间去,造成EMI。

图11

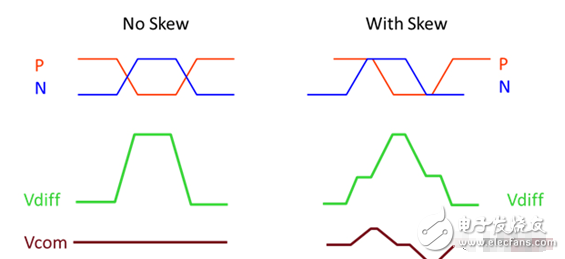

前边分析的差分对的例子采用的是对内完全匹配,但是实际中这种情况很少存在,像布线不等长、玻纤效应、连接器引脚长度不同或者是换层时差分过孔的不对称,这些问题都会引起对内延迟差。当这些情况发生时,一些差模信号会转化成为共模信号,如图12,转化程度取决于对内延迟差。在理想差分对中,Vdiff是P/N信号之前的电压差。如果它们的相位差是180度,差模电压会翻倍,并且不存在共模电压。

在有偏移(skew)的时候,差分对的相位差就不是180度了,考虑到偏移的话,差分信号会变形,并且会产生共模电压(Vcom)。共模电压的幅度和形状与相位偏移是成比例的。如果P和N的相位相同,这时没有差模电压,全部是共模电压。

共模电压也需要回流路径,如果路径被中断了,它的返回电流就会像单端返回电流一样通过分割平面。

图12

根据一些PCIe布线规范,最差的偏移是0.21UI(一个UI是一个比特位的时间)。在PCIe Gen3 8Gbps时,0.21UI的偏移是26.3ps。

将通过50mil间隙的情况等效为对内相移,并同理想情况的对比结果如图13.如所期望的一样,共模电压通过分割平面,共模返回电流跟单端线通过分割平面时(图8)的情况类似。唯一的区别是没有100%的共模电流,因此也会存在差模返回电流。

图13

最后要解决的问题是,如果在相邻的地层和分割电源层之间有一层非常薄的介质层,那么它将作为通过分割层时更好的返回路径。从逻辑上讲,这从信号完整性的角度来看是有意义的,因为传输线的阻抗随传输线和分割参考平面之间的电介质厚度增加而减小。

前边的例子我们假设的是四层板,62mil厚。这几乎决定了叠层的内层介质的厚度。为了将参考平面移至接近电源平面的缝隙,这就需要PCB层数需要增加到最少6层,以保持层叠的对称性及总厚度。

如果减小gap下边的介质厚度,重新仿真5mil gap,单端的情况,结果见图14。这层薄的介质层设为2mil,是电源平面去耦埋容芯板的常见厚度。再加上5milH1的厚度,和1.2mil厚的电源平面L2,如图1,间隙下方总的介质厚度为8.2mil。

左边的图可以看到大部分的返回电流被转移到参考平面L2缝隙的周围,右图中可以看到信号通过缝隙时,大部分返回电流流向传输线下方的参考平面L3, 但仍有一些电流会在L2的缝隙附近,因此也会辐射出去一部分噪声。

图14

从信号完整性的角度看,反射信号及近端串扰噪声基本上减少了一半,如图15,传输信号的上升时间有较少的衰减,而且远端串扰也得到了提升。

图15

再回到主题,到底哪种说法是正确的?二者都不全对,本文中讨论了微带线通过分割平面的几种情况。从信号完整性的角度看,在一定条件下,微带线通过分割平面是没问题的。例如上边的仿真,只要分割平面的间隙减小到5mil,并且在相邻平面层之间加一层薄的介质层时,串扰没有明显的增加。根据实际的噪声容限,这个可能不会有影响。

但就通过EMC来说,还是有更多的风险和疑虑。但是不会存在一部分返回电流永远不流向参考平面缝隙的边缘的情况,因此仍然存在EMI的风险。因为实际设计中有很多相关性影响最终性能,所以很难有一个通用的规则在这里适用,在其他任何情况下也适用。

一般情况下微带线应避免跨分割,当根据实际layout和板子的层叠结构不能做更详细的分析时,或许可以寻找其他可减轻噪声辐射的方法,比如增加额外的外部屏蔽。

最后本文强调的是对于现在的高速设计,我们不能仅通过信号完整性、电源完整或EMC中的一个来限制自己的思维,必须要三者同时考虑。如果仅考虑信号完整性而不考虑EMC的话,我们可能会下错误的结论,最后产品可能会因为EMC兼容测试而失败。

-

射频电路

+关注

关注

36文章

468浏览量

44941 -

高速电路

+关注

关注

8文章

170浏览量

24941

原文标题:不管是高速电路还是射频电路,当微带线跨分割时,信号将会引起什么样的问题呢?

文章出处:【微信号:SI_PI_EMC,微信公众号:信号完整性】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

这个电路有哪些核心功能呢?

【「玩转高速电路:基于ANSYS HFSS的无源仿真实例」阅读体验】+差分信号

【「玩转高速电路:基于ANSYS HFSS的无源仿真实例」阅读体验】+单端信号2

【「玩转高速电路:基于ANSYS HFSS的无源仿真实例」阅读体验】+单端信号

【「玩转高速电路:基于ANSYS HFSS的无源仿真实例」阅读体验】+本书概览,内容,特点,问题,与一些个人建议

SMA插座线束:为射频而生,与信号共行

求助射频芯片的使用,pcb绘制问题

跨阻运放:微弱电流信号的转换

凡亿Allegro Skill布线功能-检查跨分割

不管是高速电路还是射频电路,当微带线跨分割时信号将会引起什么样的问题

不管是高速电路还是射频电路,当微带线跨分割时信号将会引起什么样的问题

评论