先进封装技术(Semiconductor Advanced Packaging) - 1 混合键合技术(上)

先进封装技术(Semiconductor Advanced Packaging) - 2 混合键合技术(下)

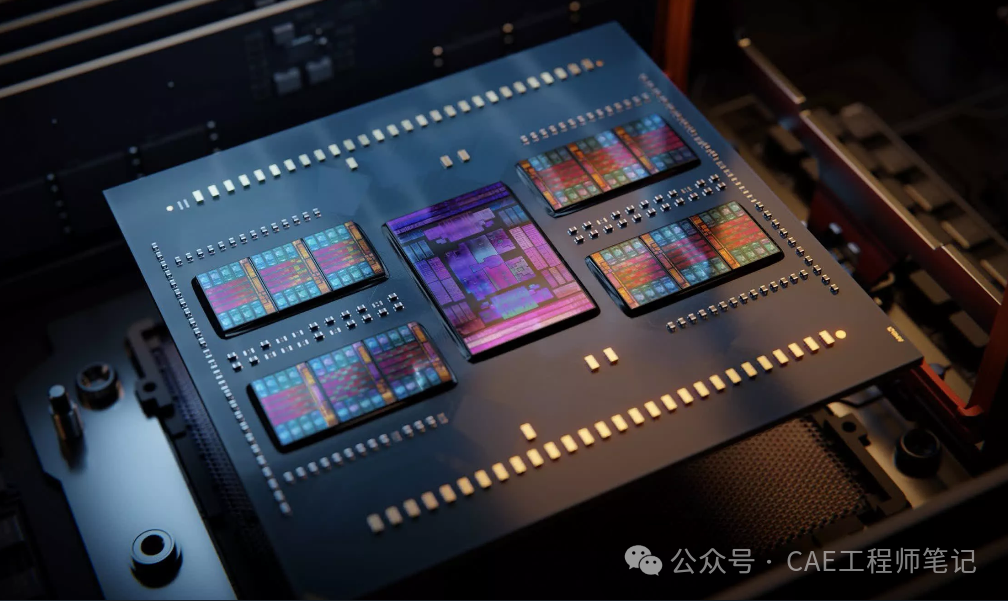

先进封装技术(Semiconductor Advanced Packaging) - 3 Chiplet 异构集成(上)

先进封装技术(Semiconductor Advanced Packaging) - 4 Chiplet 异构集成(下)

先进封装技术(Semiconductor Advanced Packaging) - 5 TSV 异构集成与等效热仿真

先进封装技术(Semiconductor Advanced Packaging) - 6 扇出型晶圆级封装(FOWLP)

先进封装技术(Semiconductor Advanced Packaging) - 7 扇出型板级封装(FOPLP)

先进封装技术(Semiconductor Advanced Packaging) - 8 3D封装与TSV技术

先进封装技术(Semiconductor Advanced Packaging) - 9 堆叠封装(PoP)技术

先进封装技术(Semiconductor Advanced Packaging) - 10 2.5D封装与异构集成技术

先进封装技术(Semiconductor Advanced Packaging) - 11 SiP 系统级封装

先进封装技术(Semiconductor Advanced Packaging) - 12 表面贴装技术 SMT

先进封装技术(Semiconductor Advanced Packaging) - 13 倒装封装 Flip Chip

先进封装技术(Semiconductor Advanced Packaging) - 14 光电共封技术(CPO) (上)

先进封装技术(Semiconductor Advanced Packaging) - 15 光电共封技术(CPO) (下)

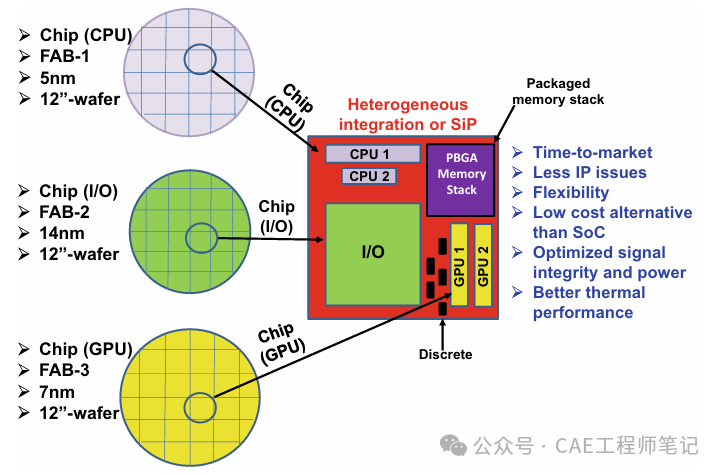

随着摩尔定律逐渐逼近物理尺寸的极限,业界不断探索着新的技术方案。前道的芯片设计和晶圆制造厂商不再单纯追求通过先进制程实现芯片内晶体管密度的增加,而是逐渐提倡从系统端出发,将复杂集成功能的芯片分解,形成某一特定功能的模块化小芯片,通过先进封装技术将这些小芯片实现高密度互连与集成,也就是chiplet技术。

Chiplet 技术设计的核心思想是先“分”后“合”,即先将单芯片中的功能块拆分出来,再通过先进封装模块将其集成为大的单芯片。

“分” 可解决怎么把大规模芯片拆分好的问题,其中架构设计是分的关键(需要考虑访问频率、缓存一致性等)。

“合” 是指将功能比较重要的部分合成在一颗芯片上,其中先进封装是合的关键(需要考虑功耗、散热、成本等)。

使用 Chiplet 技术的大芯片一定是“分”与“合”共同作用的产物。采用 Chiplet 技术通常有以下 4 个优势:

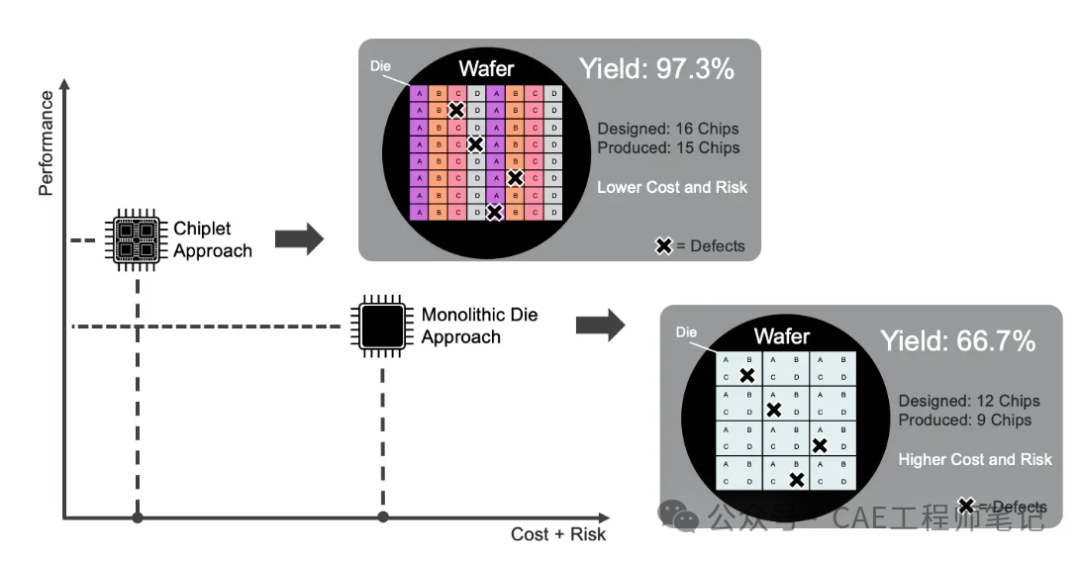

芯片可分解成特定模块。这可使单个芯片变得更小并可选择合适的工艺,以提高工艺良率,摆脱制造工艺的限制,降低成本。

Chiplet 小芯片可被视为固定模块,并可在不同产品中进行复用,具有较高的灵活性。这不仅可以加快芯片的迭代速度,还能提高芯片的可扩展性。

Chiplet可以集成多核,能够满足高效能运算处理器的需求。

相较于更先进的半导体工艺制程,Chiplet的综合成本更低,收益更高。

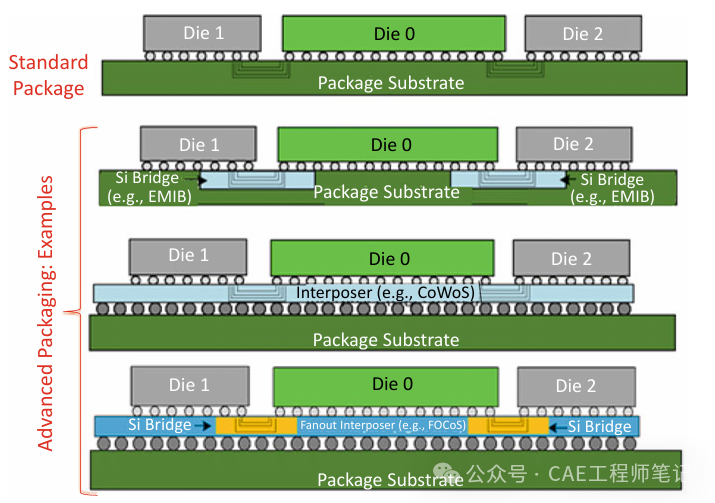

Chiplet 和集成封装之间的主要区别在于,Chiplet是一种芯片设计方法,而集成封装是一种芯片封装方法。Chiplet 集成封装技术主要有 4 种封装方式:

多芯片封装,该技术通过将芯片并排放置在有机基板上来实现芯片间的通信;

利用硅桥实现芯片互连,并将硅桥嵌入到封装基板中;

使用硅中介层连接芯片并进行重布线,再将硅中介层封装到基板上;

使用扇出型中介层进行重布线,仅在芯片连接处使用硅桥进行互连。

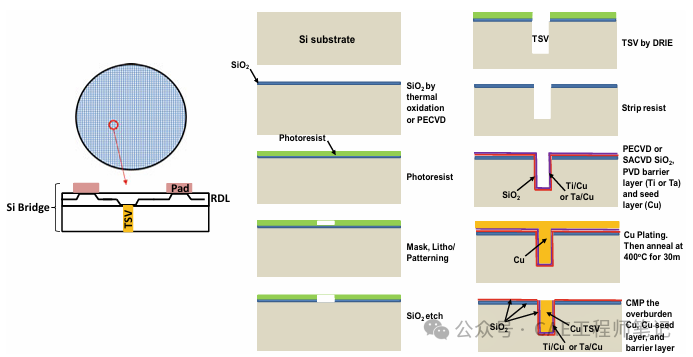

其中,硅桥技术通过在特定位置埋入带有多层 RDL 的小型桥连芯片,实现了 2 个芯片的电气连接,硅桥作为高密度互连基板制造的关键组成部分,有效降低了制造成本。

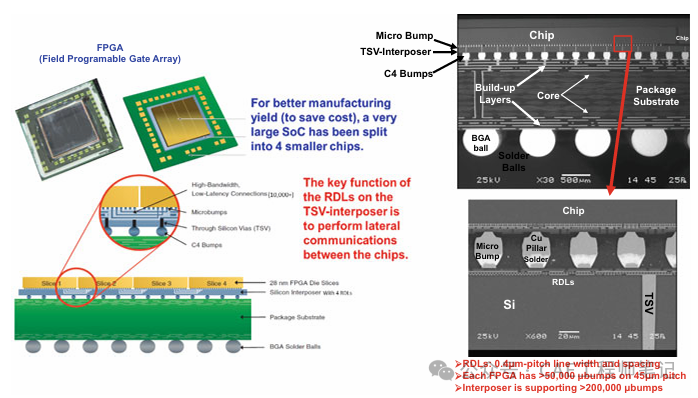

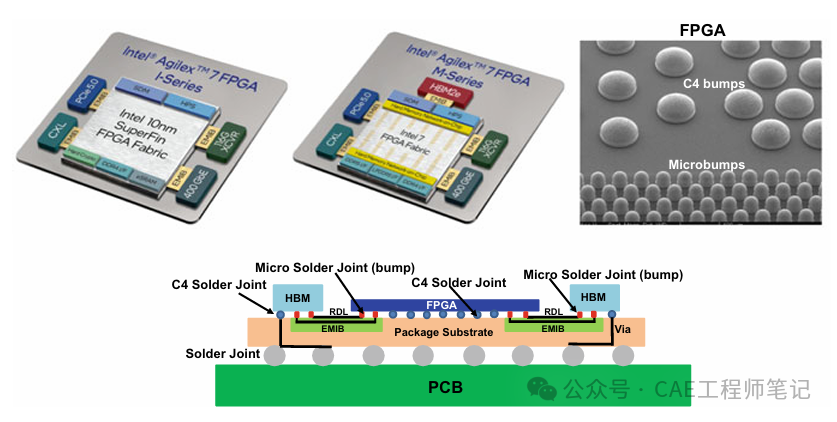

2011 年,台积电为赛灵思打造一颗 28nm工艺的 FPGA 芯片,受工艺和良率影响,台积电巧妙的将一个大尺寸 FPGA 芯片分成 4 颗较小的 FPGA 芯片,如下图所示,芯片间的互连以及芯片与基板的互连通过硅转接板完成,该技术也就是现今如火如荼的 2.5D TSV 硅中介层转接技术(CoWoS)。CoWoS 的出现有效解决了多芯片间高密度、短距离的互连问题,但也大大提高了封装集成工艺成本。为解决硅转接板带来的成本问题,桥接技术出现在了大众视野中。

首先,目前芯粒异构集成需求中,芯粒间高密度互连涉及的信号区域通常为很小的局域的范围,没有必要在整个基板或者转接板上开发精细化布线技术。其次,通过桥接互连能满足互连密度需求,且桥接载体的制造工艺相较于 TSV 转接板制造工艺较简单,成本较低,工艺更灵活。

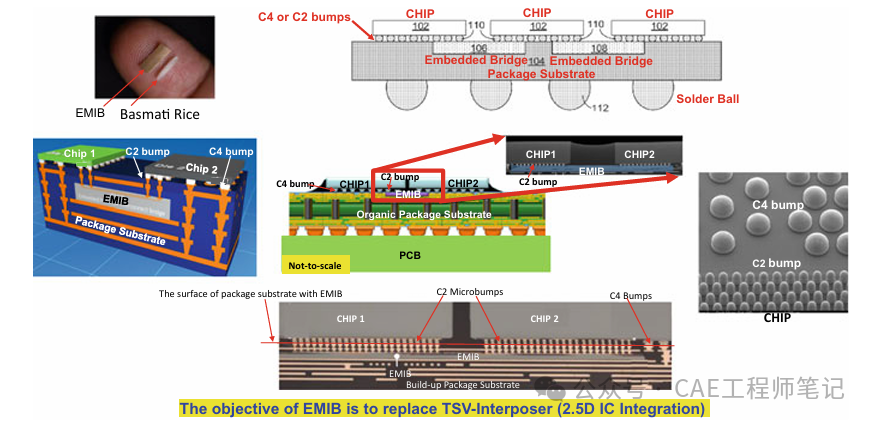

桥接的载体可以是刚性的也可以是柔性的,刚性桥接技术最为知名的也就是英特尔提出的嵌入式多芯片互连桥接技术(EMIB),高精度布线通过前道工艺在硅载体上制备,形成刚性的硅桥芯片。

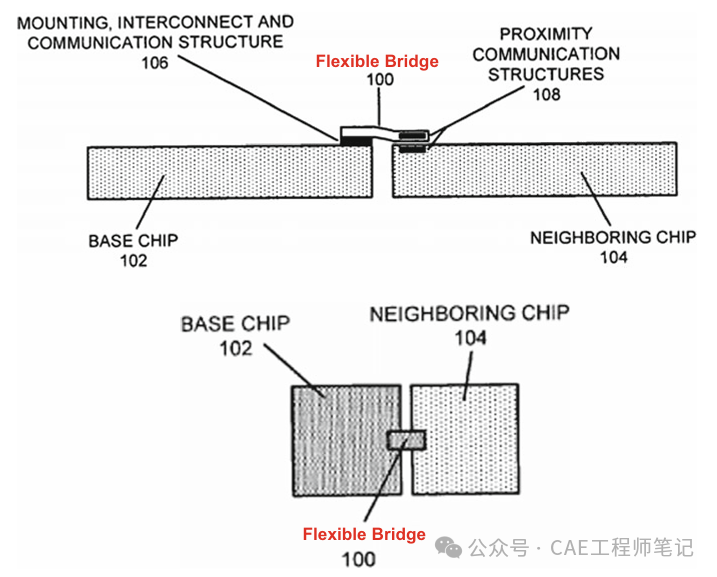

柔性桥接就是把再布线通过环氧树脂材料进行包裹,SUN Microsystems 于 2004 年提交了第一个柔性电桥专利申请 US 2006/0095639 A1,但是柔性桥接载体与芯粒的组装难度远大于刚性桥接,实用性不佳。

Intel’s Embedded Multi-die Interconnect Bridge (EMIB)

英特尔提出的 EMIB 技术核心思想就是通过硅桥芯片上局域高密度布线解决传统基板布线密度不足问题。EMIB 技术相较于台积电的CoWoS 和安靠的 SLIM 技术,其关键的优势在于没有转接板带来的制造成本、工艺制造以及尺寸限制的问题。首先硅桥作为预制件可以通过前、中道工艺制备高密度布线,相较于硅转接板需要额外配套高深宽比打孔、金属填充等工艺,其工艺成本和技术难度较低。其次硅转接板或者扇出型封装受到材料本身强度的限制,尺寸无法做大,因此限制了芯粒的尺寸以及封装后的尺寸。最后 EMIB 技术的开发基于标准有机基板工艺,没有额外引入新的技术,开发难度相对较低。

EMIB 技术方案基于标准有机基板制备工艺,但其核心挑战在于如何精确完成盲孔与硅桥芯片焊盘间的对准,其难点主要包括:硅桥贴装精度、基板与硅桥之间装片孔洞、硅桥偏移、盲孔成型等。英特尔在对准精度控制提升、芯片粘接膜(DAF)材料选择设计、硅桥翘曲控制、硅桥包封保护以及工艺整合方面都做到了精益求精,最终能够完成 EMIB 技术的完美实现。

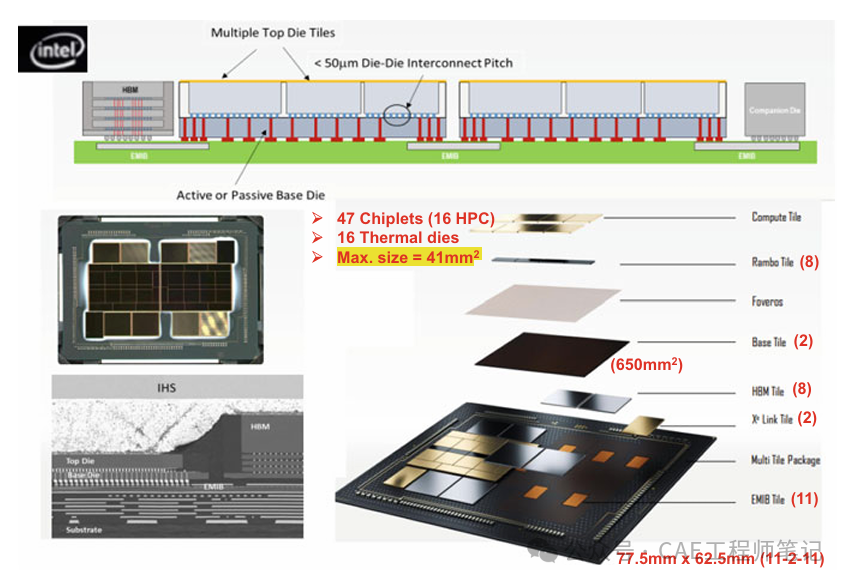

EMIB 技术方案已在 Stratix10 FPGA 系列产品上得到应用验证,满足产品对高密度、大带宽、高性能以及成本控制等一系列产品需求。EMIB 本质上属于二维集成封装技术,除了 EMIB 先进封装技术外,英特尔还推出了面向三维异构集成芯片堆叠的基于有源硅板载的 Foveros 技术,能适用于小尺寸产品或对内存带宽要求更高的产品。

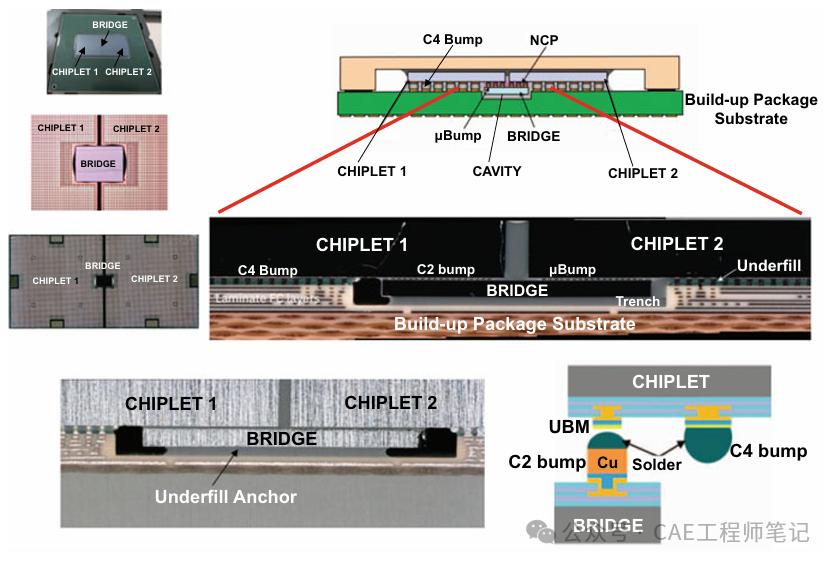

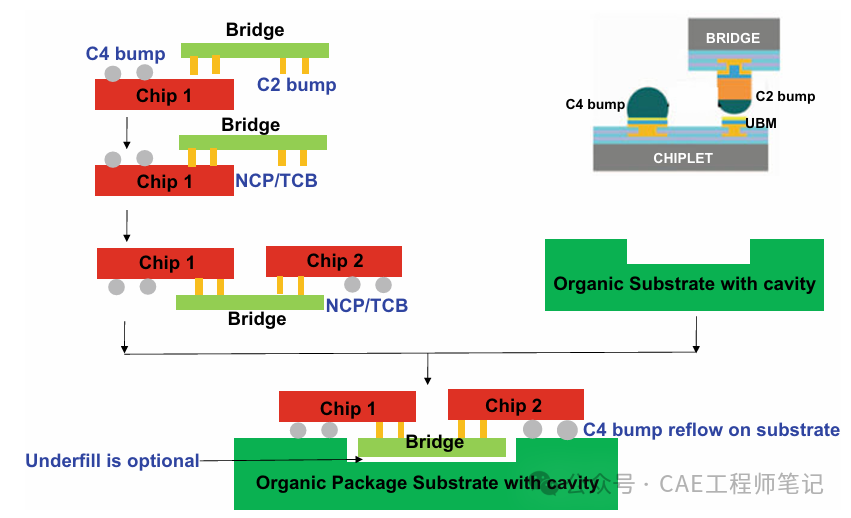

IBM’s Direct Bonded Heterogeneous Integration (DBHi)

IBM 提出的基于硅桥芯片互连的先进封装技术为基于直接键合的异构集成技术(DBHi),与英特尔 EMIB 硅桥与芯片分开组装的方案不同,IBM 的 DBHi 技术将硅桥与芯粒直接键合形成预制件,然后将组装好的芯片预制件与基板再次进行封装。

DBHi技术有以下3 个特点:

硅桥与芯片先进行组装,形成芯片-硅桥预制件,因此硅桥不会完全被包封;

硅桥和芯片上分别采用了两种结构的凸点,硅桥上生长了 C2 铜柱凸点,芯片上生长了 C2 球状凸点以及焊盘,区别于 EMIB 在单颗芯片上采用了两种凸点的方式;

基板顶层存在空腔,该空腔的空间仅用于放置硅桥芯片;

IBM 提供了一种与 EMIB 和嵌入环氧树脂材料方案不同的思路。无论是硅桥与有机基板融合的 EMIB 技术,还是硅桥与扇出型封装结合的技术,硅桥芯片都是内嵌在基板或者转接板层内,是被完全包封的状态,并且需要在硅桥上额外制作线路层完成芯片间的互连,而 DBHi 技术中硅桥直接与芯片互连,硅桥只需要通过底填的方式进行保护。

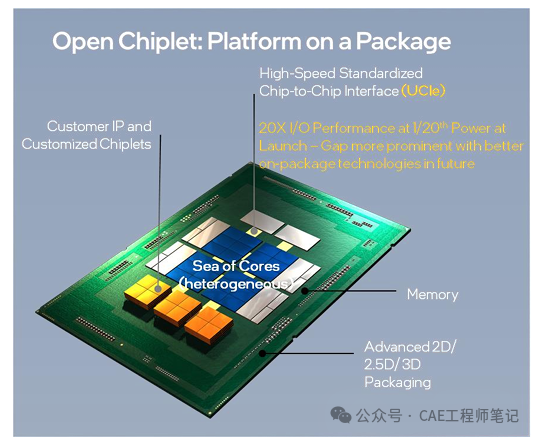

Universal Chiplet Interconnect Express (UCIe)

2022年3月2日,英特尔牵头的通用芯粒互连技术(UCIe)行业联盟宣布成立,UCIe 董事会和领导层包括创始成员 ASE、AMD、Arm、Google Cloud、Intel、Meta、Microsoft、Qualcomm、Samsung和台积电,以及新当选的成员阿里巴巴和 NVIDIA。

UCIe 推荐了标准封装和先进封装两类集成技术方案以此满足不同芯粒的集成需求,如下图所示,芯粒的标准封装通过高密度有机基板实现互连,先进封装则是通过硅基载体实现互连,其中硅基载体可以是硅转接板,对应台积电的 CoWoS 技术,也可以是硅桥芯片,对应英特尔的 EMIB 和日月光的 FoCoS-Bridge 技术。

2023年2月13日,中国科学院计算技术研究所牵头的《小芯片接口总线技术要求》正式发布,在该要求中,硅桥互连技术同样是芯粒集成的推荐方案之一,与 UCIe 略有区别的是硅桥与扇出型封装进行了结合。

-

芯片

+关注

关注

456文章

50967浏览量

424957 -

先进封装

+关注

关注

2文章

418浏览量

263

原文标题:先进封装技术(Semiconductor Advanced Packaging) - 16 硅桥技术(Si Bridge)(上)

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

硅通孔封装工艺流程与技术

多芯片整合封测技术--种用先进封装技术让系统芯片与内存达到高速传输

ASEMI可控硅模块MTC110-16为何能得到大家的青睐

详解TSV(硅通孔技术)封装技术

先进封装技术的发展与机遇

什么是先进封装?先进封装技术包括哪些技术

先进封装技术-16硅桥技术(上)

先进封装技术-16硅桥技术(上)

评论