先进封装技术(Semiconductor Advanced Packaging) - 1 混合键合技术(上)

先进封装技术(Semiconductor Advanced Packaging) - 2 混合键合技术(下)

先进封装技术(Semiconductor Advanced Packaging) - 3 Chiplet 异构集成(上)

先进封装技术(Semiconductor Advanced Packaging) - 4 Chiplet 异构集成(下)

先进封装技术(Semiconductor Advanced Packaging) - 5 TSV 异构集成与等效热仿真

先进封装技术(Semiconductor Advanced Packaging) - 6 扇出型晶圆级封装(FOWLP)

先进封装技术(Semiconductor Advanced Packaging) - 7 扇出型板级封装(FOPLP)

先进封装技术(Semiconductor Advanced Packaging) - 8 3D封装与TSV技术

先进封装技术(Semiconductor Advanced Packaging) - 9 堆叠封装(PoP)技术

先进封装技术(Semiconductor Advanced Packaging) - 10 2.5D封装与异构集成技术

先进封装技术(Semiconductor Advanced Packaging) - 11 SiP 系统级封装

先进封装技术(Semiconductor Advanced Packaging) - 12 表面贴装技术 SMT

先进封装技术(Semiconductor Advanced Packaging) - 13 倒装封装 Flip Chip

先进封装技术(Semiconductor Advanced Packaging) - 14 光电共封技术(CPO) (上)

先进封装技术(Semiconductor Advanced Packaging) - 15 光电共封技术(CPO) (下)

先进封装技术(Semiconductor Advanced Packaging) - 16 硅桥技术(Si Bridge)(上)

(继续上文~)基于扇出型封装的硅桥互连

基于扇出型封装的硅桥互连技术思路是将硅桥芯片埋置在环氧树脂料中,通过再布线完成与芯片的互连。根据硅桥芯片与再布线层制作顺序的不同可以进一步区分为硅桥芯片后置型和先置型技术。硅桥芯片后置型技术中 RDL 层可以优先制作,随后与 RDL 层完成倒装焊接。

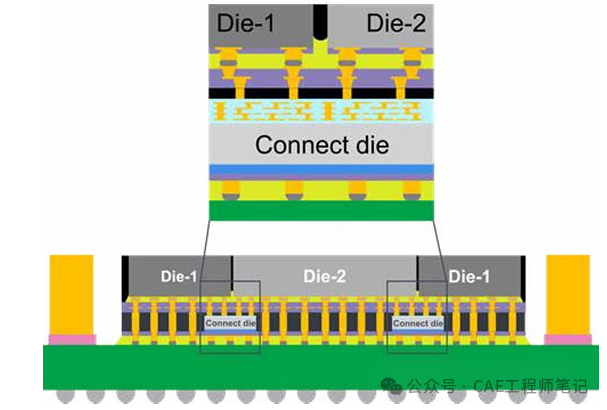

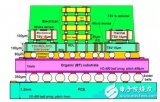

安靠提出的芯粒异构集成封装技术为埋置扇出型中介层技术 (S-Connect),该项技术中内置的桥芯片不仅可以是硅桥,也可以是树脂桥。封装测试样件结构如下图所示,包含一颗逻辑芯片和两颗存储芯片,功能芯片与内嵌桥芯片的扇出型转接板进行组装。

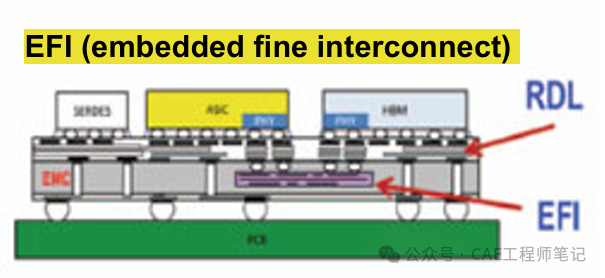

IME 研究所提出基于硅桥芯片的高密度异构集成先进封装解决方案为内嵌精细互连技术(EFI)。通过嵌入式转接板实现 ASIC 芯片和存储芯片的异构芯粒的集成。其中 EFI 芯片也就是硅桥芯片,布线层数为 2 层,布线精度为 5μm,信号通过铜柱凸点(Cu/SnAg)引出。

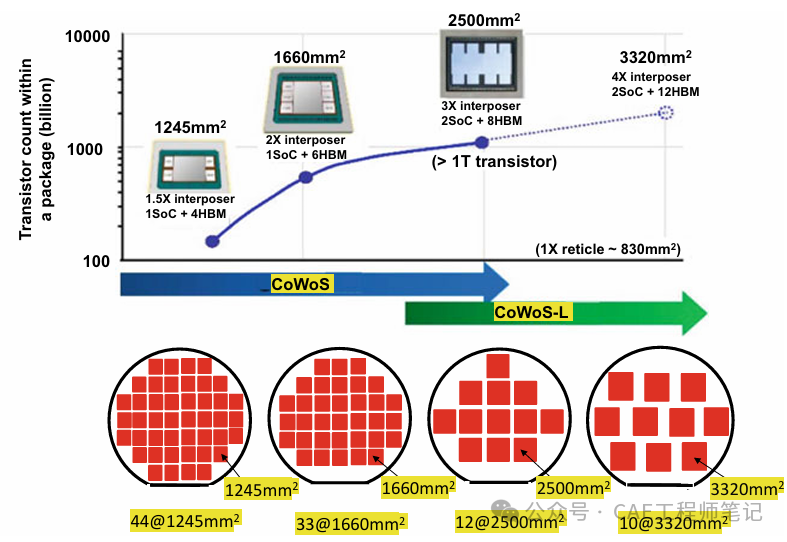

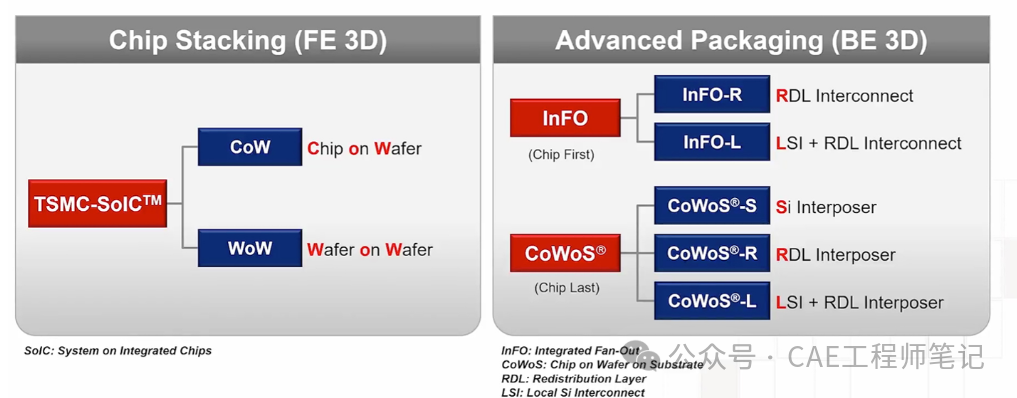

台积电为了进一步优化和发展在 2.5D 以及 3D 先进封装集成技术,满足未来芯粒和异构集成的需求,细化了 InFO 和 CoWoS 两项技术的发展方向。

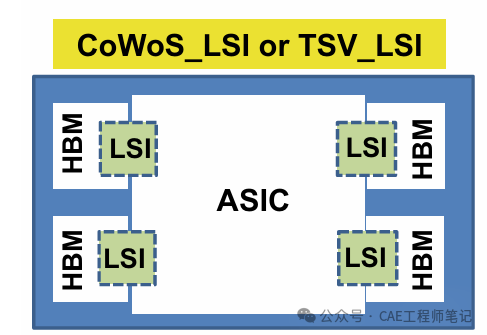

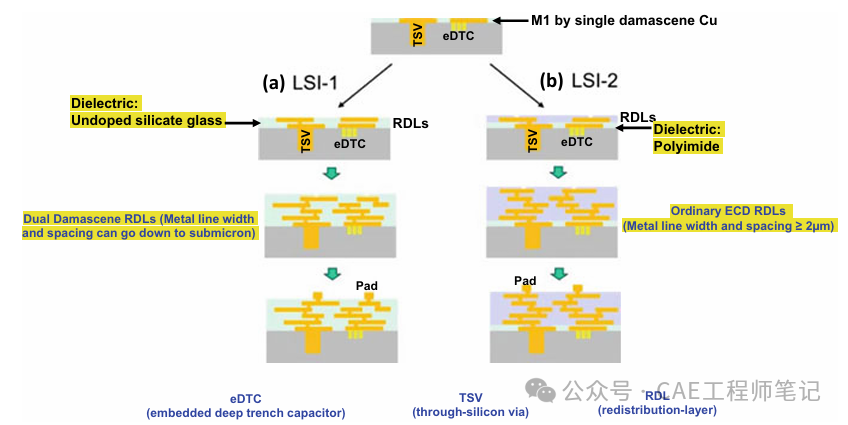

InFO 技术进一步细化为 RDL 集成扇出 (InFO-R) 和硅桥内嵌 RDL 集成扇出(InFO-L)。CoWoS 技术进一步细化为硅中介层技术(CoWoS-S)、RDL中介层技术 (CoWoS-R) 和硅桥内嵌 RDL 中介层技术(CoWoS-L)。InFO-L 和 CoWoS-L 中的 L 代表 LSI,也就是局域硅桥互连。

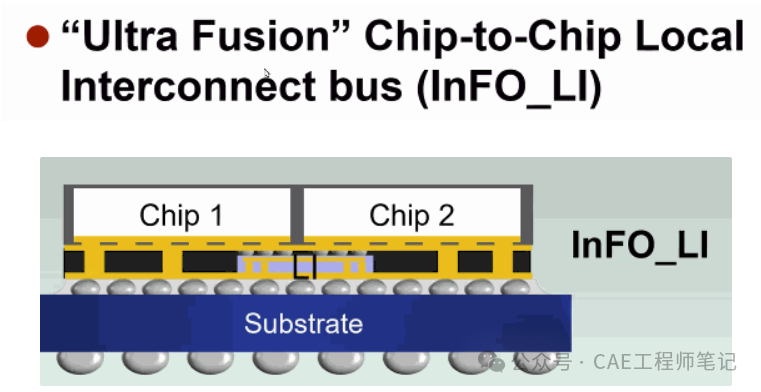

InFO-L 技术是台积电在 InFO 的基础上通过扇出实现硅桥芯片内嵌的技术,先将裸芯片通过重构扇出工艺完成再布线层,硅桥芯片内嵌在芯片的再布线层中。CoWoS-L 技术是台积电基于 CoWoS 硅基转接板的思路,通过制备有机转接板来替代硅转接,其中有机转接板通过再布线工艺实现,制备过程中内嵌了硅桥芯片。

InFO-L 技术是在芯粒的重构圆片上完成再布线层的制备,CoWoS-L 技术在临时载板上单独完成再布线层的制备,随后与硅桥芯片完成集成,因此属于硅桥芯片后置型技术。

硅桥芯片先置型技术中优先完成硅桥芯片与塑封料的结合,硅桥芯片采用正装装片(区别于后置型技术中硅桥芯片的倒装焊接),在此基础上进行再布线层制作和芯片组装。

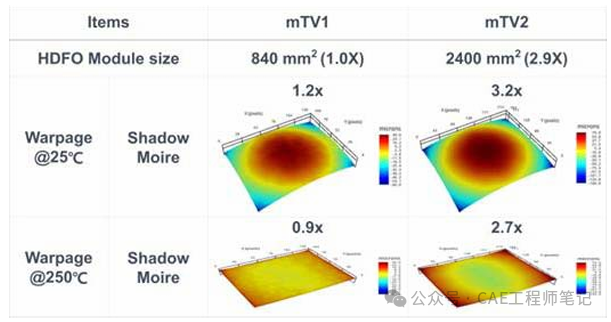

日月光在面向高性能计算的芯粒集成需求时,提出了高密度扇出型封装技术系列方案,分别命名为芯片后置型扇出 (FOCoS-CL)、芯片先置型扇出 (FOCoS-CF) 以及扇出堆叠技术 (sFOCoS)。三种技术都是基于晶圆级扇出型封装,将不同设计和工艺节点的芯粒形成单个封装体。日月光强调晶圆级翘曲控制对于整个芯粒集成至关重要,并指出塑封料和底部填充材料的选择对于改善扇出封装圆片的翘曲有巨大影响。

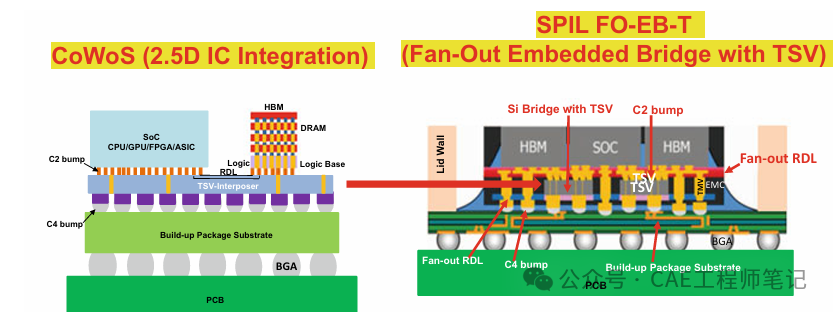

在IEEE/ECTC 2023,SPIL 提出了基于扇出型封装提出了硅桥埋置扇出技术 FOEB 和 FOEB-T 技术。FOEB 工艺流程基本和日月光的 sFOCoS 一致,FOEB-T 与 FOEB 的区别是将内嵌的硅桥芯片采用 TSV 芯片的设计,进一步减少长距离的传输损耗。

硅桥封装面临的挑战在基于硅桥技术的集成封装中,封装体各部分的材料、结构、工艺参数及流片过程的差异较大,这些差异导致微结构互连界面上的电、热、力等性能均面临较大的挑战,这对整个集成封装体的协同设计及制造能力提出了极高的要求。

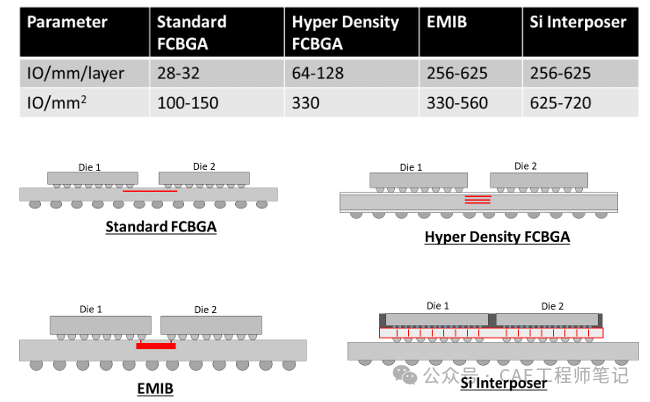

由于硅桥需要被嵌入到基板中,这会导致有机基板制备工艺复杂性提高,在精度要求上远高于现有的有机基板布线,因此需要针对该结构进行相应的材料和工艺开发。为了满足高密度布线和高频传输的要求,ABF 膜的硅粉填料占比不断提高,其 CTE 和介电损耗不断降低,同时还要确保材料对曝光光线的高敏感度。基板上的金属线路大多是通过半加成工艺制备的,该工艺对介质层与基底上金属种子层结合力的要求较高。若结合力较差,在湿制程腐蚀过程中容易出现侧刻或分层的现象,导致线路与基底分离,不利于精细线路的制备。由于对表面平整度的要求高,在层压介质层的过程中必须实现高度平坦化,以提高Chiplet 与硅桥的键合平整度。由于整个封装体工艺集成度高,从设计到加工必须实现协同性制造。

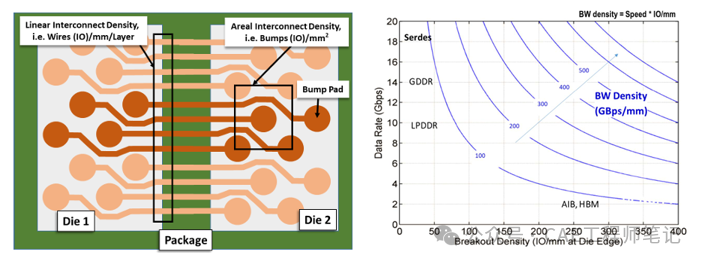

随着布线宽度的减小,线电阻会急剧增加,线间的电容也会改变,这些变化给信号的完整性增加了挑战。在进行硅桥走线设计时,不仅要考虑介质层材料的介电常数和高频损耗对整体性能的影响,还要进行非常详细的架构设计和模拟工作来保证最终的产品性能。

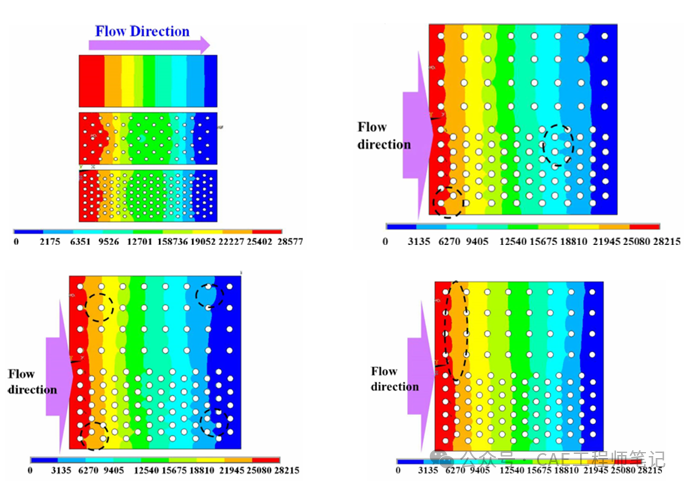

底部填充料被用于填充芯片与基板、硅桥与基板之间的空隙,以降低焊点因热应力导致的断裂失效风险。在各种底部填充材料中,环氧树脂基底部填充胶不仅应用最为广泛,也是商业化程度较高的产品。然而,随着芯片尺寸的日益增大,芯片与硅桥上的微凸点数量越来越多,填充胶的填充速度大大降低,进而延长了填充工艺的时间。同时,由于填充胶的流动性无法满足微凸点结构的特定需求,使得部分微凸点周围出现空洞。空洞的存在会严重影响倒装芯片的封装可靠性。此外,毛细管环氧基底部填充胶的导热系数较低,难以满足下一代先进封装芯片在功率密度方面日益增长的散热需求,亟待开发出低成本、高可靠的底部填充材料。

-

芯片

+关注

关注

456文章

50967浏览量

424957 -

先进封装

+关注

关注

2文章

418浏览量

263

原文标题:先进封装技术(Semiconductor Advanced Packaging) - 17 硅桥技术(Si Bridge)(下)

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

硅通孔封装工艺流程与技术

多芯片整合封测技术--种用先进封装技术让系统芯片与内存达到高速传输

先进封装技术的发展趋势

详解TSV(硅通孔技术)封装技术

先进封装技术的发展与机遇

什么是先进封装?先进封装技术包括哪些技术

先进封装技术-17硅桥技术(下)

先进封装技术-17硅桥技术(下)

评论