在上期的芝识课堂中,我们介绍了一部分CMOS逻辑IC设计的常见问题以及处理办法。本期课堂将继续探讨如何优化CMOS逻辑IC的性能,特别是负载电容连接技巧和功耗计算,这些因素对于电路的设计极其重要。

负载电容和CMOS输出引脚的连接问题

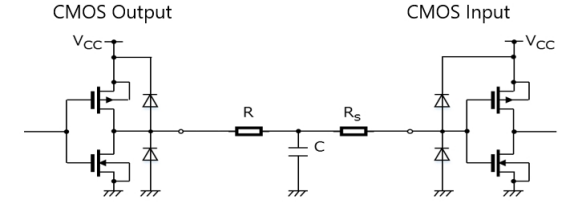

在将负载电容连接到CMOS集成电路(IC)的输出引脚时,须谨慎选择电容的大小。具体来说,大电容会增加CMOS输出的传输延迟,并且电容的充/放电过程会增加进出的电流,这可能导致电路中的噪声问题,甚至可能因电流过大而损坏连接引线。此外,由于电流在掉电时会流向输出寄生二极管,因此大负载电容不可直接连接到CMOS IC上。

若需将电容器直接连接到CMOS IC的输出端以增加其延迟时间或过滤噪声,则应选择500pF或更小的电容。当需要较大的电容时,应在IC输出端和电容器之间连接限流电阻(R)。具有输出容限功能的CMOS IC不需要限流电阻(R)来断电。但可能需要一个限流电阻(R)来限制进入电容的充电电流。

不仅如此,大负载电容也不应直接连接到CMOS IC的输入引脚。

当电容由于掉电而放电时,电流流向内部保护二极管,并通过输入引脚返回到VCC。因此,大负载电容不能直接连接到输入引脚。如果需要直接连接电容,推荐最高选择500 pF的器件。如果需要更大的电容器,则应在IC输入端和电容器之间连接限流电阻(Rs)。

连接大负载电容

计算工作电流和功耗

如何计算通用逻辑IC的功耗?可通过获取静态电流和动态电流,然后将该电流乘以施加到IC的电压来计算通用逻辑IC的功耗。

静态功耗:PS

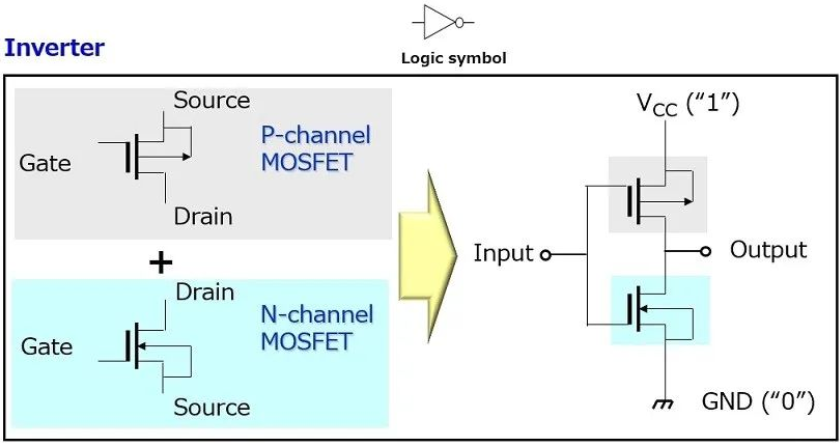

当CMOS逻辑处于静态(即当其输入电压几乎保持不变)时,除了流过内部反向偏置pn结的微小漏电流(即静态供电电流,ICC)以外,几乎没有电流流动。

静态功耗是将ICC乘以供电电压:PS=VCC×ICC

VCC:施加在逻辑IC上的电压。

ICC:如数据表所示的静态供电电流。

静态功耗:PL+PPD

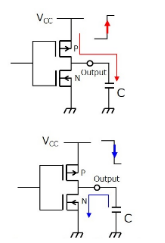

动态供电电流是指当输入在高电平和低电平之间转换时流过CMOS逻辑IC的电流。该电流在电容充放电过程中流动。必须同时考虑寄生电容(内部等效电容)和负载电容。

动态功耗是将动态供电电流乘以施加在p沟道或n沟道MOSFET上的电压。为方便起见,以下计算将假定此电压等于VCC,此时动态供电电流最大。

负载电容(CL)引起的动态功耗:PL

PL指外部负载充电和放电时的功耗,如右图所示。

CL引起的动态功耗

存储在负载电容上的电荷量(QL)计算为QL=CL×VCC,CL为负载电容。

设输出信号频率为fOUT(=1/TOUT),则平均电流(IL)表示为:IL=QL/T=CL×VCC×fOUT;因此,动态功耗(PL)为:PL=VCC×IL=CL×VCC²×fOUT;

如果一个IC有多个输出,其动态功耗可计算如下:PL=VCC2×Σ(CLn×fOUTn)

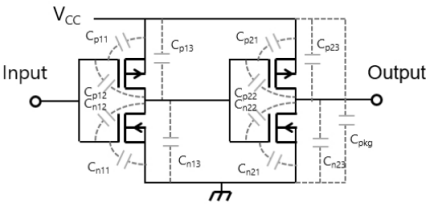

内部等效电容(CPD)引起的动态功耗:PPD

CMOS逻辑IC具有各种寄生电容,如右图所示。这些电容可等效地表示为CPD(实际上,CPD的基于零负载条件下相对较高频率(1 MHz)时的功耗计算得出的)。

PPD是IC的等效电容消耗的功率,可按与PL相同的方式考虑。但请注意,PPD的计算是基于输入频率(fIN):PPD=VCC×IL=CPD×VCC²×fIN。

CPD引起的动态功耗

总功耗(PTTL)可以表示为静态功耗(PS)和动态功耗(PL+PPD)之和:PTTL=PS+PL+PPD。

输入容限功能可用于电平转换

输入容限功能允许在电源激活时或电压为0 V时,向输入端施加高达最大工作电压的电压,允许电平从较高电压转换为较低电压。例如,东芝的74VHC和74LCX系列可用于将5 V转换至3 V,74VCX系列可用于将3V转换至1.2 V。

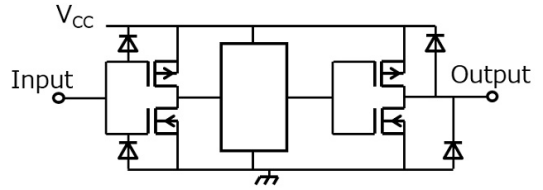

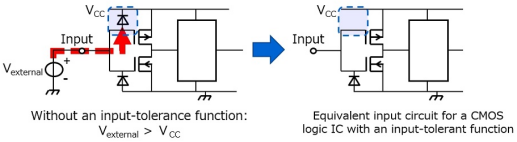

无输入容限和掉电保护功能的CMOS逻辑IC的等效输入/输出电路

在输入侧插入二极管以进行ESD防护。如果施加的电压高于VCC或在IC关断时施加电压,则输入端和电源之间的二极管可能会导通。在本例中,IC可能会被产生的大电流破坏。因此,通过使用具有输入容限功能的IC,即输入端和电源之间无二极管的IC,可以防止器件损坏。

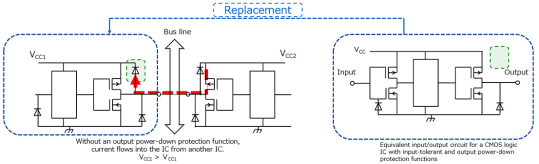

掉电保护功能应用示例(局部掉电)

如果使用具有掉电保护功能的IC,则可以实现局部掉电。为降低功耗,具有两个电压范围(VCC1和VCC2)的系统可以提供局部掉电模式。在该模式下,其中由VCC1运行的子系统将被关闭。例如,假设在电压范围VCC1使用74VHC系列。74VHC系列在输出端和电源之间有一个非预期的寄生二极管。因此,当VCC2>VCC1时,该寄生二极管导通。在这种情况下,IC可能会被产生的大电流破坏。使用既没有输入也没有输出寄生二极管的IC(如74VHCT、74LCX和74VCX系列)可以防止器件损坏。这些系列提供掉电保护。

东芝每个系列都具有输入容限和输出掉电保护功能:

其中,TC4049BF/BP,TC4050BF/BP,TC74HC4049BP/BF/BFT,74HC4049D,TTC74HC4050BP/BF/BFT和74HC4050D具有允许从较高电压到较低电压电平转换的输入容限功能。

除这些使用事项和功能外,在使用CMOS逻辑IC时也应注意噪声的危害。下期内容我们将进入实际的应用案例,学习电路设计中的噪声以及应对策略,欢迎关注!

关于东芝电子元件及存储装置株式会社

东芝电子元件及存储装置株式会社是先进的半导体和存储解决方案的领先供应商,公司累积了半个多世纪的经验和创新,为客户和合作伙伴提供分立半导体、系统LSI和HDD领域的杰出解决方案。

东芝电子元件及存储装置株式会社十分注重与客户的密切协作,旨在促进价值共创,共同开拓新市场,期待为世界各地的人们建设更美好的未来并做出贡献。

-

集成电路

+关注

关注

5387文章

11540浏览量

361709 -

CMOS

+关注

关注

58文章

5711浏览量

235451 -

二极管

+关注

关注

147文章

9634浏览量

166378 -

负载电容

+关注

关注

0文章

139浏览量

10439 -

逻辑IC

+关注

关注

0文章

24浏览量

6427

原文标题:芝识课堂【CMOS逻辑IC的使用注意事项】—深入电子设计,需要这份指南(二)

文章出处:【微信号:toshiba_semicon,微信公众号:东芝半导体】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

TTL和CMOS逻辑门电路的几点认识

CMOS逻辑门电路

CMOS逻辑电路,CMOS逻辑电路是什么意思

CMOS逻辑门电路介绍

CMOS逻辑IC基础知识:系统认识CMOS逻辑IC

一起了解CMOS逻辑IC的基本操作

CMOS逻辑IC的基本操作流程

CMOS逻辑IC基础知识:解密组合逻辑背后的强大用途(上)

【CMOS逻辑IC基础知识】—解密组合逻辑背后的强大用途!(上)

如何优化CMOS逻辑IC的性能

如何优化CMOS逻辑IC的性能

评论