随着电动汽车动力总成和能源基础设施对碳化硅(SiC)功率器件需求的增加,加速了市场的增长。在这一过程中,终端用户需求不断提高以及日益增大的盈利压力促使各企业在其电力电子应用中考虑采用SiC沟槽技术(Trench)MOSFET,部分原因是基于传统硅功率器件的经验,认为沟槽技术是实现最优功率密度的唯一途径。然而,在决定沟槽技术是否为当前合适选择之前,至关重要的是要考虑下一代SiCMOSFET技术的进步,这些技术很可能会带来好处,同时避免其固有风险。

在电力电子应用中,平面技术(Planar)和沟槽技术(Trench)的关键差异

在电力电子应用中,功率密度固然重要,但可靠性也同样至关重要,甚至在某些应用中可能更为关键。尽管工程师通常专注于性能局限性问题,但可能导致计划外停机或维修的实际故障则较难接受,因为它们可能会对业务产生不可预见的重大影响。因此,沟槽技术的潜力需要进行更全面的评估。虽然沟槽技术有望成为电力电子工程工具箱的标准配置,事实上也已经被采纳使用,但采用这种技术的人对其提供可靠性能的能力还抱有相当多的"大胆一试"的想法。

在半导体生产的典型研发过程中,实现工艺的全面优化需要相当长的时间。故障可能来自意想不到的原因,而且可能要等到大量器件在现场部署数月乃至数年后才会显现出来。沟槽技术正在开辟新的道路,而基于相对有限的现场经验,供应商对可靠性的预测往往无法得到充分的验证。

相比之下,众多供应商在平面技术方面积累了数十年的行业经验,为其性能和耐用性提供了有据可查的广泛依据。换句话说,在当前发展阶段,沟槽技术相较于其他方案仍然具有更大的风险。

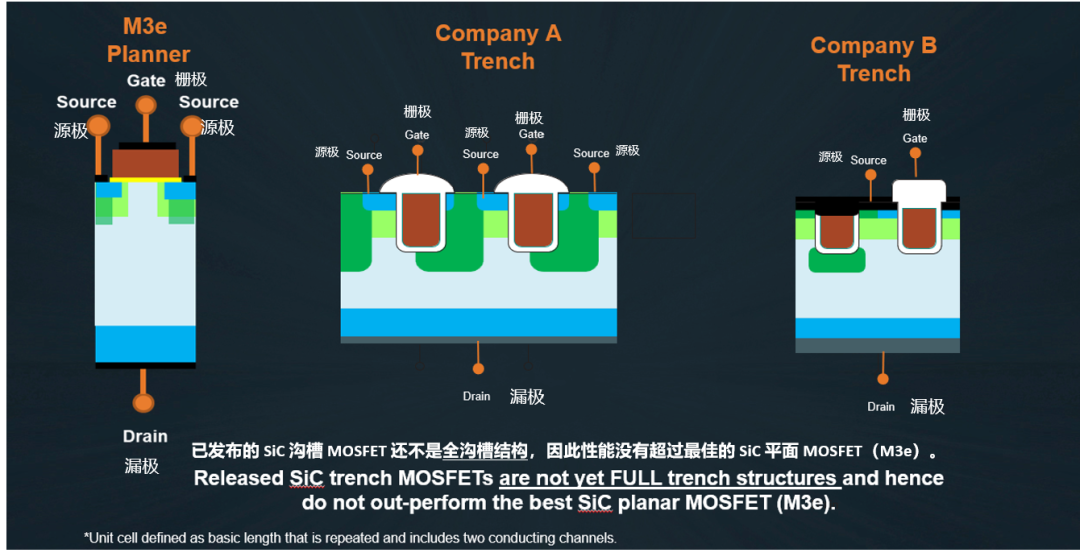

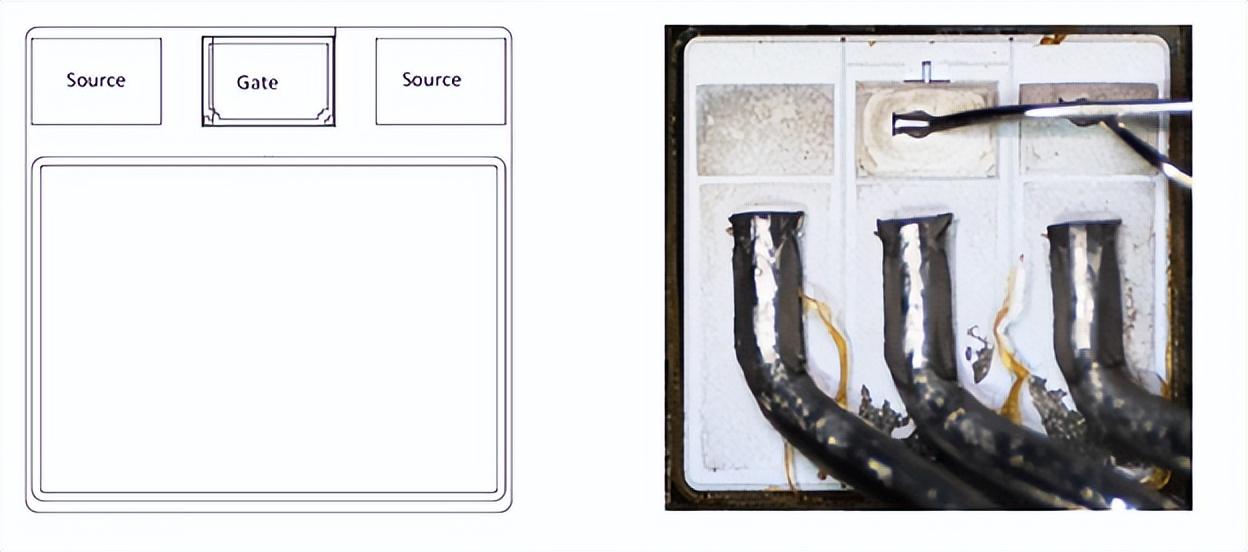

图1.M3e性能延长了碳化硅平面MOSFET的寿命

沟槽技术供应商正在努力寻找既能提高管芯(unitcell)密度,又能保持高可靠性的设计。

沟槽技术的基本问题之一(如上图左侧所示)是沟槽底部的强氧化物电场。当MOSFET阻断高压时,该电场会从相邻的强电场SiC放大。此外,沟槽底部拐角处的氧化物变薄和场拥挤效应也加剧了这一现象。这不是一个孤立的问题,而是业界一直面临的挑战。

一个解决方案的例子如中间图片所示,该图例展示了A公司的第三代沟槽技术。A公司通过在栅极沟槽两侧增加源极沟槽,并将保护性的p层下沉至SiCn-drift层内,从而解决了氧化物的难题。这些额外的源极沟槽使得管芯间距增大,实质上牺牲了沟槽的优势,因此在给定面积下,其原始性能相较于最佳的平面MOSFET而言略逊一筹。沟槽电流利用率是评估SiC沟槽MOSFET性能的重要因素。

B公司的M1产品和A公司的第四代技术将沟槽利用率提高到50%,这代表了商业应用的SiC沟槽技术的最新水平,并逐渐接近最好的平面SiCMOSFET的性能。为了使SiC沟槽MOSFET性能超越平面结构,沟槽电流利用率必须达到100%。

当前平面技术(Planar)的优势

安森美(onsemi)如何打破维度势垒,将成熟的平面技术提升到一个新的水平?

安森美在将沟槽技术作为自己 "路线图"上的一条重要技术路线的同时,还采取了两条并行的策略来实现这一目标。一方面,安森美致力于攻克沟槽技术面临的各项技术难题;另一方面,通过在非常成熟的平面技术基础上进行深化研发,不断提升性能,以实现与沟槽技术相当的性能。

平面器件建立在安森美公司和整个行业数十年的全球制造经验基础之上。这意味着平面器件比其他替代方案具有更高的性能、稳定性和可靠性。整个平面供应链经过不断优化,以实现最佳效果。沟槽技术很可能最终达到这一水平,但目前相对较新,在实际应用中的长期部署案例还很有限。

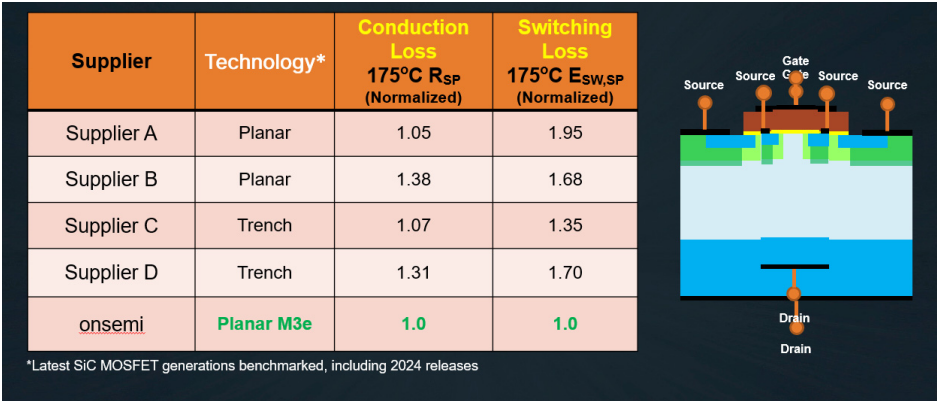

图2.1200 V EliteSiC M3e用于主驱逆变器中实现行业领先的低损耗

另一个需要考虑的因素是从硅衬底到SiC的过渡。大多数客户都是第一次使用SiC,可能没有意识到这种材料的可靠性风险更大。在硅衬底平面MOSFET中,氧化物与硅结合在一起,这种界面已经过广泛的研究和设计。在平面SiC中,顶部硅层发生氧化的情况与硅衬底有一定程度的相似性。而对于沟槽SiC,碳在氧化过程中起着不可忽视的作用--这是一种不同的、更具挑战性的情况,可能会导致界面形成物理上的锯齿状区域,从而可能导致电气问题。对于许多供应商来说,这仍然是一个有待时间、丰富的现场经验和工程验证才能明确解决的问题。

正在采用平面技术制造,计划向沟槽技术过渡

除了对沟槽技术可靠性的关注之外,对于安森美来说,无论是从系统级的每安培成本还是每千瓦成本的角度来看,平面器件都具有成本优势。

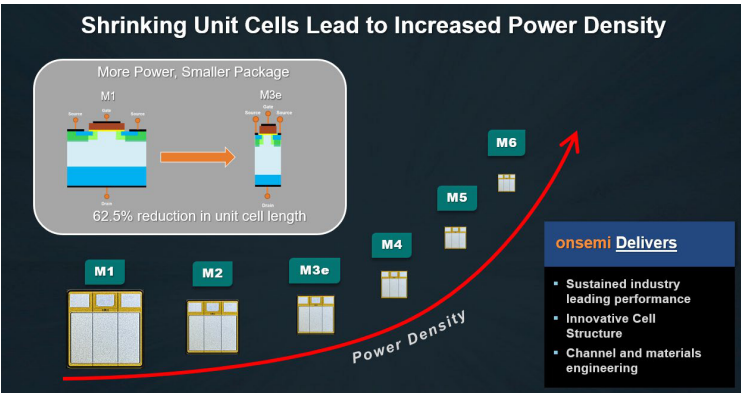

安森美EliteSiCMOSFET 在沟槽技术上的路线图始于M1/M2平面技术、方形/六边形管芯器件。随后推出的M3T和M3S平面技术、条纹管芯、薄晶圆技术显著降低了管芯尺寸。不久前,安森美推出了1200V M3e,采用了业界领先的薄晶圆平面技术,进一步适度减小了管芯体积。

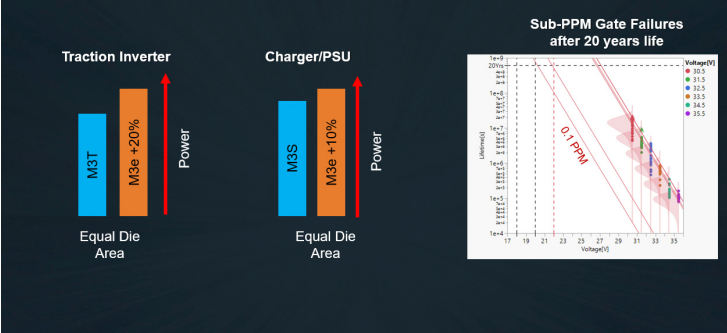

图3:安森美1200V M3e MOSFET

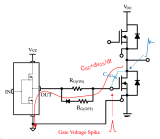

第三代M3e标志着平面技术的终极发展,其管芯间距与M1相比减少了超过60%。它建立在平面结构基础上,这种结构经过几十年的发展,已具有高度的可制造性和更长的使用寿命。SiC平面MOSFET在现场已累计使用数万亿小时,具有极低的故障率。针对SiC材料的弱点,通过100%缺陷筛选和加速电气测试进行了有效应对。特别是在栅极氧化层方面给予了特别关注,因为它们在导通状态和关断状态下都会承受高电场应力。

图4.M3e提供更高功率及经过验证的高品质

除了初始性能外,安森美M3e还通过足够高的阈值电压和极低的临界导通电阻(CRSS)实现了栅极电路的简化设计,可避免在VGS,OFF=0V时的直通现象。这一特性使得M3e对寄生导通具有更强的抗干扰能力。用户因此能够受益于在栅极驱动电路中使用单电压轨(singlevoltage rail)这一可行方案。

安森美下一代M4S和M4T产品将采用先进的沟槽设计、薄晶圆技术,并进一步将管芯体积减小25%,从而提供业界领先的沟槽技术。最重要的是,第四代MOSFET将采用100%沟槽利用率设计,以提供真正有别于传统平面器件的性能。

结论

现实情况表明,电力电子应用领域仍在充分利用现有的最佳技术方案:平面技术。在沟槽技术不断进步并趋于成熟的同时,安森美正在对平面技术进行完善,并为沟槽技术规划了发展蓝图,旨在引导其在未来实现成功部署与应用(图5)。

图5.安森美SiC路线图

-

MOSFET

+关注

关注

147文章

7208浏览量

213730 -

安森美

+关注

关注

32文章

1692浏览量

92091 -

碳化硅

+关注

关注

25文章

2784浏览量

49135

原文标题:平面技术PK沟槽技术:探索碳化硅MOSFET的持续演进

文章出处:【微信号:onsemi-china,微信公众号:安森美】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

揭秘碳化硅芯片的设计和制造

安森美1200V碳化硅MOSFET M3S系列设计注意事项和使用技巧

什么是MOSFET栅极氧化层?如何测试SiC碳化硅MOSFET的栅氧可靠性?

碳化硅深层的特性

碳化硅MOSFET的SCT怎么样?

浅谈硅IGBT与碳化硅MOSFET驱动的区别

安森美半导体发布一系列新碳化硅产品,适用于高要求应用设计

碳化硅MOSFET什么意思

安森美中国区碳化硅首席专家谈碳化硅产业链迭代趋势与背后的意义、合作与机会

安森美碳化硅MOSFET的持续演进

安森美碳化硅MOSFET的持续演进

评论