High-k栅极堆叠技术,作为半导体领域内一项广泛采纳的前沿科技,对于现代集成电路制造业具有举足轻重的地位。

在过去,半导体晶体管普遍采用二氧化硅(SiO₂)作为其栅极绝缘层。但随着半导体元件的尺寸持续缩减,二氧化硅层的厚度也相应变薄,这引发了严重的漏电问题,进而影响了元件的性能表现和功耗效率。High-k栅极堆叠技术则通过引入具备高介电常数的材料,对传统二氧化硅栅极绝缘层进行了革新性替代。

高介电常数材料能够在保持电容值不变的前提下,实现绝缘层物理厚度的增加,从而显著降低漏电电流。同时,它们与传统的栅极材料相结合,形成栅极堆叠结构,能够更精准地调控晶体管的开启与关闭状态,进而提升元件的性能和可靠性。

在众多高介电常数材料中,氧化铪(HfO₂)、氧化锆(ZrO₂)、氧化铝(Al₂O₃)等备受瞩目。这些材料不仅介电常数高,能够在较厚的绝缘层下维持与传统二氧化硅相当的电容值,而且热稳定性和化学稳定性出色,能够承受半导体制造过程中严苛的高温环境和化学腐蚀。

技术优势方面:

01

漏电电流得到有效控制

High-k栅极堆叠技术能够大幅降低晶体管的漏电电流,从而提升元件的性能表现和功耗效率。这对于现代高性能集成电路而言至关重要,特别是在移动设备和低功耗应用场景中。

地域、干湿环境的不同,会产生炎热干燥或者湿热多雨的不同气候。

02

元件性能显著提升

通过更精确地控制晶体管的开启与关闭状态,High-k栅极堆叠技术能够增强元件的开关速度和电流驱动能力,进而提升整个集成电路的性能水平。

03

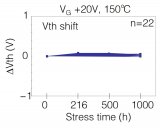

可靠性显著增强

绝缘层厚度的增加提升了晶体管的耐压能力,减少了因漏电和击穿等问题引发的元件失效,从而增强了集成电路的可靠性。

04

适应元件尺寸缩减的需求

随着半导体元件尺寸的不断缩减,传统的二氧化硅栅极绝缘层面临严峻挑战。而High-k栅极堆叠技术则为继续缩小元件尺寸提供了有力支持,满足了集成电路技术持续发展的需求。

-

晶体管

+关注

关注

77文章

9811浏览量

139154 -

栅极

+关注

关注

1文章

175浏览量

21074 -

绝缘层

+关注

关注

0文章

43浏览量

5252

原文标题:High-k栅极堆叠技术的定义与概述

文章出处:【微信号:闪德半导体,微信公众号:闪德半导体】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

集成电路新突破:HKMG工艺引领性能革命

FinFet Process Flow—哑栅极的形成

High-k栅极堆叠技术的介绍

High-k栅极堆叠技术的介绍

评论