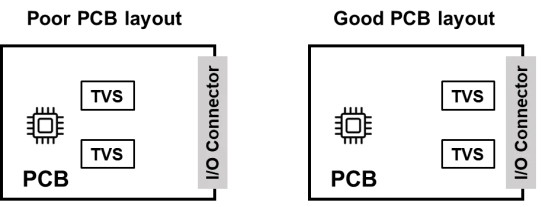

1TVS器件要尽可能布局在紧邻干扰源的输入端(端口靠近面板处)。

2连接TVS器件的导线要尽可能短且粗,以减小导线的寄生电感和低阻抗回路。并且保证TVS器件走线要比被保护对象的走线短,确保外界脉冲干扰通过TVS器件释放。

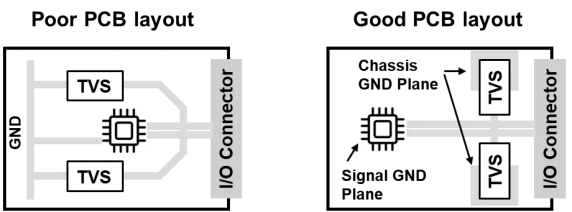

3TVS器件保护电路应该将能量直接泄放到保护地,不建议将其直接与工作信号地相连,以避免引起工作地平面信号反弹。

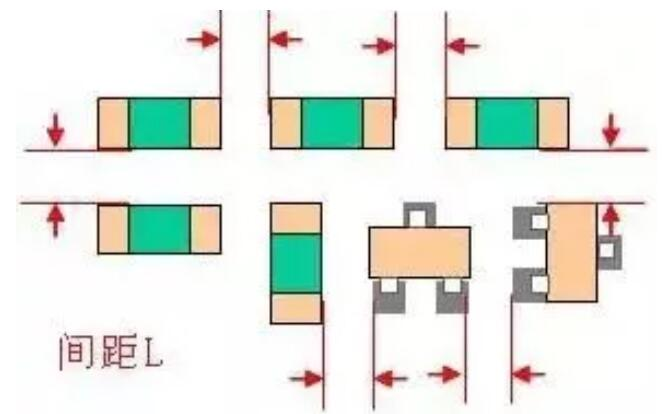

4绘制差分线的长度差应尽量小(控制在5mil以内),与其它信号网络以及地的距离尽量在20mil以上,且两侧的测试点、串联的电阻电容、上下拉电阻的摆放尽量避免直角。

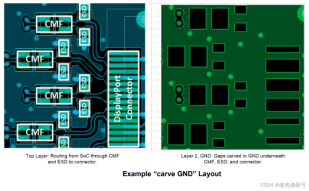

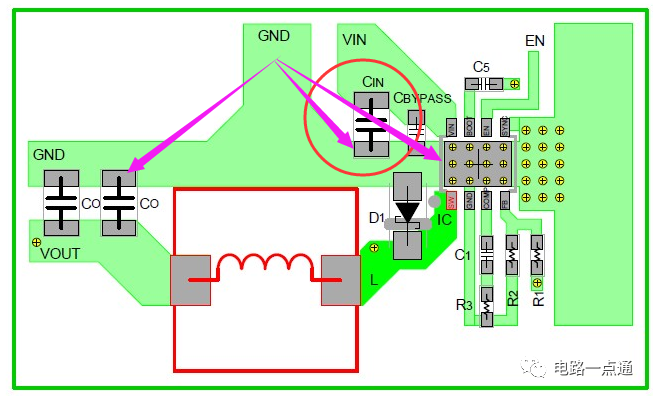

5建议在信号线换层孔附近添加回流孔,尽量减少换层孔;信号走线优先参考GND层,并保证参考平面完整。如果设计中无法避免跨平面参考,建议再跨平面分割处用旁路电容将回流信号连接起来;差分耦合电容、共模电感和ESD等器件尽量靠近DP座并对称放置;DP座上机壳地与数字地完全分开单点连接;

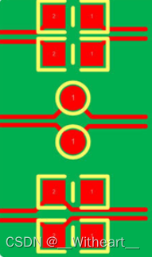

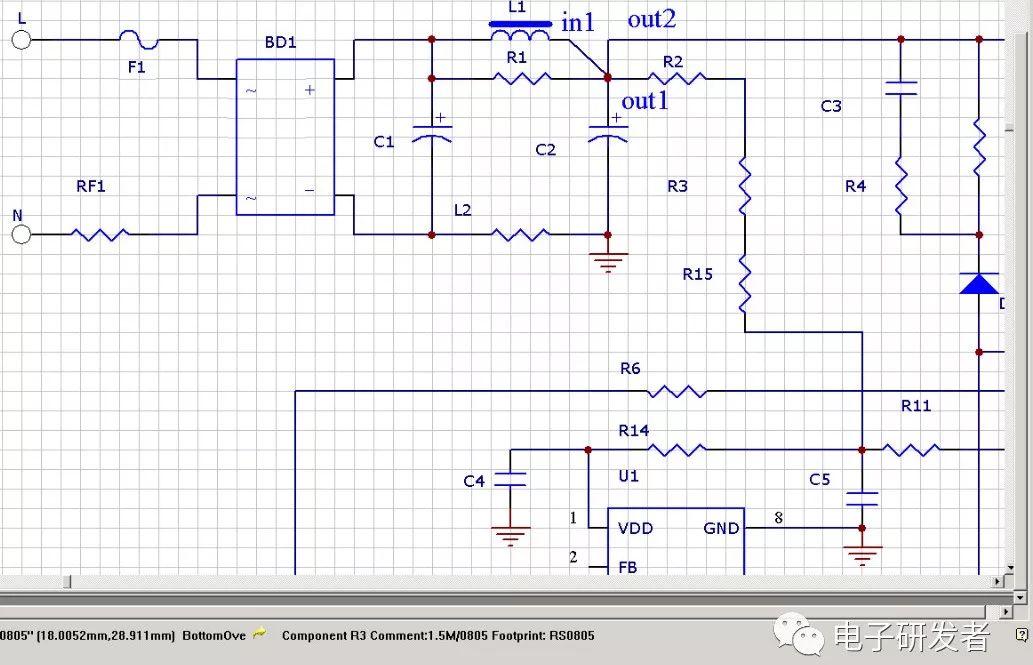

由于元器件的PAD width会导致阻抗不连续,因此建议在元器件pad下方的参考层挖空以减小阻抗的不连续性。下图为Layout的一个例子。

晶扬电子 | 电路与系统保护专家

深圳市晶扬电子有限公司成立于2006年,是国家高新技术企业、国家专精特新“小巨人”科技企业,是多年专业从事IC设计、生产、销售及系统集成的IC DESIGN HOUSE,拥有百余项有效专利等知识产权。建成国内唯一的广东省ESD保护芯片工程技术研究中心,是业内著名的“电路与系统保护专家”。

-

元器件

+关注

关注

113文章

4760浏览量

93203 -

Layout

+关注

关注

14文章

408浏览量

62178 -

寄生电感

+关注

关注

1文章

157浏览量

14668 -

TVS器件

+关注

关注

0文章

20浏览量

6985

原文标题:晶扬小课堂|Layout设计注意事项

文章出处:【微信号:晶扬电子,微信公众号:晶扬电子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

蓝牙2.4G倒F天线的layout注意事项

emi emc pcb layout注意事项

WiFi模块应用选型参考及布局走线Layout注意事项

WiFi模块应用选型参考及布局走线Layout注意事项

RF设计天线 PI型匹配layout注意事项

PCB电源板layout的设计注意事项说明

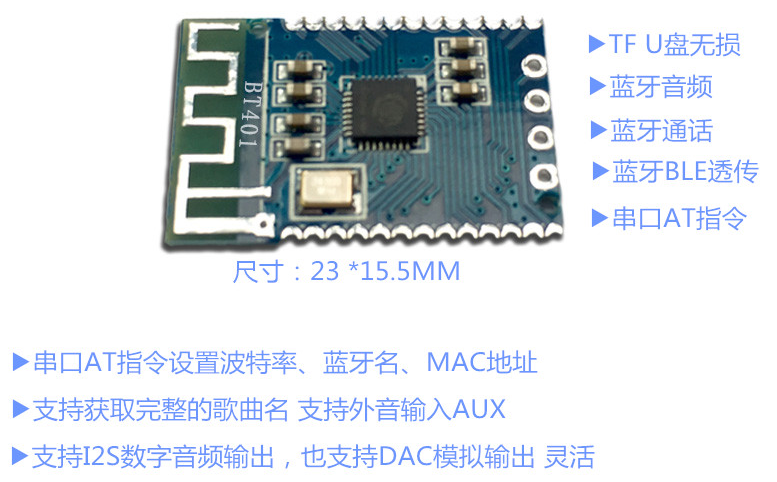

蓝牙模块BT401音频BLE串口数传的layout注意事项

Layout设计注意事项

Layout设计注意事项

评论