本文是意法半导体公司发布的关于其微控制器 EMC 设计指南的应用笔记,主要介绍了 EMC 相关定义、意法半导体微控制器的 EMC 特性、设计策略、应用的 EMC 指南以及结论等内容,旨在帮助应用设计者获得最佳 EMC 性能。

文档下载:ST微控制器EMC设计指南

*附件:an1709-emc-design-guide-for-stm8-stm32-and-legacy-mcus-stmicroelectronics.pdf

1. EMC 定义

- EMC :系统在电磁干扰下正常工作且不干扰其他设备的能力。

- EMS :器件对电气干扰和传导电气噪声的耐受能力,通过 ESD 和 FTB 测试衡量。

- EMI :设备产生的传导或辐射电气噪声水平,包括传导发射和辐射发射。

2. 意法半导体微控制器的 EMC 特性

- 电磁敏感性(EMS)

- 功能性 EMS 测试

- 功能性静电放电测试(F_ESD 测试) :对新微控制器每个引脚进行正极或负极单次放电测试,使用符合 IEC 61000 - 4 - 2 标准的 NSG 435 发生器,依据表 1 标准参考。

- 快速瞬变脉冲群测试 :通过电容耦合网络对微控制器电源线施加干扰,符合表 2 中 EN61000 - 4 - 4 / IEC 61000 - 4 - 4 标准,尖峰频率 5kHz,每 300ms 产生持续 15ms 突发尖峰(75 个尖峰)。

- 严重性级别和类别 :根据测试电压与 IEC 标准关系定义,如 ESD(IEC 61000 - 4 - 2)和 FTB(IEC 61000 - 4 - 4)测试电压对应不同严重性级别,同时根据 EN 50082 - 2 标准将 ESD 干扰下 MCU 行为分为 A、B、C、D 类,依据可接受限值和目标级别判断器件性能,相关信息在数据手册中按表 5、6 格式呈现。

- 门锁(LU)

- 绝对电气敏感性 :评估元件对 ESD 导致破坏的耐受能力,使用自动 ESD 测试仪按标准(如 JESD22 - A114A/A115A)对引脚组合放电,样本大小与供电引脚数目有关,模拟人体模型(HBM)和充电器件模型(CDM),测试后在生产测试仪上确认参数符合数据手册。

- 功能性 EMS 测试

- 电磁干扰(EMI)

3. ST MCU 设计策略和 EMC 特性

- 敏感性

- 发射

4. 基于 MCU 的应用的 EMC 指南

- 硬件

- ESD 保护的处理预防措施 :参考应用笔记 AN1181 获取详细程序。

- 固件 :参考 ST 网站专用应用笔记 AN1015。

- EMC 相关机构的网站链接 :提供 FCC、EIA、SAE、IEC、CENELEC、JEDEC 等机构网站链接。

5. 结论

开发微控制器应用时应尽早考虑 EMC 要求,ST 微控制器数据手册信息有助于选择元件,需采取硬件和固件预防措施优化 EMC 和系统稳定性。

6. EMC设计策略进行详细的整理和总结

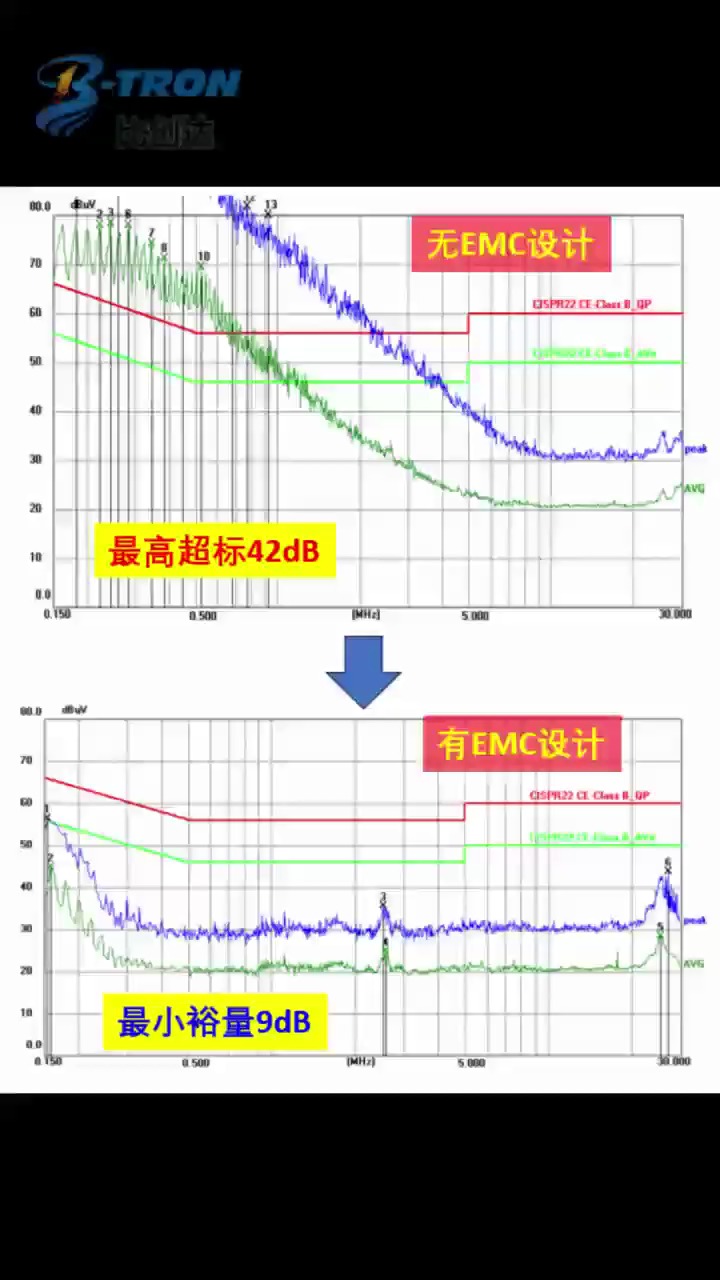

意法半导体微控制器的 EMC 设计策略涵盖敏感性和发射两个方面,旨在提高微控制器在电磁环境中的稳定性和可靠性,同时降低其对其他设备的电磁干扰。以下是对这些策略的详细整理和总结:

敏感性设计策略

- 欠压复位(BOR)

- 功能与原理 :确保微控制器始终在安全工作区内运行。当 VDD 低于最低工作 VDD 时,微控制器可能无法正常工作,而 BOR 电路在 VDD 低于特定阈值(VIT + 或 VIT - )时,会使微控制器进入复位状态,以防止不可预测行为。例如,当 VDD 上升时,低于 VIT + 时产生复位;当 VDD 下降时,低于 VIT 时产生复位。

- 迟滞特性 :设有多个迟滞级别,避免微控制器重启时发生振荡。这有助于稳定微控制器的复位过程,确保其在电源波动时能正确响应。

- 配置方式 :电压阈值可通过选项字节配置为低、中或高,以适应不同应用需求。

- 复位引脚状态 :在欠压复位期间,NRST 引脚保持低电平,允许 MCU 复位其他器件,同时也为外部复位电路提供了一种控制手段。

- 优势与应用场景 :BOR 功能使 MCU 在面对电源干扰时更加稳健,适用于对稳定性要求较高的应用场景,且在一定程度上可减少外部复位硬件的需求。

- 可编程电压检测器(PVD)

- 功能概述 :在电源受到外部噪声干扰时,提前预警并采取相应措施,确保微控制器行为安全,从而提升 EMS 性能。

- 阈值与预警机制 :PVD 阈值高于 BOR 值约 200mV,当 VDD 达到 PVD 阈值时,会生成中断,通知应用软件采取操作,如准备关闭应用或执行其他安全措施,直到电源恢复正常。

- 中断特性 :PVD 比较器输出通过实时状态位(PVDO)供应用软件读取,该位只读。中断的产生与电压上升时间(trv)有关,若 trv 不足特定 CPU 周期数,在达到 VIT+(PVD) 时可能不生成中断;若 trv 足够长,根据 PVD 中断使能的时机,可能收到一个或两个中断。

- 与 BOR 的协同工作 :与 BOR 协同工作,在电源波动时提供更精细的控制和保护,避免微控制器因电源问题出现异常。

- I/O 功能和属性

- 静电放电和闩锁防护

- 保护接口设计

- 硬件解决方案 :尽管 ST 微控制器输入 / 输出电路已考虑 ESD 和闩锁问题,但在引脚暴露于非法电压和高电流注入的应用中,建议用户采用低通滤波器和钳位二极管等硬件解决方案,防止过载损坏。

- 不同输出配置下的注意事项

- 推挽输出 :数字 I/O 引脚电路包含标准输入缓冲区和推挽配置的输出缓冲区,输出缓冲区 MOS 晶体管的二极管结构在非法电压条件下可能影响引脚行为,同时附加的 ESD 保护电路用于保护逻辑电路,但需注意其在正常工作模式下的影响。

- 开漏输出 :某些 I/O 引脚可设置为开漏输出,此时需注意外部线路电压高于 VDD 时可能通过二极管注入电流损坏器件,且在多引脚连接同一点时,应合理配置输出以避免电流争用。

- 模拟输入引脚保护 :模拟输入引脚内部电路包含数字 I/O 和模拟复用器,复用器晶体管受电源影响,需确保模拟电源和数字电源输入电压值正常,避免意外电流注入导致器件损毁。

发射设计策略

- 内部 PLL

- 时钟生成与优化 :部分微控制器内置可编程 PLL 时钟生成器,可使用标准 3 - 25MHz 晶振获取多种内部频率(最高几百 MHz),使微控制器能在使用中等频率晶振的同时,获得高频率内部时钟以提升系统性能。

- 噪声减少机制 :高频时钟源集成在芯片内部,减少了 PCB 走线和外部元件带来的潜在噪声发射,同时 PLL 网络对 CPU 时钟滤波,可抵御外部短时脉冲波干扰。

- 通用低功耗方法

- 低功耗振荡器选择

- 外部源 :使用外部时钟源时,需用占空比约 50% 的时钟信号(方波、正弦波或三角波)驱动 OSC1 引脚,OSC2 引脚接地。

- 晶振 / 陶瓷振荡器 :优点是主时钟精度高,通过选项字节选择不同频率范围的振荡器,且谐振器和负载电容应靠近振荡器引脚以减小失真和稳定时间,在复位阶段不停止,以避免启动延迟。

- 内部 RC 振荡器 :经济高效但频率精度较低,处于个位数低 MHz 范围,两个振荡器引脚接地,不同批次间存在工艺变化差异,部分微控制器有工艺补偿(可调内部 RC)可将精度提高到 1%。

- 内部调压器(适用低功耗内核 MCU)

- 供电电压调节 :从外部电源为内核供电,降低 CPU 供电电压,减少内核带来的 EMI。

- 电源隔离 :将 CPU 供电与 MCU 外部供电隔离开,进一步降低电磁干扰。

- 低功耗振荡器选择

- 输出 I/O 电流限制和边沿时间控制 :内置输出缓冲区,通过控制切换速度,在噪声和速度之间实现平衡,避免切换时产生寄生振荡,从而减少电磁发射。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

emc

+关注

关注

170文章

3927浏览量

183283

发布评论请先 登录

相关推荐

单板设计中的EMC优化策略

1板级EMC设计Openclasses成都9月20-21日随着电子信息的发展,产品的EMC要求不断提升。然而,70%的企业未设专职EMC人员,EMC设计多依赖研发人员经验和“测试修补法

EMC滤波器:原理、应用及选型指南?|深圳比创达电子EMC.

EMC滤波器:原理、应用及选型指南?|深圳比创达电子EMC随着电子设备的不断普及和电磁环境的复杂化,电磁兼容性(EMC)问题日益凸显。在电子设备中,

发表于 03-18 10:34

EMC滤波器:原理、应用与选型指南?|深圳比创达电子EMC a

景和选型指南等方面进行详细介绍。接下来就跟着深圳比创达电子EMC小编一起来看下吧!一、EMC滤波器的基本原理EMC滤波器是一种用于抑制电磁干扰的器件,其工作原理主要包括:1、滤波器分类

发表于 03-04 10:49

常见EMC器件的特性及选型分析

常见EMC器件的特性及选型分析 EMC(电磁兼容性)是指电子设备在电磁环境中正常工作,同时不对周围环境产生干扰。为了满足EMC的需求,需要选择合适的

ST MCU的 EMC 特性、设计策略、应用的 EMC设计指南

ST MCU的 EMC 特性、设计策略、应用的 EMC设计指南

评论