当前,半导体行业正在将 3.5D 作为先进封装的下一个最佳选择,这是一种混合方法,包括堆叠逻辑芯片并将它们分别粘合到其他组件共享的基板上。

这种封装模型既满足了大幅提升性能的需求,又避开了异构集成中一些最棘手的问题。它在数据中心内已经广泛使用的2.5D和芯片行业近十年来一直在努力实现商业化的全3D-IC之间建立了一个中间地带。

3.5D 架构有几个主要优势:

它创造了足够的物理分离来有效解决散热和噪音问题。

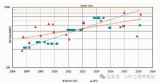

它提供了一种在高速设计中添加更多 SRAM 的方法。自 20 世纪 60 年代中期以来,SRAM 一直是处理器缓存的首选,并且仍然是加快处理速度的必要元素。但 SRAM 不再以与数字晶体管相同的速率扩展,因此它在每个新节点上占用更多的空间(以百分比计算)。而且由于光罩的尺寸是固定的,因此最好的选择是通过垂直堆叠芯片来增加面积。

通过减小处理元件和内存之间的接口,3.5D 方法还可以缩短信号需要传输的距离,并大大提高处理速度,远远超过平面实现。这对于大型语言模型和 AI/ML 至关重要,因为这些领域需要快速处理的数据量正在激增。

芯片制造商仍然认为,完全集成的 3D-IC 是平面 SoC 的最佳替代品,但将所有东西都打包成 3D 配置使得处理物理效应变得更加困难。散热可能是最难解决的问题。工作负载可能会有很大差异,从而产生动态热梯度并将热量困在意想不到的地方,从而缩短芯片的使用寿命和可靠性。除此之外,在每个新节点上,电源和基板噪声都会变得更加成问题,电磁干扰问题也是如此。

Ansys产品营销总监Marc Swinnen表示:“市场首先采用的是高性能芯片,这些芯片会产生大量热量。他们选择了昂贵的冷却系统,配备了大量风扇和散热器,并且选择了硅中介层,这可以说是连接芯片的最昂贵的技术之一。但它也能提供最高的性能,并且非常适合散热,因为它与热膨胀系数相匹配。散热是它成功的一大原因。除此之外,你可能想要更大的系统,里面有更多东西,而这些东西是无法放在一块芯片上的。这只是一个光罩尺寸的限制。另一个是异构集成,你需要多个不同的工艺,比如 RF 工艺或 I/O,而这些工艺不必在 5nm 范围内。”

3.5D 封装还提供了更大的灵活性来添加额外的处理器内核,并且由于可以单独制造和测试已知良好的芯片,因此可以实现更高的产量,这是Xilinx于 2011 年在 28nm 工艺上率先提出的概念。

3.5D 是所有这些方法的松散融合。它可以包括两到三个堆叠在一起的芯片,甚至可以包括水平排列的多个芯片。

“它的垂直方向受到限制,这不仅仅是因为散热原因,” ASE 集团研究员兼高级技术顾问Bill Chen表示。“这也是出于性能原因。但散热是限制因素,我们已经讨论过许多不同的材料来帮助解决这个问题——金刚石和石墨烯——但这个限制仍然存在。”

这就是为什么最有可能的组合(至少在最初阶段)是将处理器堆叠在SRAM上,从而简化冷却。不同处理元件的高利用率产生的热量可以通过散热器或液体冷却去除。而且,使用一个或多个变薄的基板,信号将传播更短的距离,从而使用更少的功率在处理器和内存之间来回移动数据。

“最有可能的是,这将是逻辑过程上的内存逻辑,”Arm硅操作工程研究员兼高级总监 Javier DeLaCruz 表示。“这些通常都包含在 SoC 中,但其中一部分将是 SRAM,而 SRAM 在节点之间的扩展性不是很好。因此,在内存和逻辑过程中使用逻辑才是真正的制胜解决方案,这是 3D 更好的用例之一,因为这才是真正缩短连接性的原因。处理器通常不会与另一个处理器通信。它们通过内存相互通信,因此将内存放在不同的楼层,并且它们之间没有延迟是非常有吸引力的。”

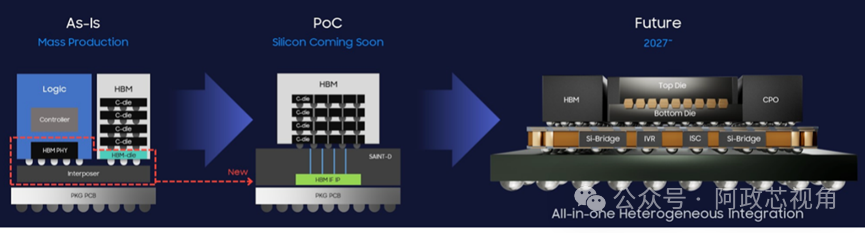

SRAM 不一定必须与处理器的先进节点处于同一节点,这也有助于提高产量和可靠性。在最近的三星代工活动中,该公司代工业务开发副总裁 Taejoong Song 展示了 3.5D 配置的路线图,明年将使用 2nm 芯片堆叠在 4nm 芯片上,2027 年将使用 1.4nm 芯片堆叠在 2nm 芯片上。

图 1:三星的异构集成路线图,显示堆叠式 DRAM(HBM)、小芯片和共封装光学器件。资料来源:三星代工厂

英特尔代工厂的方法在很多方面都很相似。英特尔高级副总裁兼代工服务总经理 Kevin O'Buckley 表示:“我们的 3.5D 技术是在带有硅桥的基板上实现的。这不是成本极高、产量低、多掩模版形状的硅,甚至不是 RDL。我们以更具成本效益的方式使用薄硅片,通过硅桥实现芯片到芯片的连接,甚至是堆叠芯片到芯片的连接。因此,您可以获得相同的硅密度优势,以及该硅桥的相同 SI(信号完整性)性能,而无需在整个硅桥下方放置巨大的单片中介层,这既成本高昂又限制了容量。它正在发挥作用。它正在实验室中运行。”

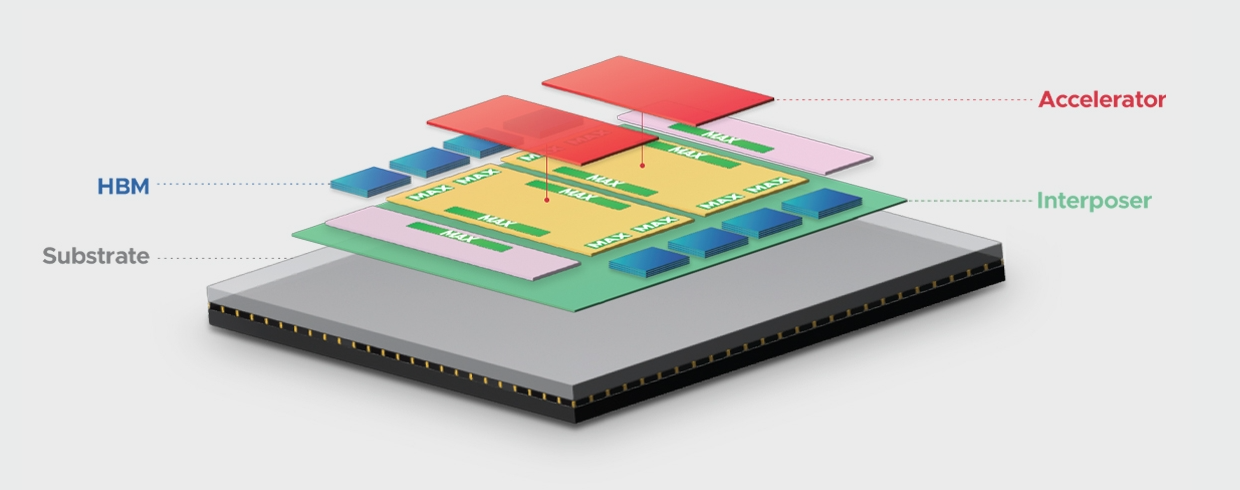

图 2:英特尔的 3.5D 模型。来源:英特尔

这里的策略部分是进化的——3.5D 至少已经进行了几年的研发——部分是革命性的,因为减薄互连层、找出处理这些更薄互连层的方法以及如何粘合它们仍在进行中。可能会出现翘曲、开裂或其他潜在缺陷,并且动态配置数据路径以最大化吞吐量是一项持续的挑战。但在两芯片和三芯片堆栈的热管理方面已经取得了重大进展。

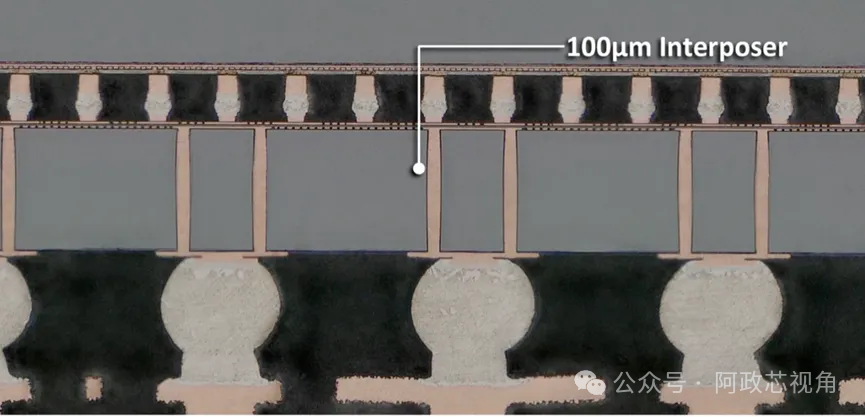

“将会有多种解决方案,”ASE 公司研发副总裁 CP Hung 表示。“例如,除了设备本身和外部散热器之外,许多人还会添加浸入式冷却或局部液体冷却。因此对于封装,您可能还会看到蒸汽室的实现,这将为设备本身和外部散热器之间添加一个良好的接口。面对所有这些挑战,我们还需要针对不同的间距。例如,如今您可以看到批量生产的间距为 45 到 40。这是一种典型的凸块解决方案。我们预计行业将转向 25 到 20 微米的凸块间距。然后,为了更进一步,我们需要混合键合,即小于 10 微米的间距。”

图 3:当今的中介层支持间距为 45m 的 100,000 多个 I/O。来源:ASE

混合键合解决了另一个棘手的问题,即数千个微凸块之间的共面性。“人们开始意识到,我们互连的密度需要一定的平整度,而制造传统键合产品的人很难以合理的产量满足这一要求,”Promex Industries首席运营官 David Fromm说。“这使得制造它们变得困难,人们的想法是,‘所以也许我们必须做点别的。’你开始看到其中的一些。”

-

封装

+关注

关注

127文章

8132浏览量

143846 -

逻辑芯片

+关注

关注

1文章

156浏览量

30766

原文标题:3.5D封装,来了!(上)

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

3.5D Chiplet技术典型案例解读

先进封装技术:3.5D封装、AMD、AI训练降本

3.5D封装来了(下)

Cadence如何应对AI芯片设计挑战

博通股价跃升 或因苹果与博通合作开发人工智能芯片的利好刺激

一颗芯片面积顶4颗H200,博通推出3.5D XDSiP封装平台

什么是3.5D封装?它有哪些优势?

MEMS传感器在汽车应用增长快速,NEMS、3.5D封装技术成趋势

芯片级封装中的3.5MHz高效升压转换器TPS6125x数据表

Chiplet&互联要闻分享 「奇说芯语 Kiwi talks」

3.5D封装来了(上)

3.5D封装来了(上)

评论