由于CPU、GPU、加速器和交换机的创新,超大规模数据中心的接口需要更快的数据传输,不仅在计算和内存之间,还涉及网络。PCI Express (PCIe®) 成为这些互连的基础,支持构建 CXL™和 UCIe™等协议。CXL提供缓存一致性互连,支持多台机器间的内存扩展,提供最低延迟和最高带宽。CXL和NVM Express®利用 PCIe 的物理层和简便的协议适应性。UCIe作为最新的Chiplet标准,也基于PCIe,支持可靠的数据传输和CXL缓存一致性。因此,PCIe 凭借其高速、低延迟和低功耗,成为处理节点之间数据传输的标准。

本文讨论了对PCI Express 6.0和未来标准的行业需求,合规性的重要性,如何通过 PHY 验证成功实现互操作性,以及针对PCIe 6.0收发器的测量方法。Synopsys的PCI Express 6.0 IP和Tektronix的测试与测量解决方案正积极应对这一最新的技术转折点。

数据速率再次翻倍

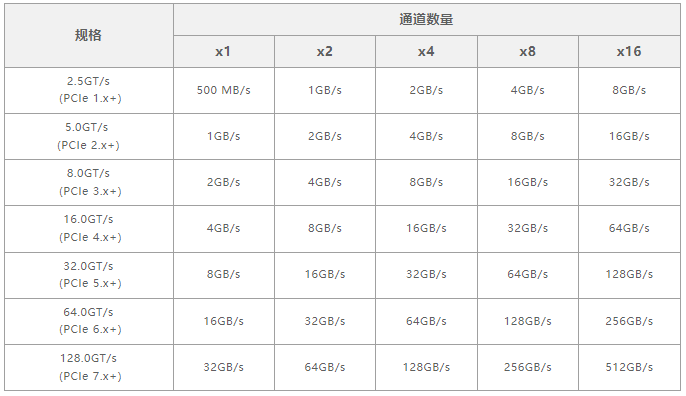

PCI-SIG® 联盟是一个由900多家成员公司组成的开放行业标准组织,每三年发布一个新的PCIe版本。过去十年中,数据速率定期翻倍并保持完全向后兼容。PCIe 6.0.1引入 PAM4信号技术,实现单通道64 GT/s传输速率,x16链路双向传输达到256GB/s。2022年,PCI-SIG宣布了PCIe 7.0规范,将数据速率提升至128GT/s,并使用1b/1b flit编码和PAM4信号技术,在16通道下实现512GB/s双向吞吐量,同时提高电源效率。除了超大规模数据中心,PCIe技术也被广泛应用于手持设备、服务器、汽车等领域,这些市场对可靠性和成本有严格要求,确保产品符合PCIe 6.0.1规范并实现互操作性是关键。

图1:PCI-SIG各代带宽

合理性和互操性测试

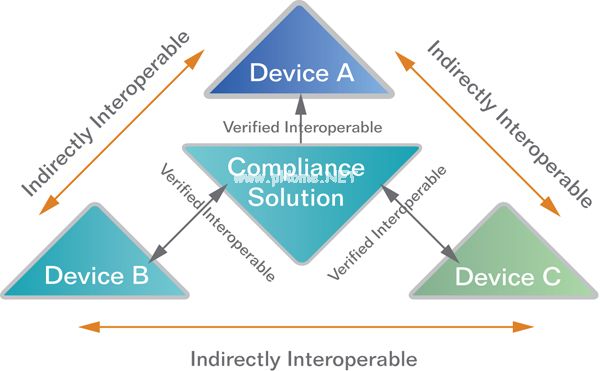

PCI-SIG的合规性和互操作性测试对于PCIe 6.0.1集成商至关重要。设计验证、PHY验证和合规性测试共同降低集成风险并提升产品质量。PCIe系统有多种拓扑,涵盖服务器、存储、GPU托架等,所有配置需满足16GHz奈奎斯特频率下的32dB插入损耗预算。具体分配为Root Complex 23.5dB,Add-in card 8.5dB,其中包括PCB走线损耗和连接器预算。因主设备与最终设备间距离最小,主板可能需更高质量的 PCB 材料和 Retimer。PCIe向后兼容性及速率升级(如64GT/s和128GT/s)增加了通道设计复杂性。

温湿度影响可致插入损耗变化,先进PCB材料变化约±10%,主流材料约±25%。开发需考虑PHY对阻抗不连续性和PVT(工艺、电压、温度)变化的补偿能力,通道均衡技术需适应并持续调整以应对环境变化,确保操作裕度。因此,与生态系统的广泛互操作性验证对确保PHY稳健性至关重要。

用于PAM4信号的新测量方法

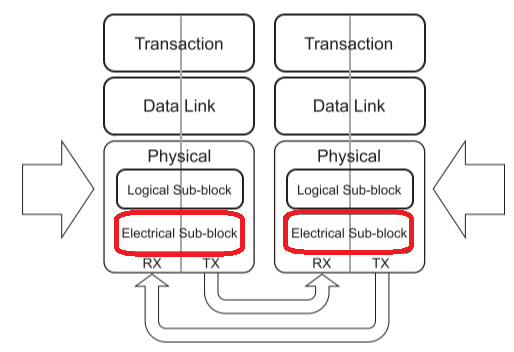

PCI Express 6.0.1基础规范将PHY层划分为逻辑子模块和电气子模块(如图2所示)。电气子模块的验证是 PHY 层全面验证的前提条件,这也是本文的重点。电气子模块包括发射器(Tx)、接收器(Rx)、参考时钟(Refclk)和通道要求。支持新的64GT/s数据速率的收发器(Tx 和 Rx)还必须保持与较低速率(2.5、5.0、8.0、16.0和32.0GT/s)的向后兼容性。在6.0.1中引入的脉冲幅度调制方法(PAM4)要求有四个不同的信号级别,这允许在一个单位间隔(UI)内传输两位信息。从NRZ(两个信号级别)到PAM4的转换确保了通道损耗与PCIe 5.0(32GT/s)保持一致,因为这两种速率的波特率都是32Gb/s,奈奎斯特频率也为16GHz。

图2:PCI Express模块图

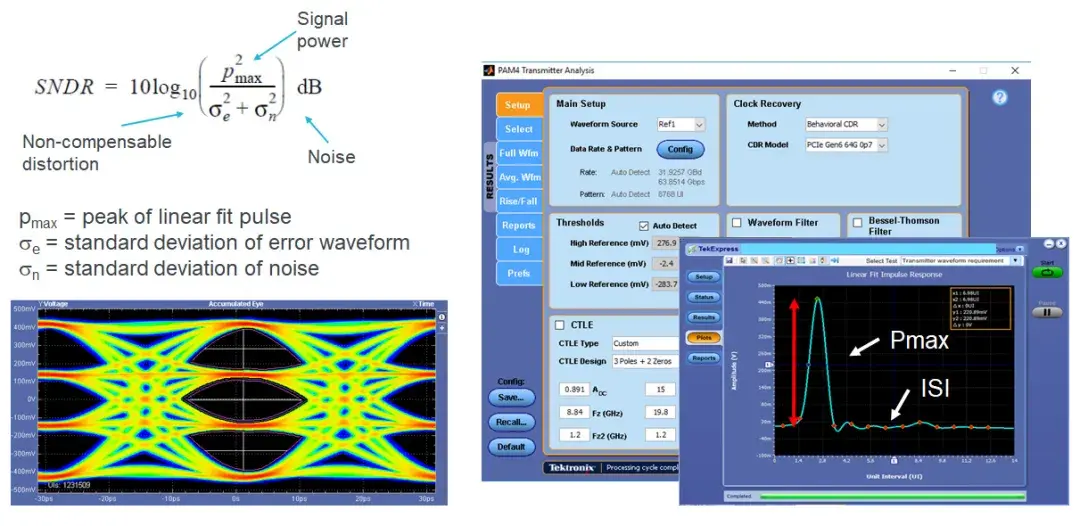

由于信号方案从NRZ变为PAM4,垂直眼图的开口减少了33%,因为我们从2个信号级别增加到4个信号级别。现在需要考虑3个眼图,而不是单个NRZ眼图。这种噪声裕度的减少加剧了串扰干扰、信号反射和电源噪声。为缓解增加的噪声敏感性,PCIe 6.0.1还采用了格雷编码以最小化比特错误,并采用预编码来减少突发错误传播。基于DAC和ADC/DSP的Tx和Rx均衡技术可以用于校正可补偿的损伤,如符号间干扰(ISI),其中相邻比特由于通道影响(包括损耗和反射)而变得模糊不清。PCIe 6.0.1规范引入了信噪失真比(SNDR)来帮助量化这一新的设计挑战。

图3:信噪失真比 (SNDR)

SNDR建立在长期以来使用的信噪比 (SNR) 测量基础之上,但引入了一个名为“σe”的变量,用于捕捉电信号中的不可补偿损伤。为了简化设计和直观理解,我们大量依赖线性模型,这些模型只是对物理世界的近似。非线性行为确实存在于PCIe收发器和通信通道中。标准通过引入SNDR的“σe”项来捕捉这种影响。这一技术借用了IEEE标准的方法,并针对64GT/s的PCIe测量进行了定制。脉冲响应是从 PRBS(伪随机二进制序列)数据模式波形创建的,使用 IEEE 的线性拟合脉冲响应方法,这成为确定信号幅度和“σe”的核心。准确的SNDR测量需要50GHz带宽的实时示波器来捕捉信号,并使用DSP软件进行波形后处理(如图3所示)。

PAM4信号中一种预期的非线性情况发生在发射信号电平不均匀间隔时。假设静态幅度,这将影响三个眼图中的一个或多个,导致比特错误增加。在后硅验证过程中对这种现象进行表征可以使收发器调整或设计更改以提高电平的线性度。为了解决这个问题,PCIe标准首次引入了电平失配比(RLM),以更好地理解和改进PAM4发射器的性能。这一基础规范测量预计将在包括CEM形态的系统级验证中扩展,CEM常用于显卡和网络接口卡 (NIC) 的实现。

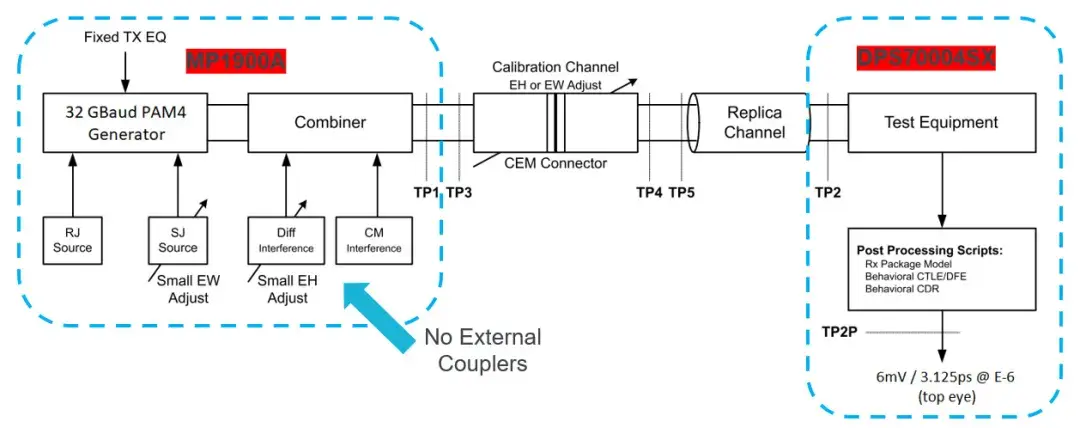

图4:受损眼校准

从电压到时序相关挑战的过渡对在最新PCIe 6.0.1数据速率下实现稳定链路具有重要意义。当信号从相邻级别(例如,从电平1到电平2)过渡时的名义斜率将小于从电平0到电平3的过渡,导致更多的垂直噪声被转移到时序抖动中。此外,由于可能的电平过渡数量的增加,眼图宽度固有地减小。高级测量仪器(例如实时示波器)的噪声表征和补偿技术首次被PCIe标准纳入考虑,以减轻与测量相关的噪声,并提高电压和时序测量(例如非相关抖动)的准确性。

为PCIe 4.0和5.0接收器建立的测量方法随着PCIe 6.0.1的Rx校准和测试得到了扩展。最差“压力眼” 信号是使用允许的最高通道损耗创建的,并传递到被测 Rx,以量化其性能。Rx 将数字化模拟信号,然后使用回环模式从相应的 Tx 重新发送比特流,以逐位比较来确定比特错误率 (BER) 或测量不同正弦抖动 (Sj) 频率的抖动容限 (JTOL)。在64GT/s下运行的接收器需要能够跟踪低于10MHz的抖动增加量和高频率下0.05 UI的抖动量。具有独立时钟的上下行端口时钟架构需要增加对33 kHz扩展频谱时钟 (SSC) 的容忍度。

压力眼信号的校准是物理层验证的复杂方面,涉及比特误差率测试仪 (BERT)、物理通道、实时示波器 (scope) 和多个DSP软件包。最终,这是对充当PCIe Tx的BERT脉冲模式发生器 (PPG) 的校准。图4显示了这个校准过程。目标是建立一个嵌入到基础规范中定义的行为接收器锁存器的眼图,其中包括时钟数据恢复器 (CDR) 和行为接收器均衡器。通过调整通道损耗、噪声和抖动来实现目标眼图,允许的顶部眼高度和眼宽度范围被找到。通道调整带来的符号间干扰 (ISI) 对眼图提供了最大的调整,而正弦抖动 (Sj) 和使用差模干扰的串扰作为微调机制。业界越来越依赖软件自动化来理解和实现接收器测试的压力眼校准。

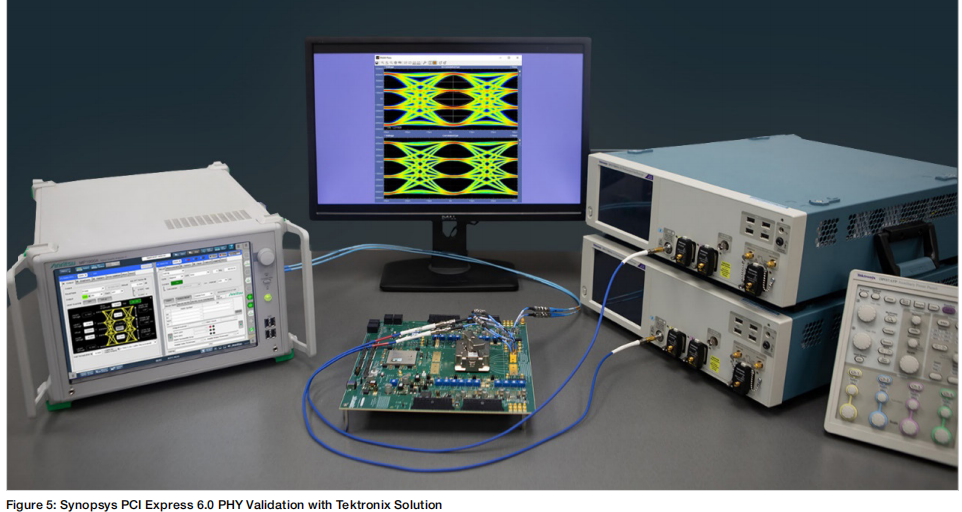

图5:使用Tektronix解决方案进行Synopsys PCI Express 6.0 PHY 验证

PCIe 6.0 解决方案

互操作性仍然是PCIe技术成功的支柱,推动了新兴技术(如 CXL)的广泛普及和采用,并被纳入未来的Chiplet(die-to-die)设计中,例如 UCIe。实现互操作性始于IP设计或选择,并涉及在基础规范和系统级别的测试,以确保来自不同供应商的设备能够正确建立链路并在不同的工作电压和温度下保持稳定。还必须考虑可制造性产品的可实现良率。例如,为了验证Synopsys的PCI Express 6.0 IP,本文所述的测试设置包括Tektronix的DPS77004SX示波器、Tektronix 的测试自动化软件以及Anritsu MP1900A BERT(如图5所示)。

Synopsys提供了涵盖该标准所有代数的完整PCI Express控制器、PHY和验证IP解决方案,这些解决方案已在客户产品中得到硅验证,目标应用包括重定时器、闪存控制器、加速器、SSD U.2/U.3、PCIe交换机和智能NIC。Synopsys IP已实现多次成功的第三方互操作性。Tektronix提供了一个完整的PCI Express 6.0基础Tx/Rx自动化解决方案,并向下兼容较低的数据速率和特定外形的测试。

审核编辑 黄宇

-

PCI

+关注

关注

5文章

690浏览量

134567 -

PCIe

+关注

关注

16文章

1496浏览量

89111 -

PHY

+关注

关注

2文章

341浏览量

54420

发布评论请先 登录

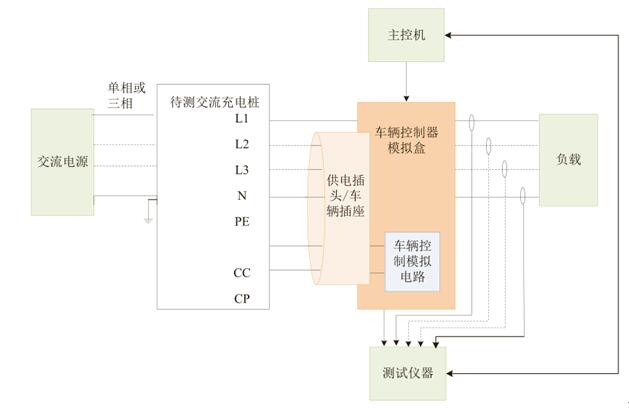

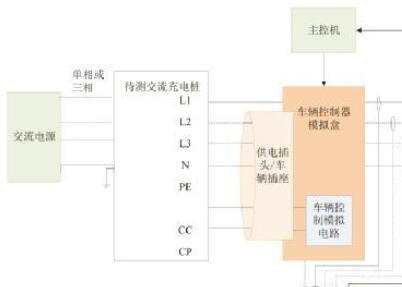

浅析交流充电桩的互操作性测试标准

10-Gbps以太网MAC和XAUI PHY互操作性硬件演示参考设计(PDF)中的说明进行操作

基于XML的现场总线设备互操作性研究

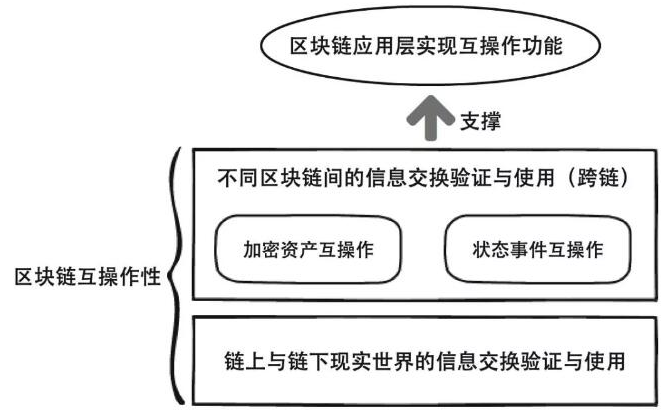

区块链互操作性是什么

PCIe 6.0 互操作性PHY验证测试方案

PCIe 6.0 互操作性PHY验证测试方案

评论