(1)集成电路封装

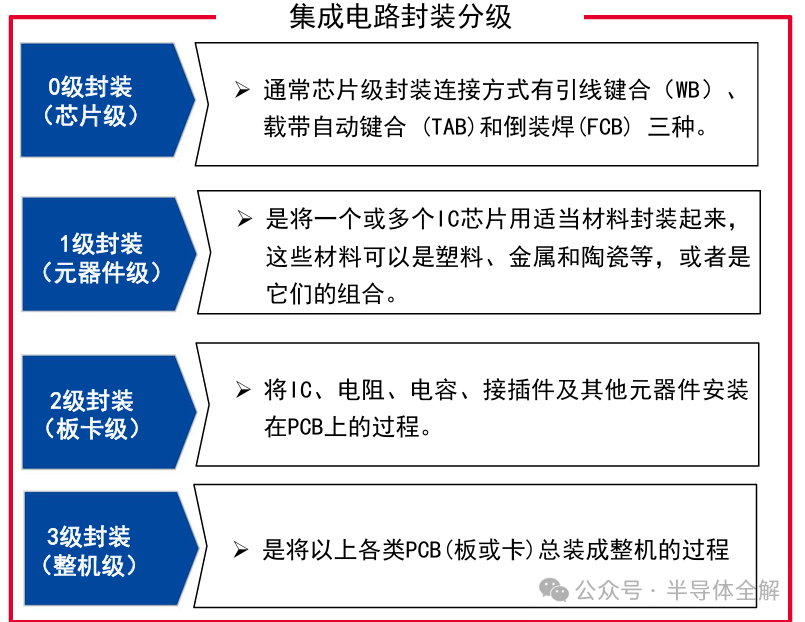

集成电路封装是指将制备合格芯片、元件等装配到载体上,采用适当连接技术形成电气连接,安装外壳,构成有效组件的整个过程,封装主要起着安放、固定、密封、保护芯片,以及确保电路性能和热性能等作用。集成电路封装一般可以分为芯片级封装(0级封装)、元器件级封装(1级封装)、板卡级封装(2级封装)和整机级封装 (3级封装)。

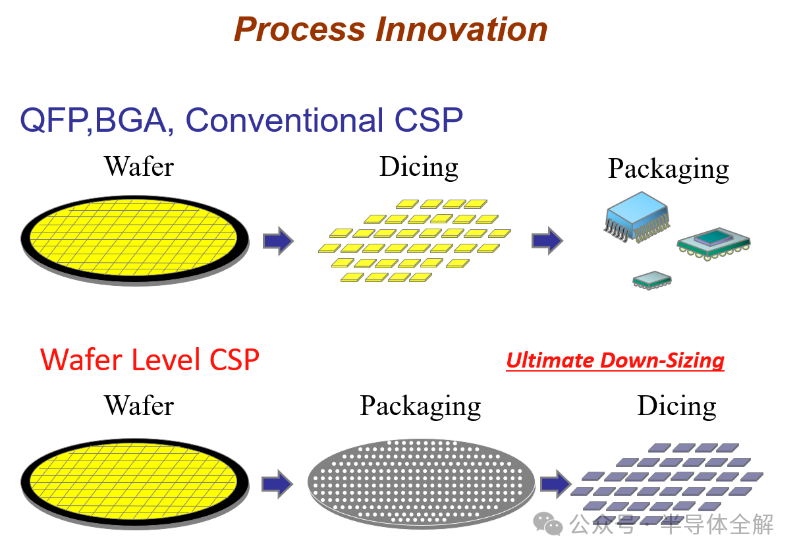

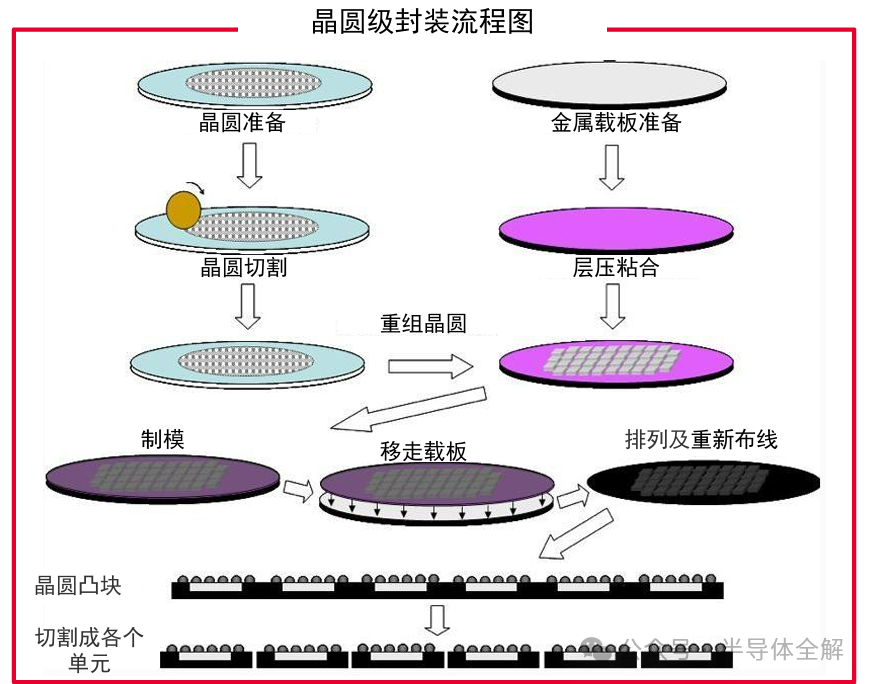

根据切割与封装顺序划分:传统封装(先从晶圆上分离出单个芯片后再进行封装);晶圆级封装(WLP,在晶圆级上进行部分或全部封装工艺,再切割成单件)。

先进封装与传统封装的最大区别在于连接芯片的方式,先进封装可在更小空间内实现更高设备密度,并使功能得到扩展。通过硅通孔、桥接器、硅中介层或导线层完成更大规模串联,从而提高信号输送速度,减少能耗。

先进封装技术通过采用更紧凑、更高级设计和制程技术,可提供更高集成度,更小尺寸,更高性能及更低能耗芯片。通过将多个芯片堆叠,在显著提高集成度及性能时,降低空间需求。在性能与能耗上,先进封装通过优化设计与制程,可大幅提高信号传输速度,降低功耗。在制程技术上,先进封装采用如微细化焊球、超低k材料等创新技术,使得封装电气性能及散热性能有显著提升。

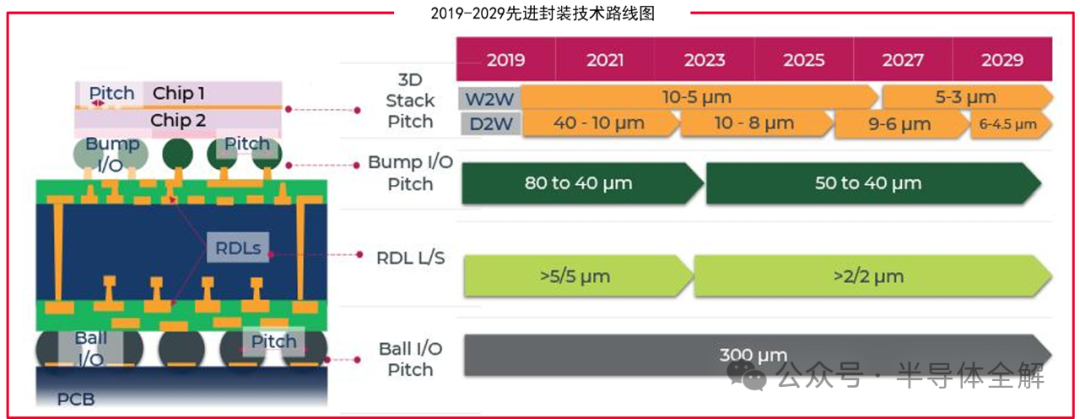

先进封装异构集成将推动半导体创新,提高整体系统性能,同时降低成本,未来3D堆叠间距将会进一步下降,Bump I/0间距将会缩小至40-50微米之间,重布层线宽间距将至2/2微米。

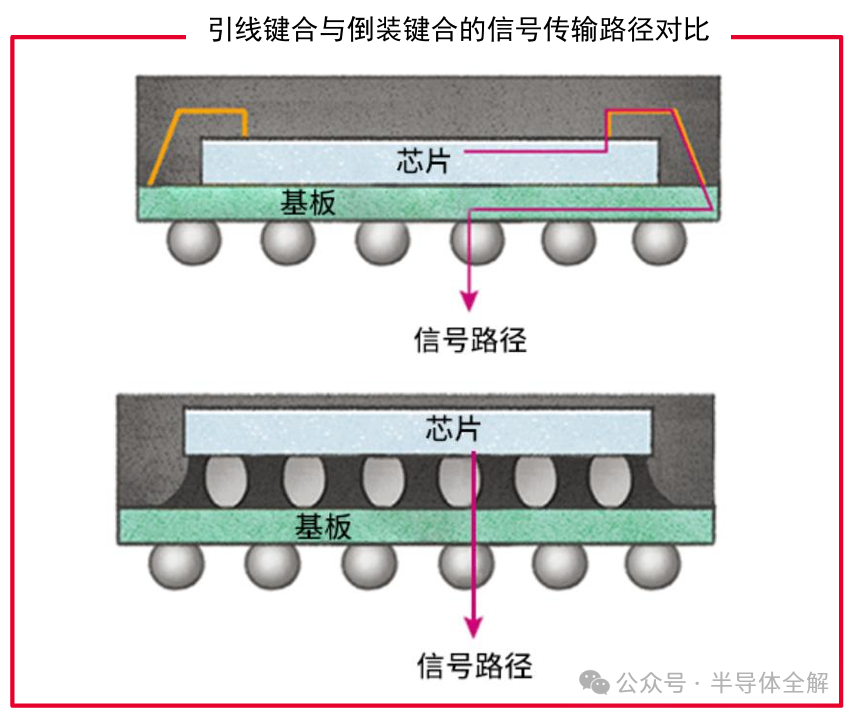

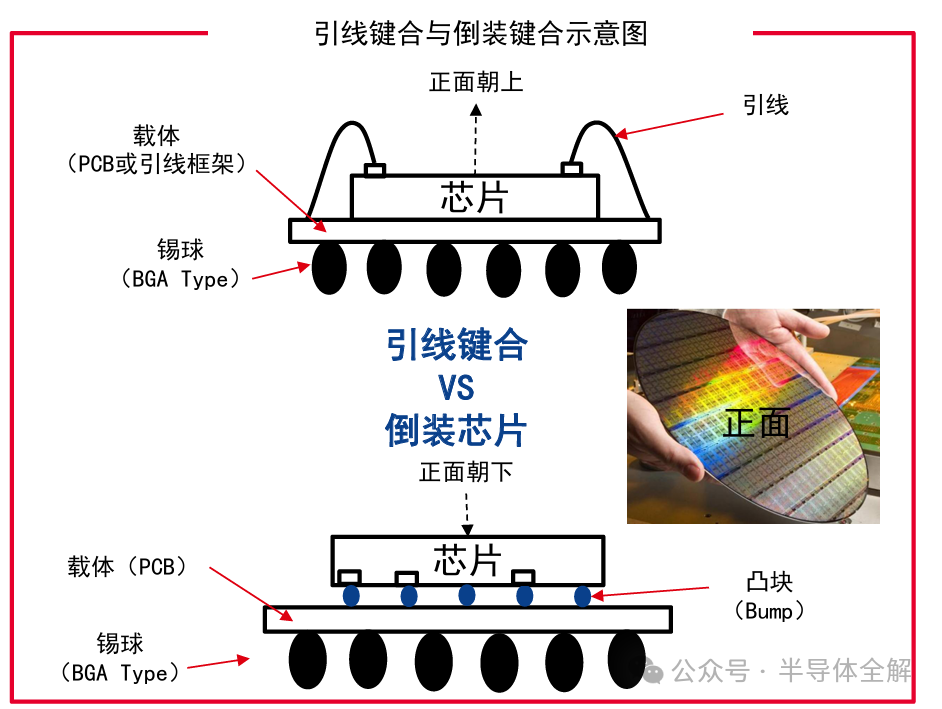

(2)先进封装技术详解 倒装是在I/O底板上沉积锡铅球,将芯片翻转加热,利用熔融锡铅球与陶瓷机板相结合来替换传统打线键合。倒装将裸片面朝下,将整个芯片面积与基板直接连接,省掉互联引线,具备更好的电气性能。

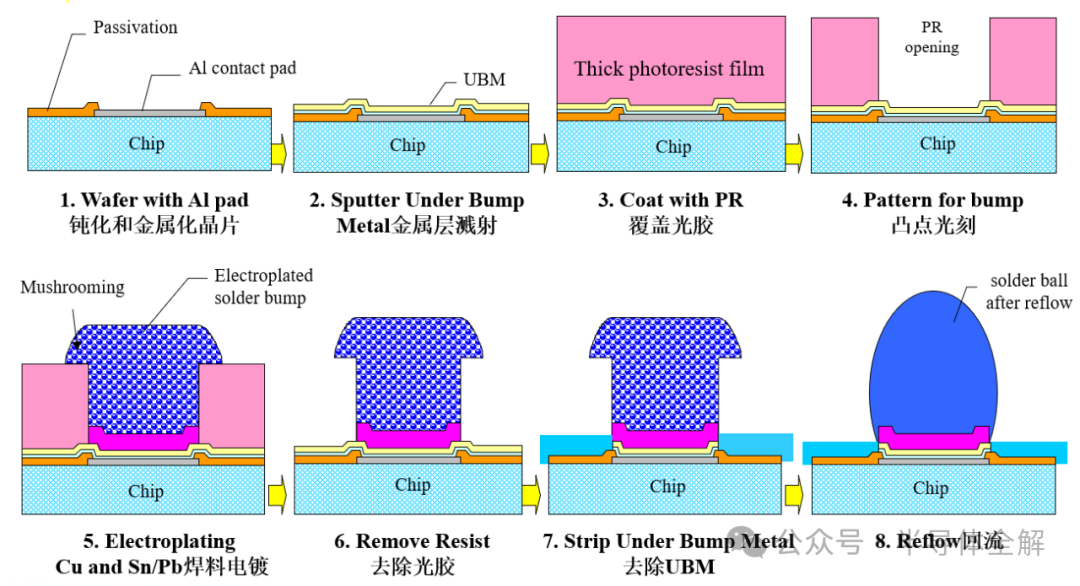

UBM是在芯片焊盘与凸点之间的金属过渡层,主要起黏附和扩散阻挡作用,通常由黏附层、扩散阻挡层和浸润层等多层金属膜组成。Bump是FC与PCB电连接唯一通道,是FC技术中关键环节。

重新布线(RDL)是将原来设计的IC线路接点位置(I/O pad),通过晶圆级金属布线工艺和凸块工艺改变其接点位置,使IC能适用于不同封装形式。

重新布线优点:可改变线路I/O原有设计,增加原有设计附加价值;可加大I/O间距,提供较大凸块面积,降低基板与元件间应力,增加元件可靠性;取代部分IC线路设计,加速IC开发时间。

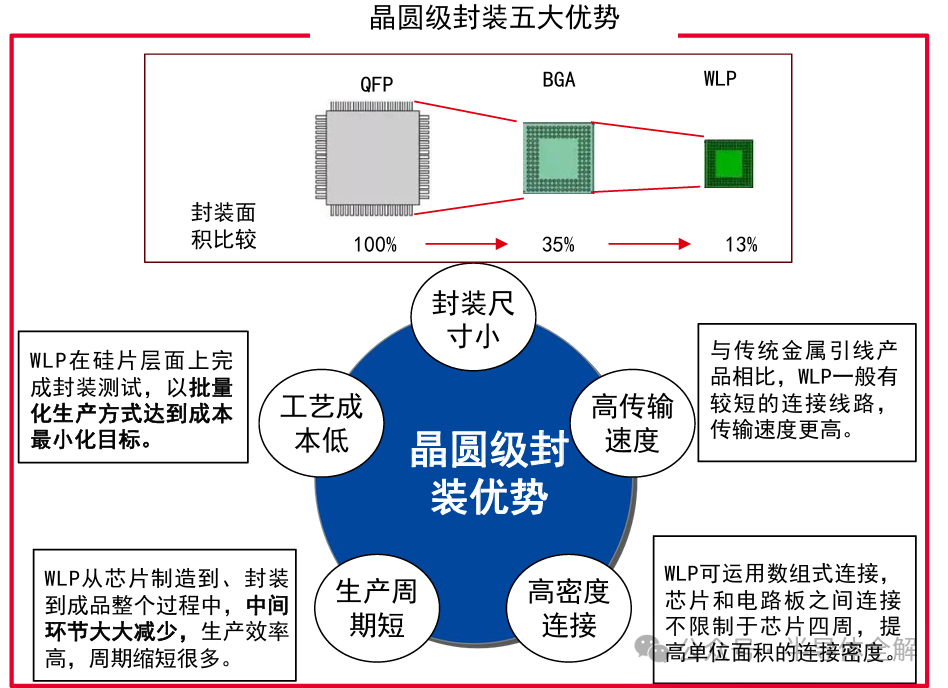

晶圆级封装是指先在整片晶圆上同时对众多芯片进行封装、测试,最后切割成单个器件,并直接贴装到基板或PCB上,生产成本大幅降低。

由于没有引线、键合和塑胶工艺,封装无需向芯片外扩展,使得WLP的封装尺寸几乎等于芯片尺寸。

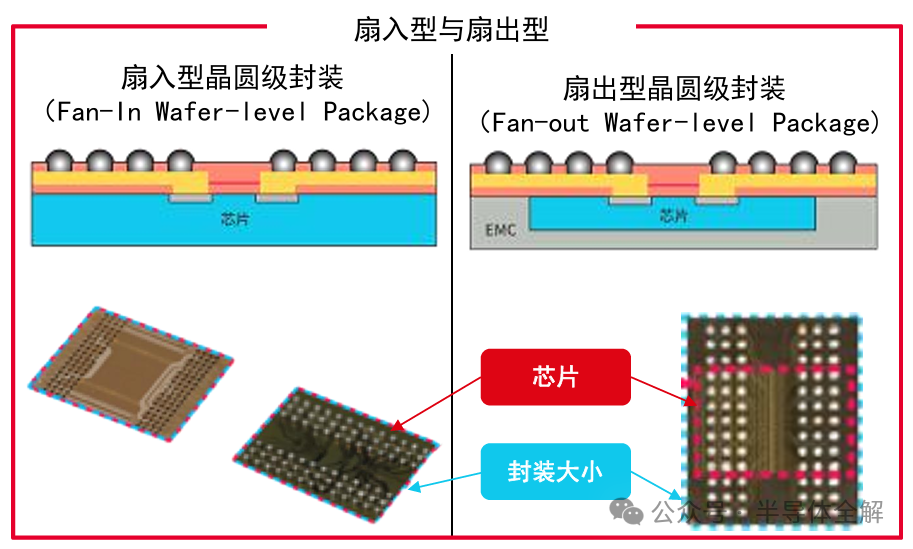

“扇(Fan)”指芯片大小。

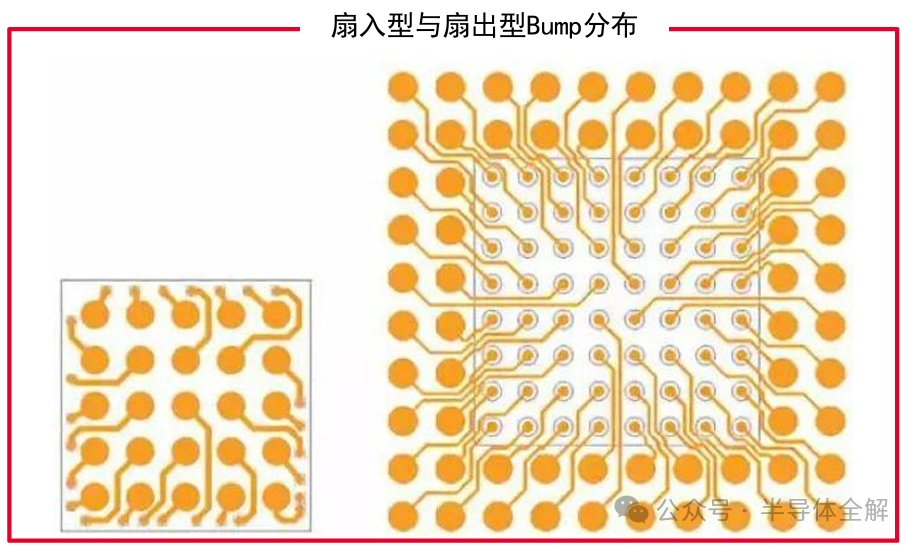

扇入型晶圆级封装(FI-WLP):芯片大小与封装大小相同,且封装用锡球在芯片大小内;

扇出型晶圆级封装(FO-WLP):封装尺寸大于芯片尺寸且部分锡球在芯片之外。

FI-WLP具有真正裸片尺寸的显著特点,通常用于低输入/输出(I/O)数量(一般小于400)和较小裸片尺寸工艺当中;

FO WLP初始用于将独立的裸片重新组装或重新配置到晶圆工艺中,并以此为基础,通过批量处理、构建和金属化结构,Fan Out的Bump可以长到Die外部,封装后IC也较Die面积大(1.2倍最大)。

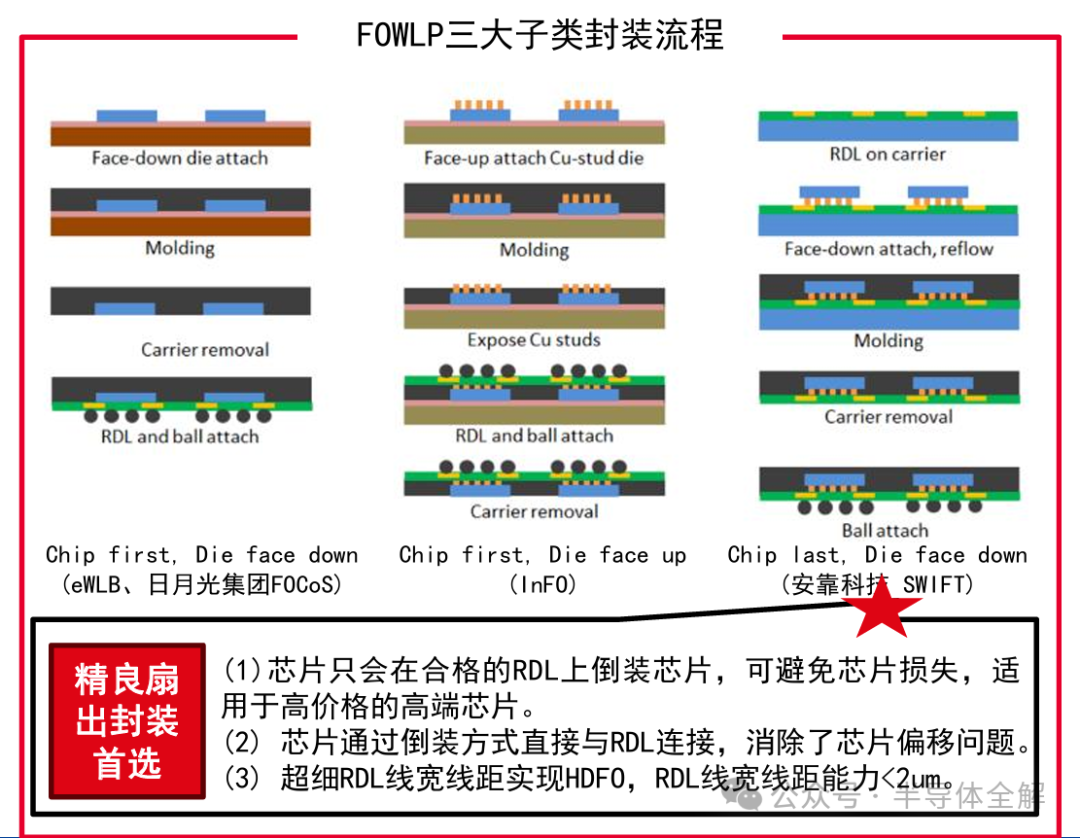

FOWLP封装技术主要分为Chip first以及Chip last(RDL first),而Chip first可再分为Die face 及Die face down。

Chip-first是在生成RDL之前,先将Die附着在一个临时或者永久材料架构上的工艺、而Chip-last则是先生成RDL,再导入 Die。封装厂商若要做出精良扇出型封装,只能采用Chip last技术路线。

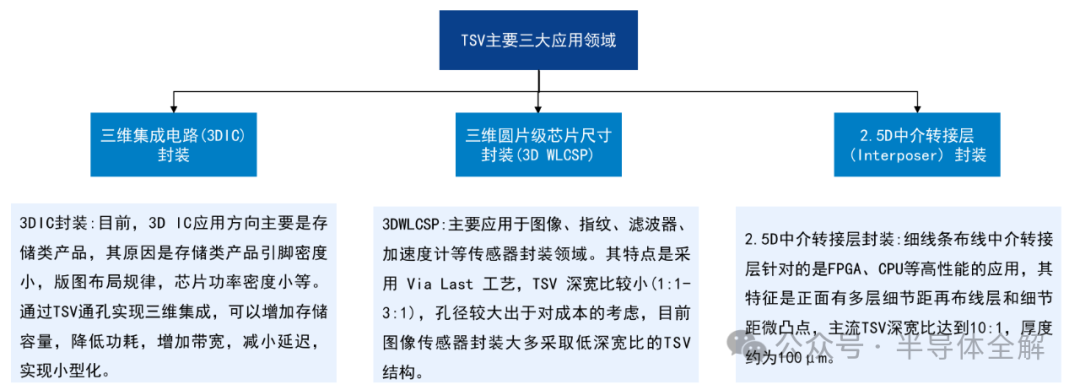

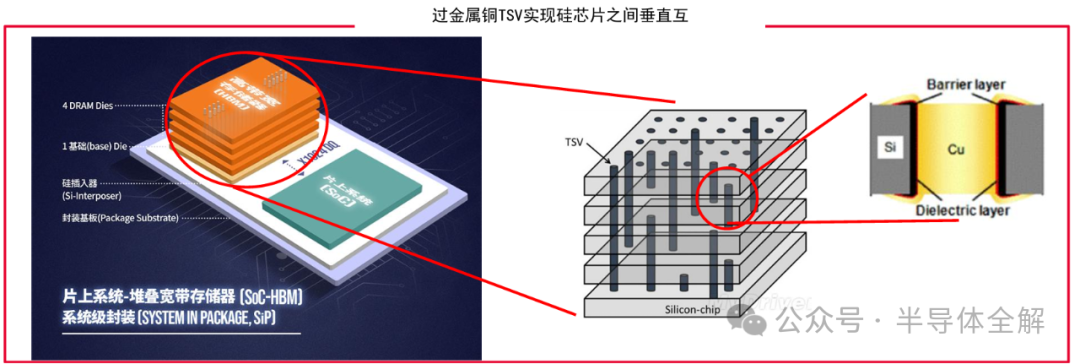

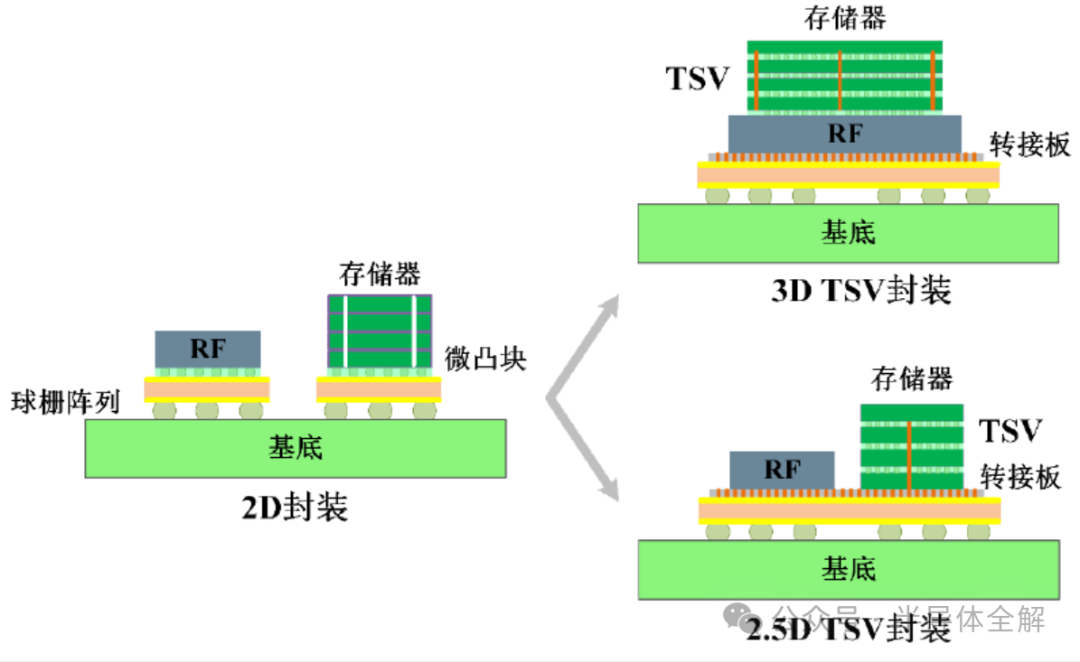

目前,TSV主要有三大应用领域,分别是三维集成电路(3D IC)封装、三维圆片级芯片尺寸封装(3D WLCSP)和2.5D中介转接层 (Interposer) 封装。

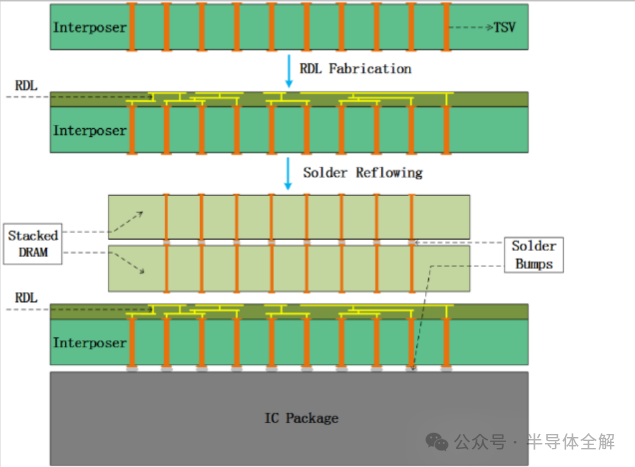

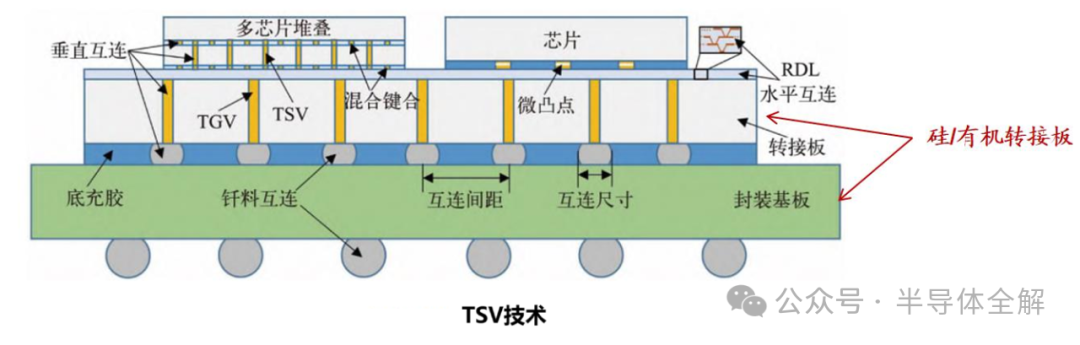

中介层是一种由硅及有机材料制成硅基板,是先进封装中多芯片模块传递电信号的管道,可以实现芯片间的互连,也可以实现与封装基板的互连,充当多颗裸片和电路板之间的桥梁。硅中介层是一种经过验证的技术,具有较高的细间距布线能力和可靠的TSV能力,可以实现高密度I/O需求,在2.5D封装中扮演着关键角色。

2.5D集成关键在于中介层Interposer:1)中介层是否采用硅转接板;2)中介层是否采用TSV,在硅转接板上穿越中介层(TSV),在玻璃转接板上穿越中介层(TGV)。

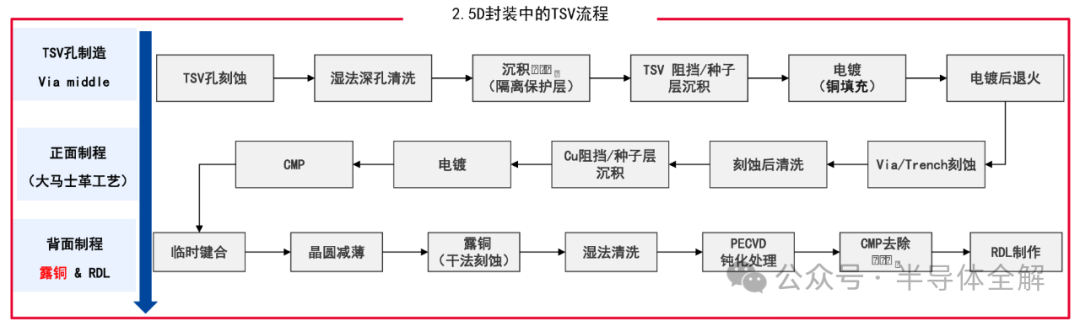

TSV生产流程涉及到深孔刻蚀、PVD、CVD、铜填充、微凸点及电镀、清洗、减薄、键合等二十余种设备,其中深孔刻蚀、气相沉积、铜填充、CMP去除多余金属、晶圆减薄、晶圆键合等工序涉及的设备最为关键。

TSV工艺流程:深反应离子刻蚀(DRIE)法行成通孔;使用化学沉积方法沉积制作绝缘层、使用物理气相沉积方法沉积制作 阻挡层及种子层;选择一种电镀方法在盲孔中进行铜填充;使用化学和机械抛光(CMP)法去除多余铜,完成铜填充后, 则需要对晶圆进行减薄,最后是进行晶圆键合。

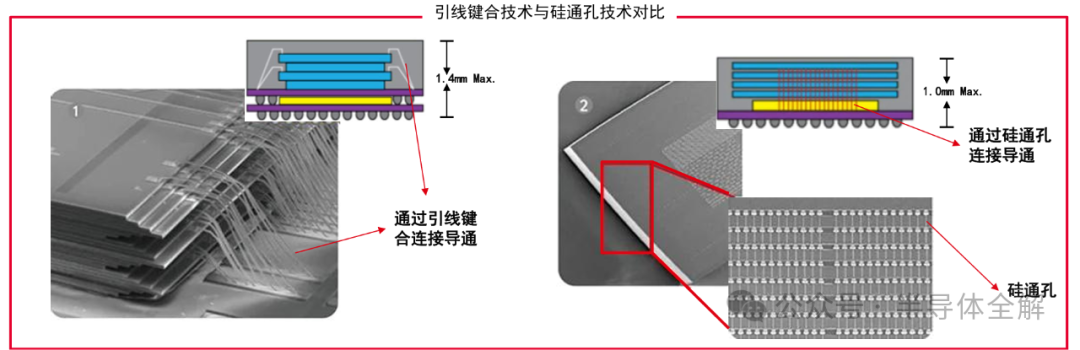

硅通孔是一种通过在硅片上钻孔来容纳电极芯片堆叠技术。相比采用传统引线方法实现芯片与芯片(Chip-to-Chip)互连或芯片与基板(Chip-to-Substrate)互连,硅通孔通过在芯片上钻孔并填充金属等导电材料来实现芯片垂直互连。

硅通孔封装主要优势在于性能优越且封装尺寸较小。使用引线键合芯片堆叠封装利用引线连接至各个堆叠芯片侧面,随着堆叠芯片以及连接引脚(Pin)数量增加,引线变得更加复杂,且需更多空间来容纳引线。相比之下,硅通孔芯片堆叠则不 需要复杂布线,因而封装尺寸更小。

HBM是一种封装存储器,可通过同一封装内的硅中介层与SoC集成在一起。通过这种方法,便可以克服传统片外封装存在的数据I/O封装引脚限制的最大数量。DRAM通过堆叠的方式,叠在一起,Die之间用TVS方式连接;DRAM下面是DRAM逻辑控制单元,对DRAM进行控制;GPU和DRAM通过uBump和Interposer (起互联功能的硅片)连通Interposer再通过Bump和 Substrate(封装基板)连通到BALL;最后BGA BALL 连接到PCB上。

2.5D封装:将处理器、记忆体或是其他芯片,并列排在硅中介板上,经由微凸块连结,让硅中介板之内金属线可连接不同芯片电子讯号;再透过硅穿孔(TSV)来连结下方金属凸块,再经由导线载板连结外部金属球,实现芯片、芯片与封装基板之间互连。

3D集成和2.5D集成的主要区别在于:2.5D封装是在中介层Interposer上进行布线和打孔,而3D封装是直接在芯片上打孔和布线,连接上下层芯片。

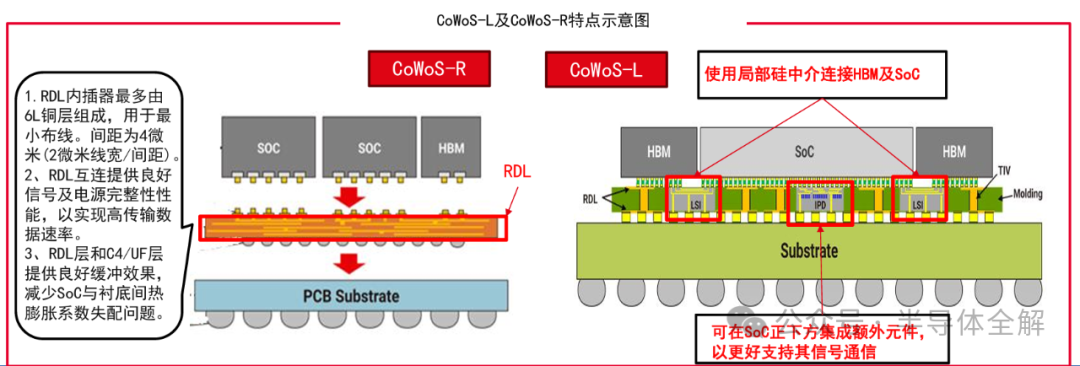

CoWoS实质为2.5D封装,依据中介层采用不同技术划分为CoWoS-S、CoWoS-L及CoWoS-R三大技术。CoWoS-S采用硅中介层,为高性能计算应用提供最佳性能及最高晶体管密度;CoWoS-R类似InFO技术,利用RDL中介层进行互连,更强调小芯片间互连;CoWoS-L结合CoWoS-S及InFO技术优点,使用夹层与LSI(局部硅互连)芯片进行互连,使用RDL层进行电源与信号传输,提供最灵活集成。

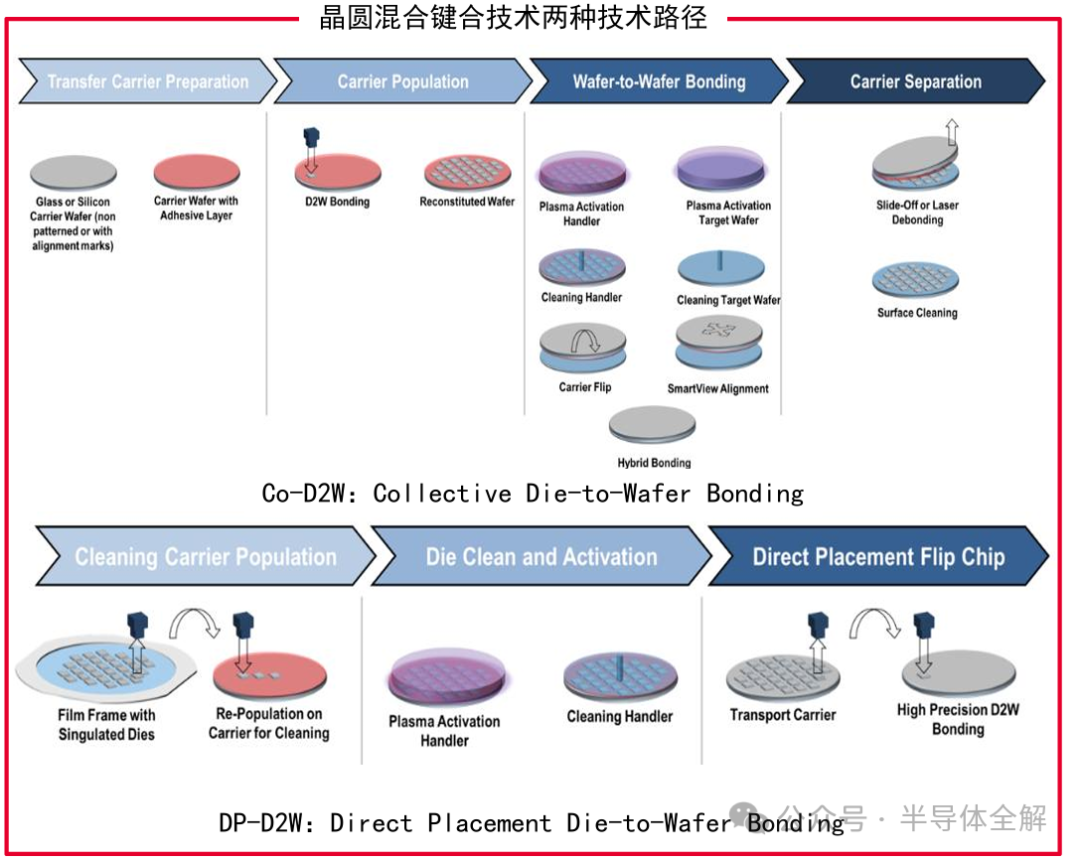

混合键合是通过分子间作用力(范德华力) 实现,使用化学机械抛光对大马士革布线层进行表面处理,CMP过程还可以减少Cu线路腐蚀和Cu凹陷。当Cu和Si的光滑界面相互接触时形成范德华力。为增强表面结合力,通常需要增加等离子体活化工序,然后再通过高精度倒装热压工序,实现多界面之间混合键合。

HybridBonding技术最早实际应用于SONY公司高端 CMOSImage Sensor产品。通过把图像传感器晶圆、 数据存储及处理芯片的晶圆直接键合,实现大规模图像数据高效并行传输,后来该技术被广泛应用于 逻辑芯片及存储芯3D互连。由于需要解决不同裸片尺寸芯片间直接键合,混合键合应用从Wafer toWafer(W2W)基础上发展出Die to Wafer(D2W), 即将切割好裸片一个个贴到另一个完整晶圆上,和晶圆上的裸片实现键合。

Co-D2W:将切割好Die用临时键合方式粘到Carrier 晶圆上,随后整片和另一片产品晶圆整片键合再解键。该技术类似于W2W,相对成熟,但一次D2W叠加一次W2W方式容易累计误差,Carrier晶圆处理成本高,且对Die厚度变化范围有较高要求。

DP-D2W:将切好Die一颗颗放置于另一片产品晶圆对应位置。该路线位置精度将会提高且对Die厚度变化容忍度高,但有颗粒控制等问题。

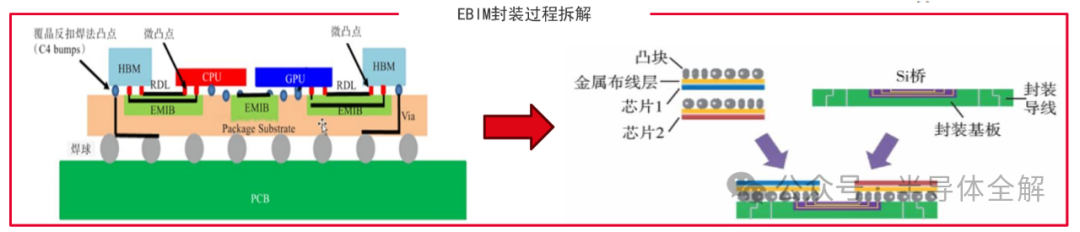

EMIB是将带有多层导电金属(back end of line,BEOL)互连的超薄硅片埋入有机封装基板的最上层,通过焊球与倒装芯片的连接,以实现两个或多个芯片之间的局部高密度互连。与传统封装中在基板表面贴装芯片或元件不同,板级埋入式封装直接将芯片或元件嵌热性能及更高的集成度。

-

集成电路

+关注

关注

5388文章

11563浏览量

362082 -

封装

+关注

关注

126文章

7934浏览量

143056

原文标题:一文详解集成电路封装发展历程

文章出处:【微信号:wc_ysj,微信公众号:旺材芯片】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

集成电路封装技术专题 通知

集成电路电源芯片的分类及发展

世界集成电路发展历程及产业结构的变化

环境与静电对集成电路封装的影响

集成电路是什么_集成电路封装_集成电路的主要原材料

林仲珉带着集成电路封装技术回归,助国内封装行业发展

2022年中国集成电路封装行业龙头企业对比:谁是封装之王?

集成电路封装的发展历程

集成电路封装的发展历程

评论