倒掺杂阱(Inverted Doping Well)技术作为一种现代半导体芯片制造中精密的掺杂方法,本文详细介绍了倒掺杂阱工艺的特点与优势。

在现代半导体芯片制造中,倒掺杂阱(Inverted Doping Well)技术作为一种精密的掺杂方法,对于实现高性能和高密度的集成电路至关重要。倒掺杂阱工艺通过精确控制掺杂深度和横向扩散,有效改善了闩锁效应和DIBL(drain induced barrier lowering)同时降低了电流在阱等效电阻上的压降,并且能够灵活调节阈值电压以优化器件性能和亚阈值漏电流,从而显著提升了芯片的可靠性和性能,有利于制造高密度、高性能的先进半导体器件。

倒掺杂阱工艺的特点与优势:

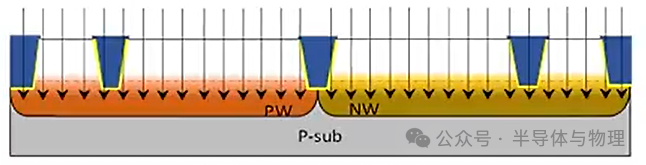

1、阱离子注入

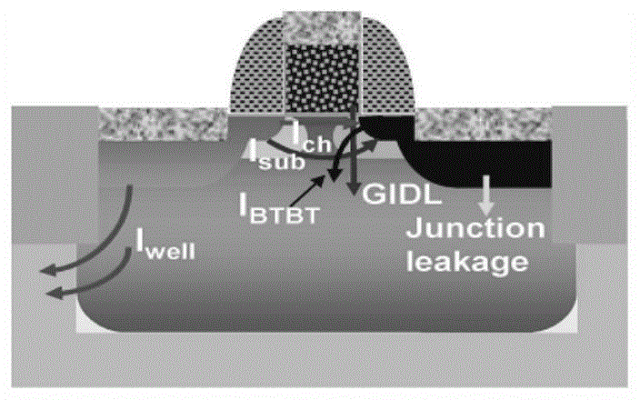

改善闩锁效应:大掺杂浓度的深层阱区可以降低阱的等效电阻,减少电流通过时的压降,有效缓解闩锁效应(Latch-up),即两个寄生双极型晶体管之间的正反馈导通现象。

减小耗尽区宽度:增大掺杂浓度可以缩小漏极与衬底(或阱)间的耗尽区宽度,进而减轻DIBL(Drain Induced Barrier Lowering,源-栅电压引起的阈值电压降低)效应,提高短沟道器件的性能。

特点:采用高能量和高浓度的离子注入,峰值浓度通常出现在几微米的深度。

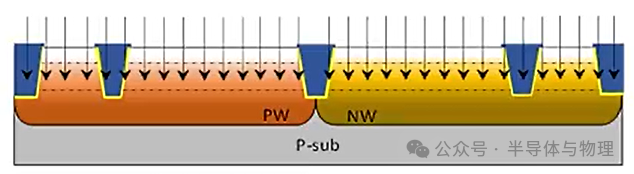

2、沟道离子注入

优化DIBL效应:适当调节沟道掺杂浓度能够减小源和漏耗尽区宽度,进一步改善DIBL效应。

载流子迁移率折衷:增加沟道掺杂浓度虽然有助于减小DIBL效应,但也会因为库仑散射增加而降低载流子迁移率,最终影响器件速度。因此,在提升器件穿通特性和保持高速度之间需要找到一个平衡点。

特点:使用中等能量和中等浓度的离子注入,目标区域位于高掺杂阱区上方的沟道部分,紧邻源和漏有源区。

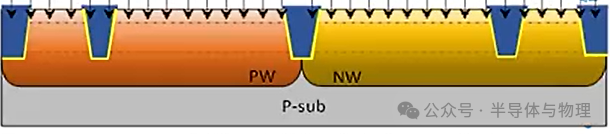

3、阈值电压离子注入

阈值电压调控:沟道表面附近的掺杂浓度直接决定了阈值电压的高低,通过精准调控这一参数,可以设计出不同阈值电压级别的晶体管,如高、中、低阈值电压器件。

亚阈值漏电流管理:随着阈值电压的升高,亚阈值区的漏电流会相应减少;反之,则会增加。这为工程师提供了灵活的设计空间,以满足特定应用的需求。

特点:利用低能量和低浓度的离子注入,重点在于沟道表面附近的掺杂浓度调整

-

半导体

+关注

关注

334文章

27442浏览量

219454 -

芯片制造

+关注

关注

10文章

624浏览量

28837

原文标题:离子注入:倒掺杂阱

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

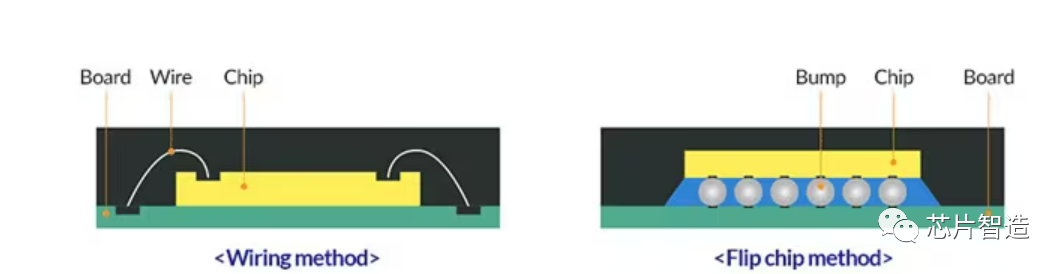

倒装封装(Flip Chip)工艺:半导体封装的璀璨明星!

半导体芯片制造中倒掺杂阱工艺的特点与优势

半导体芯片制造中倒掺杂阱工艺的特点与优势

评论