如今,算力极限挑战正推动着芯片设计的技术边界。Chiplet的诞生不仅仅是技术的迭代,更是对未来芯片架构的革命性改变。然而,要真正解锁Chiplet技术的无限潜力,先进封装技术成为了不可或缺的关键钥匙。

Chiplet:

超大规模芯片突破的关键策略

面对全球范围内计算需求的爆炸性增长,高性能芯片市场正以前所未有的速度持续扩张。在这一背景下,Chiplet技术以其独到的设计理念与先进的封装工艺,成为了突破传统单芯片设计局限性的关键钥匙。通过将多个高性能芯粒(Chiplet)巧妙集成,Chiplet技术不仅重塑了芯片设计的版图,更为整个芯片产业开辟了一条全新的发展路径。

作为推动算力跃升的前沿技术,Chiplet展现出了多方面的显著优势。

Chiplet技术可以克服算力墙、存储墙、光罩墙、功耗墙四方面的限制,是突破先进制程瓶颈的有效手段。

Chiplet基于硅片级IP重构和复用的新架构,给缩短产品研发周期、提升良品率、降低成本等方面带来巨大优势。

Chiplet的异质异构、跨尺度封装特点,集成芯片在尺寸、功能密度、总/局部功率密度、IO数量/密度/速率、互连带宽/密度、热流密度、时延、单位bit功耗等关键指标具有显著提升空间,可有效满足各类应用场景。

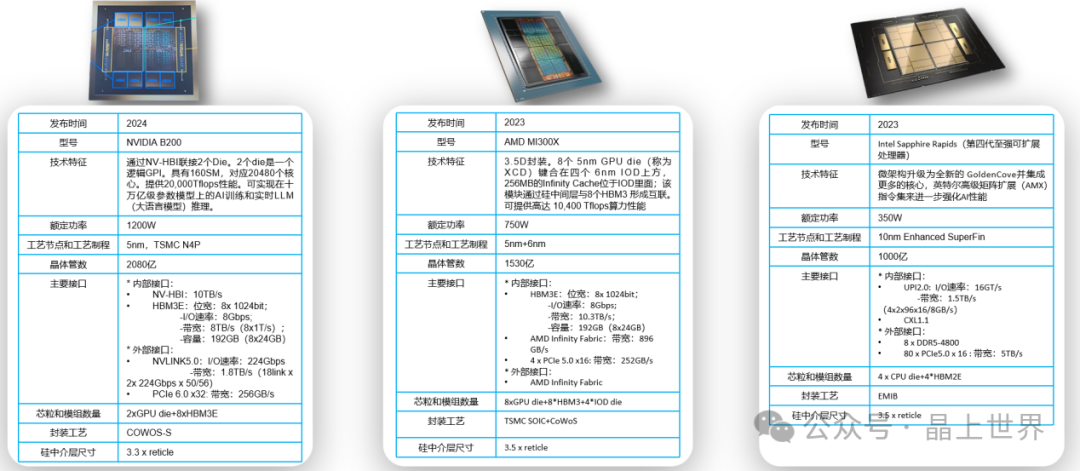

近两年,随着国际大厂纷纷将Chiplet技术应用于其最新产品之中,超大规模芯片采用Chiplet设计已蔚然成风。

Chiplet实现的关键

——先进封装

Chiplet技术的核心理念,在于通过先进封装技术的精妙运用,实现大芯片的“化零为整”。因此,先进封装对于Chiplet而言,不仅是技术实现的基础,更是决定其未来发展空间与深度的关键技术。

Chiplet封装应用形式分为同构和异构。

同构目前主要封装形式为2D方案,即MCM,核心为D2D模块,是通过将多个独立的芯片(Chiplet)直接并排或堆叠在同一封装基板上,利用引线键合(Wire Bonding)、倒装芯片(Flip-Chip)或其他互连技术实现芯片间的电气连接。

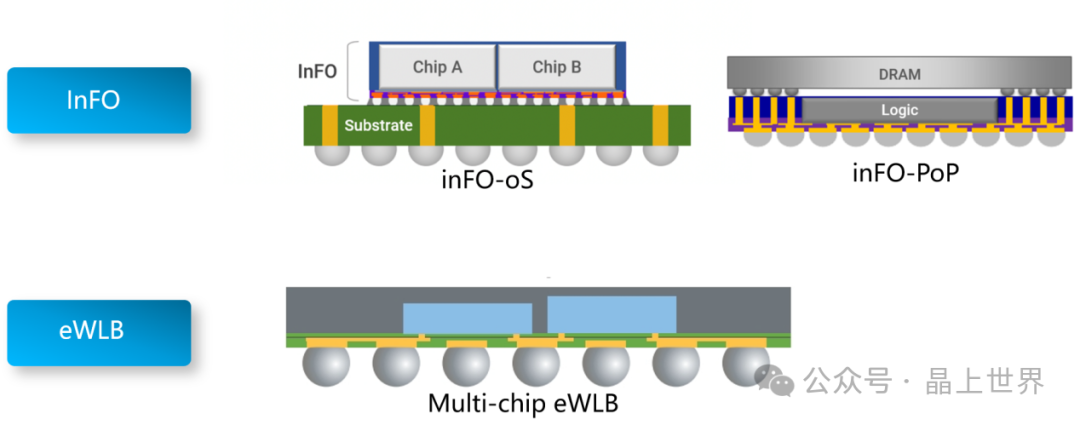

代表性封装技术:

TSMC InFO:InFO是TSMC开发的一种扇出型晶圆级封装技术。该技术通过去除传统的封装基板,直接在晶圆上进行封装,从而实现更薄、更轻、成本更低的封装解决方案。

日月光 eWLB:eWLB封装技术是一种创新的晶圆级封装技术,由日月光半导体等公司开发并推广。该技术将晶圆直接嵌入到封装基板中,并通过重新布线层(RDL)实现芯片间的互连。eWLB封装技术结合了晶圆级封装的高密度和低成本优势。

异构目前主要封装形式为2.5D,以HBM应用为主,核心为控制模块和HBM颗粒。代表性封装方案主要分为三类:

2.5D硅中介层

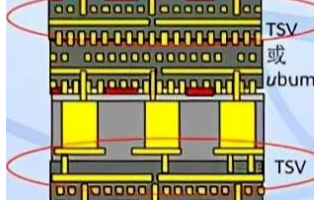

2.5D硅中介层封装技术是通过在两个或多个芯片之间插入一个硅材质的中间层(即硅中介层),来实现芯片间的互连。这种技术可以有效缩短芯片间的互连距离,提高数据传输速度和带宽,同时降低功耗和延迟。硅中介层上集成了大量的微凸点(microbumps)或TSV(Through Silicon Via,硅通孔)来实现芯片与中介层之间的电气连接。

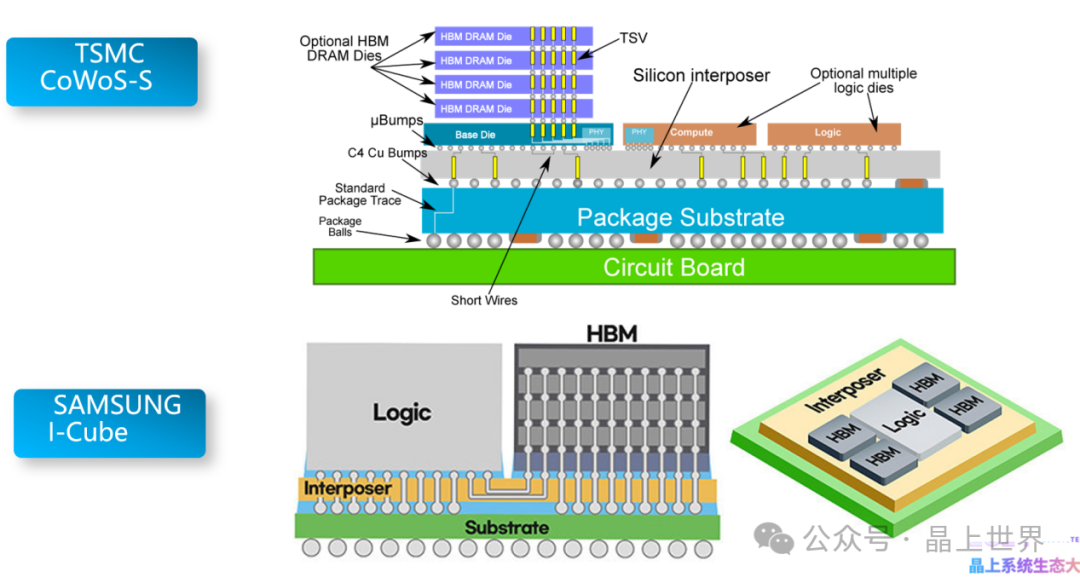

代表性封装技术:

TSMCCoWoS-S:这是台积电(TSMC)推出的一种基于硅中介层的Chiplet封装技术,其中“CoWoS”代表Chip-on-Wafer-on-Substrate,即芯片-晶圆-基板封装。该技术利用硅中介层来连接多个高性能芯片,并通过微凸点或TSV实现高密度互连。

Samsung I-Cube:三星(Samsung)的Cube技术也是基于硅中介层的Chiplet封装方案,它采用了先进的堆叠和互连技术,将多个芯片封装在一个紧凑的立方体中,以实现高性能和低功耗。

2.5D硅桥

2.5D硅桥封装技术通过直接在芯片之间构建硅桥来实现互连,而不需要额外的硅中介层。这种技术可以减少封装尺寸和成本,同时保持较高的数据传输速率和带宽。硅桥通常通过TSV技术实现,确保芯片间的高效电气连接。

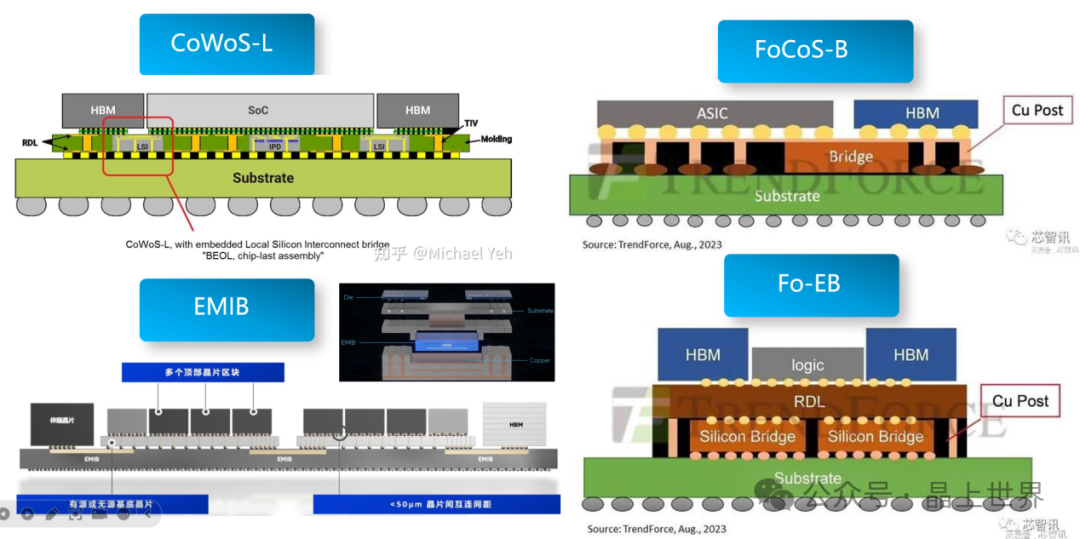

代表性封装技术:

TSMCCoWoS-L:这是TSMC CoWoS系列中的一种变体,特别优化了硅桥技术,以实现更紧密的芯片间连接。该技术适用于需要高带宽和低延迟的应用场景,如高速网络接口、高性能存储等。

Intel EMIB:Intel推出的EMIB技术是一种创新的硅桥封装方案,它允许将多个芯片直接嵌入到封装基板上,并通过嵌入式硅桥实现高速互连。该技术提高了系统的集成度和性能,降低了功耗和延迟。

FoCoS-B和Fo-EB:日月光集团推出的FoCoS-B和Fo-EB也是基于硅桥技术的Chiplet封装方案,尽管它们可能不如上述技术广为人知,但在特定领域或应用中仍具有优势。

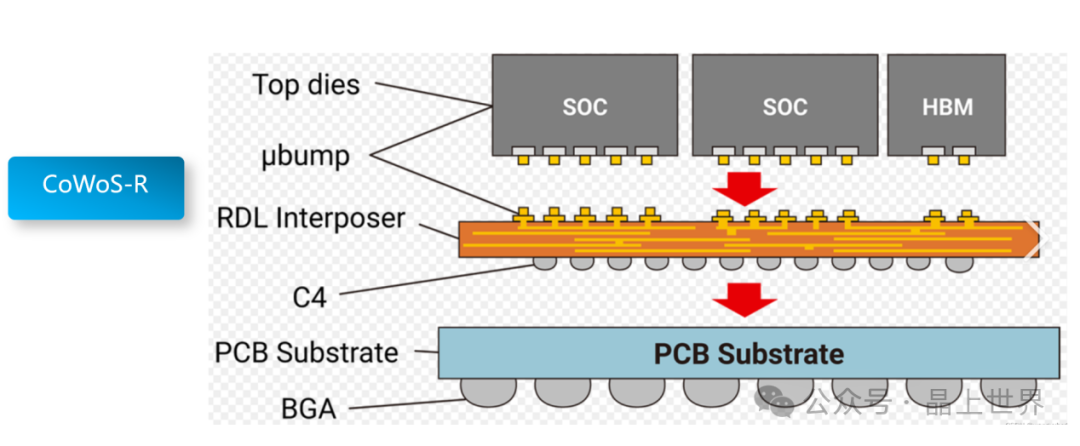

2.5D RDL中介层

2.5D RDL中介层封装技术利用RDL在硅中介层上构建复杂的互连网络。RDL层可以包含多层金属布线,用于实现芯片间的高密度、高性能互连。这种技术结合了硅中介层的优势,同时提供了更灵活的布线能力和更高的集成度。

代表性封装技术:

CoWoS-R:作为TSMC CoWoS系列的一部分,CoWoS-R特别强调了RDL中介层的应用。该技术通过精细的RDL布线,实现了芯片间的高效互连,适用于对性能、功耗和尺寸有严格要求的高端应用。

Chiplet可以通过多种先进封装技术实现,其中2.5D封装技术尤为突出。随着Chiplet的发展和封装技术的迭代,Chiplet+先进封装技术组合将在满足多样化应用需求方面带来更多的创新和变革。

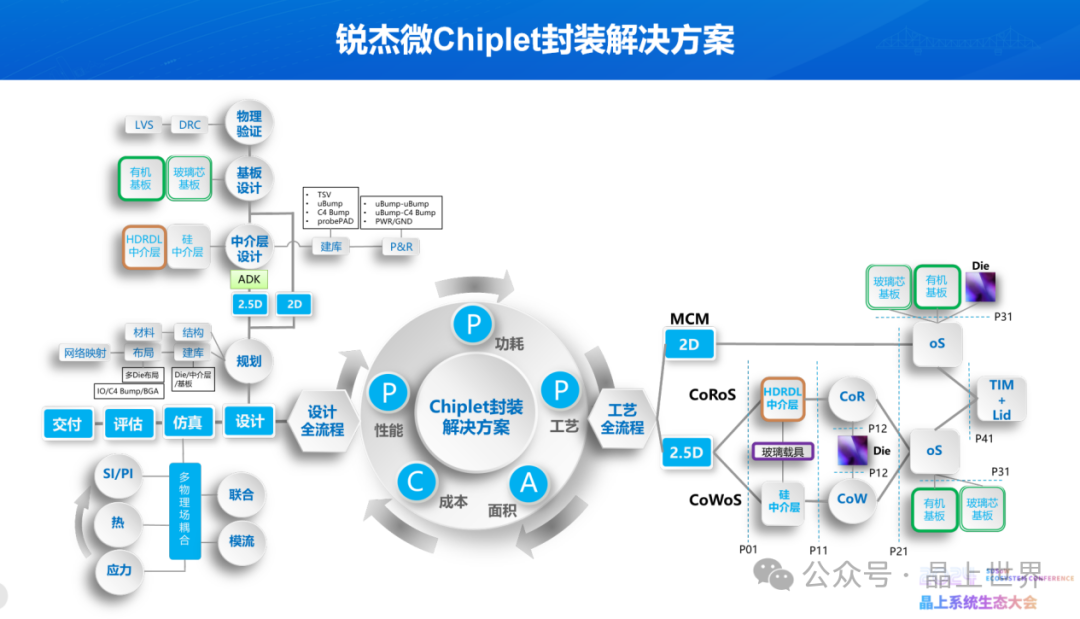

锐杰微 Chiplet封装技术的创新先锋

锐杰微科技专注于高端芯片设计和工艺全流程的封测制造,特别是在Chiplet封装技术领域默默耕耘,积累了宝贵经验,掌握着包括2.5D硅中介层、硅桥及RDL中介层等在内的多项核心技术。而且作为中国第三代封装技术Chiplet标准的参与方,锐杰微在推动行业标准制定方面也发挥了积极作用。

现阶段,锐杰微主要瞄准台积电CoWoS-S封装技术的替代工艺展开开发,针对晶圆级系统的3D封装方案也在布局当中。

围绕基于国内的先进工艺制程推出全国产化先进封装方案这一核心发展理念,锐杰微已构建了一套涵盖Chiplet产品设计仿真与工艺生产全流程的封测解决方案。

截至目前,锐杰微已完成采用不同封装方案的多个Chiplet产品开发和项目交付。下面进行部分展示:

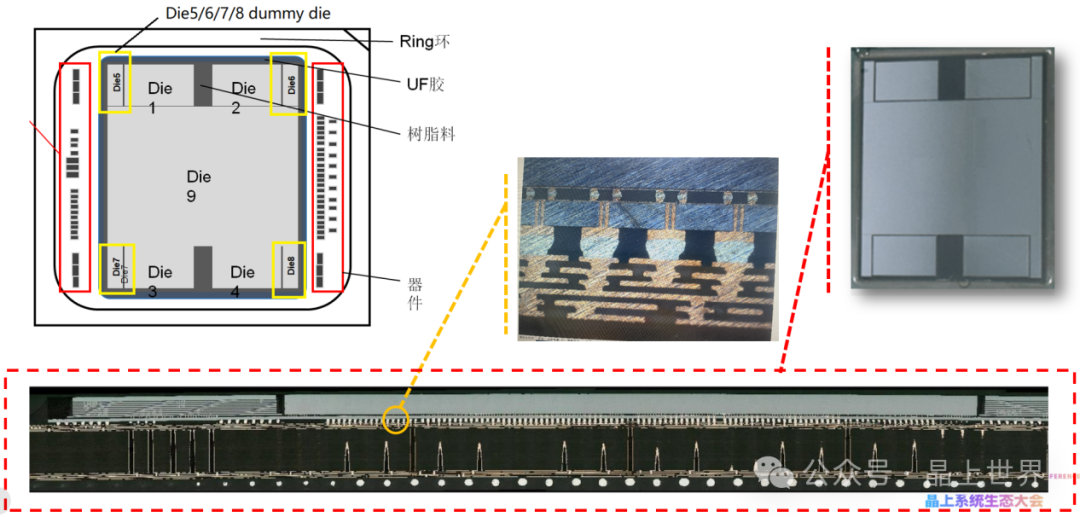

2.5D CoW组装工艺验证

产品集成了4个HBM芯片,4个HBM dummy芯片,并利用4个结构dummy堆叠仿真设计有效的控制了2.5D模组翘曲。CoW组装C2 pillar直径/节距为20um/40um,C4 bump为80um SAC焊球;并采用65nm双大马士革工艺节点的TSV中介层和18层ABF基板封装。该项目验证了CoW组装工艺技术路线可行性。

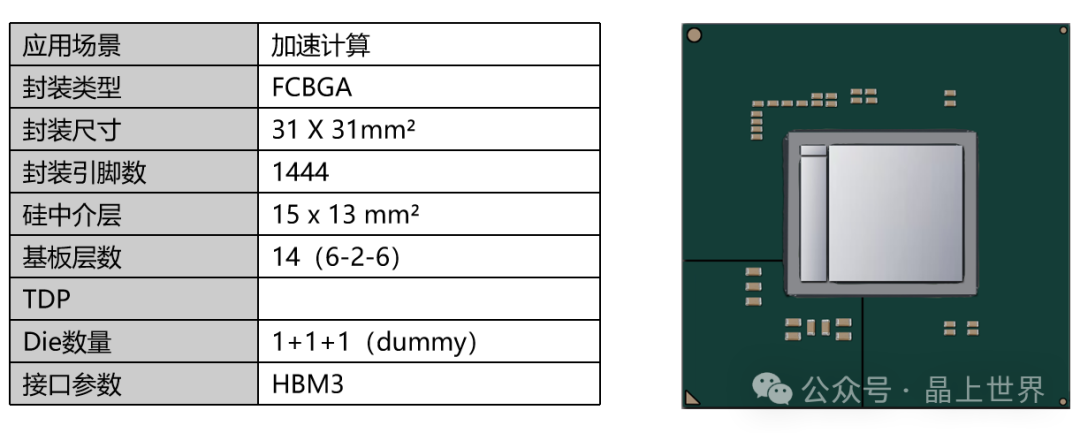

国产HBM方案

方案采用1+1结构,Logic Die+第四代HBM模组,通过硅中介层实现高速互联。Logic Die采用了国内先进的工艺制程,Micro Bump直径25um,Pitch为40um的工艺参数;硅中介层采用了目前国内领先带DTC结构的TSV工艺,有效降低PDN高频段噪声,改善AC IR-DROP指标,大幅提升大功率场景的电源网络的完整性。

该项目从硅载板电路设计、基板电路设计到模型参数抽取、SI/PI完整性仿真、热仿真分析、结构应力多物理场耦合仿真以及组装工艺,锐杰微全程参与并提供了重要技术支撑。验证了国产2.5D+HBM的设计、Wafer工艺路线及封装加工工艺路线。

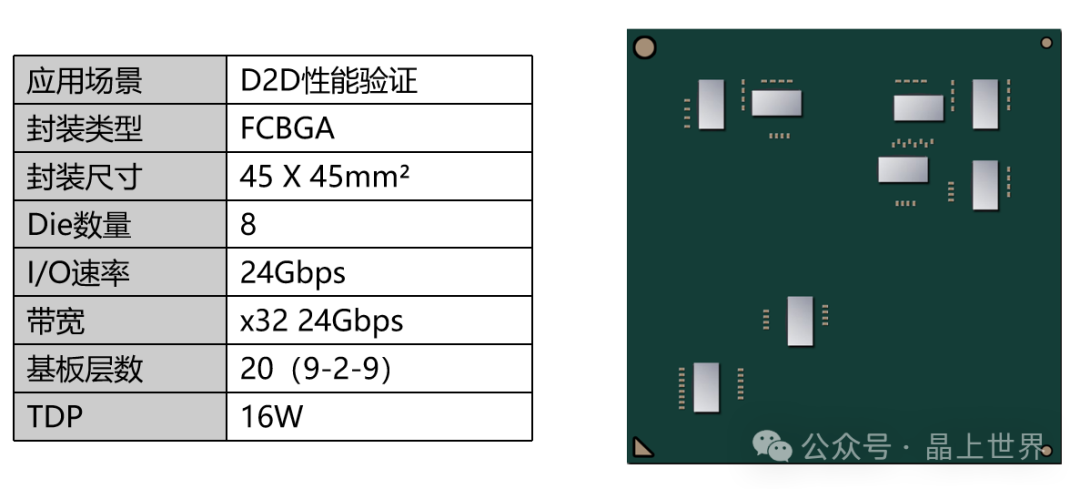

2D MCM —

UCIe1.0标准 x32 24Gbps D2D

按照UCIe1.0标准给出的参考建议,要达到x32 24Gbps的I/O速率和带宽,需要采用2.5D工艺才能满足性能要求。考虑到成本因素,经锐杰微和合作伙伴论证,通过设计+仿真反复迭代,在无中介层、搭载ABF基板条件下,达到了D2D最长距离25mm和x32 24Gbps的性能指标要求,探索出了一条高性能、低成本的Chiplet解决之路。该产品也是目前国内性价比最好的产品。

作为Chiplet封装技术的探索者,锐杰微正以扎实的技术基础和行业参与,稳步推动技术革新。期待未来锐杰微继续深耕国产化封装解决方案,打造国内高端核心芯片国产化封测服务最优平台。

-

封装

+关注

关注

127文章

8184浏览量

143961 -

chiplet

+关注

关注

6文章

439浏览量

12702

原文标题:解锁Chiplet潜力:封装技术是关键

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

支持Chiplet的底层封装技术

半导体芯片先进封装——CHIPLET

什么是Chiplet技术?chiplet芯片封装为啥突然热起来

北极雄芯开发的首款基于Chiplet异构集成的智能处理芯片“启明930”

SiP与Chiplet成先进封装技术发展热点

支持Chiplet的底层封装技术

先进封装Chiplet全球格局分析

Chiplet技术给EDA带来了哪些挑战?

先进封装Chiplet的优缺点与应用场景

先进封装技术是Chiplet的关键?

探讨Chiplet封装的优势和挑战

先进封装 Chiplet 技术与 AI 芯片发展

什么是Chiplet技术?

解锁Chiplet潜力:封装技术是关键

解锁Chiplet潜力:封装技术是关键

评论