GPIO口的定义:

GPIO口,通用输入输出,这个大家都知道,但是输入,输出的电路是什么样的,其实并不用太关心,只需配置寄存器即可,但是还是要摸一摸,为了方便理解,引入了单片机的IO口原理图来说明(道理是一样的)

认识电路:

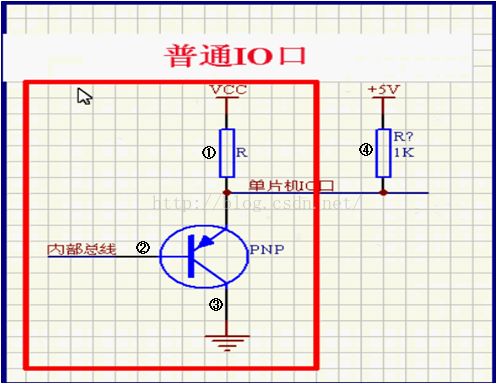

一.普通IO口

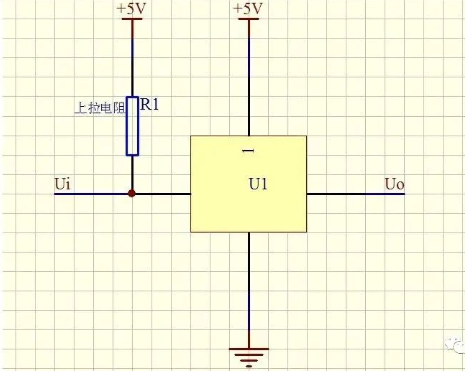

如上图所示(红色框是板子内部)

1.基级(②位置)为低电平时,PNP导通,此时单片机IO口输出的是低电平,当基级(②位置)为高电平时,PNP导通,此时单片机IO口输出的是高电平

2.这里注意,④位置上是一个上拉电阻,这里设置上拉电阻的考虑因素是这样的,假设我要在这个单片机IO口输出一个电流来驱动小灯发亮,①的位置电阻一般有20k左右,发出的电流250uA,基本上忽略不计,加上一个上拉电阻后, 总电流 = ①位置电流 + ④位置电流(①与④构成并联电路)

3.为什么不设置让,①的位置电阻R小一点,这样电流大一点,就不需要上拉电阻了呢? 因为单片机是控制单元,设计时最好把强电流设计到外围电路里,如果设计到单片机内部,会烧坏板子

这里体现出上拉电阻的其中一个作用--->加大电流,加强了驱动的能力

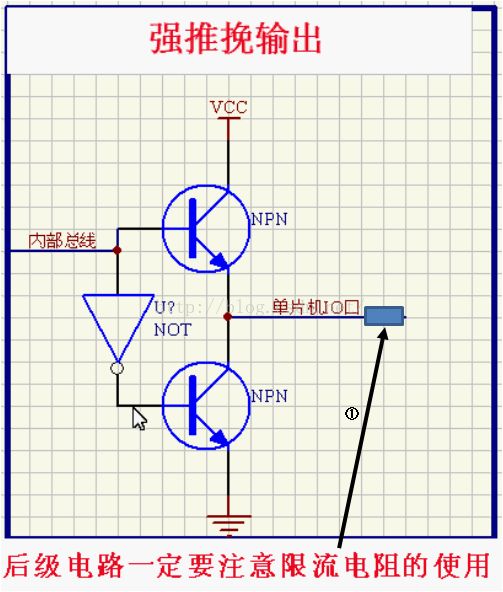

二.强推挽输出:

(意思就是说能输入输出大电流,前面已经说了单片机内部最好不要设计大的电流,所以这个功能的IO要少用)

1.内部总线输入高电平, 上面的NPN导通,则IO口输出大电流(因为上面的三极管VCC电源下面没有接上拉电阻, I = VCC/电阻+NPN内部电阻),所以IO出口的地方一般接一个电阻限流内部总线输如低电平, 下面的NPN导通,则此时如果IO口外面接一个VCC(不带上拉电阻),就会有大电流灌输进来

这里体现了上拉电阻的另一个作用--->限流

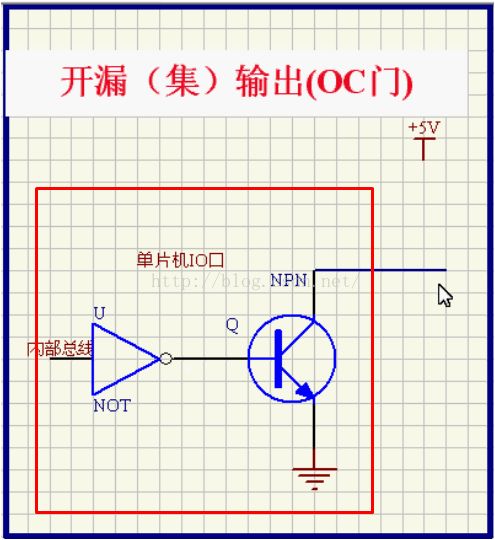

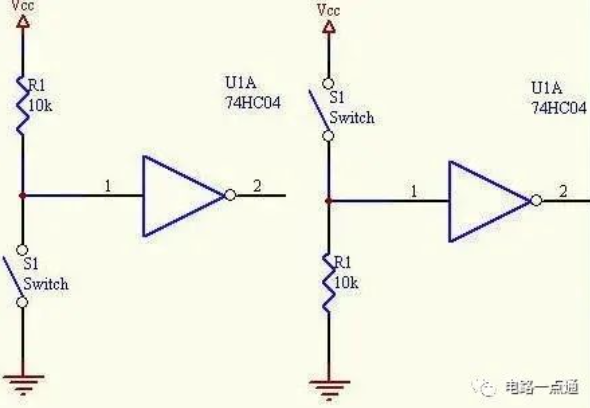

三.开漏级OC门:

什么叫IO口的开漏状态,如上图所示 如果内线是高电平,则NPN的基级是低电平,此时NPN不导通,那么IO口此时相当于是悬浮在空气中的,所以无法确定它的状态(不知道是低电平还是高电平),那么这个状态就是开漏状态,所以此时要向外围电路输出一个高电平是不可能的,如果想输出一个高电平,则必须在NPN的集电极上面来一个上拉电阻

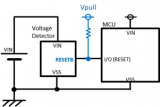

这时又体现出上拉的一个作用: 就是将不确定的信号通过一个电阻嵌位(保持)在一个高电平上,下拉同理,

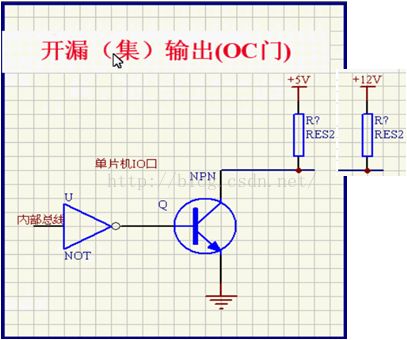

这里对于OC门还有一个应用, 可以控制高电位的电路,如果外围电路需要大的电压,则可以用OC门加上拉电阻来完成这个功能,如下图所示, 当内部总线为高电平,则NPN截止,最右边加一个12v的上拉电阻,使得电位钳在12v供外围电路使用。

-

上拉电阻

+关注

关注

5文章

359浏览量

30611 -

GPIO

+关注

关注

16文章

1204浏览量

52059

原文标题:GPIO电路图以及上拉电阻的作用

文章出处:【微信号:eet-china,微信公众号:电子工程专辑】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

TLV320AIC3100原理图,音频输入电路MIC的上拉电阻R1303和下拉电阻R1304是否需要?

GPIO电路图以及上拉电阻的作用

GPIO电路图以及上拉电阻的作用

评论