在脉冲雷达应用中,从发射到接收操作的过渡期间需要快速开启/关闭高功率放大器 (HPA)。典型的转换时间目标可能小于1 s。传统上,这是通过漏极控制来实现的。漏极控制需要在28 V至50 V的电压下切换大电流。已知开关功率技术可以胜任这一任务,但会涉及额外的物理尺寸和电路问题。在现代相控阵天线开发中,虽然要求尽可能低的SWaP(尺寸重量和功耗),但希望消除与HPA漏极开关相关的复杂问题。

本文提出了一种独特但简单的栅极脉冲驱动电路,为快速开关HPA提供了另一种方法,同时消除了与漏极开关有关的电路。实测切换时间小于200 ns,相对于1 s的目标还有一些裕量。其他特性包括:解决器件间差异的偏置编程能力,保护HPA免受栅极电压增加影响的栅极箝位,以及用于优化脉冲上升时间的过冲补偿。

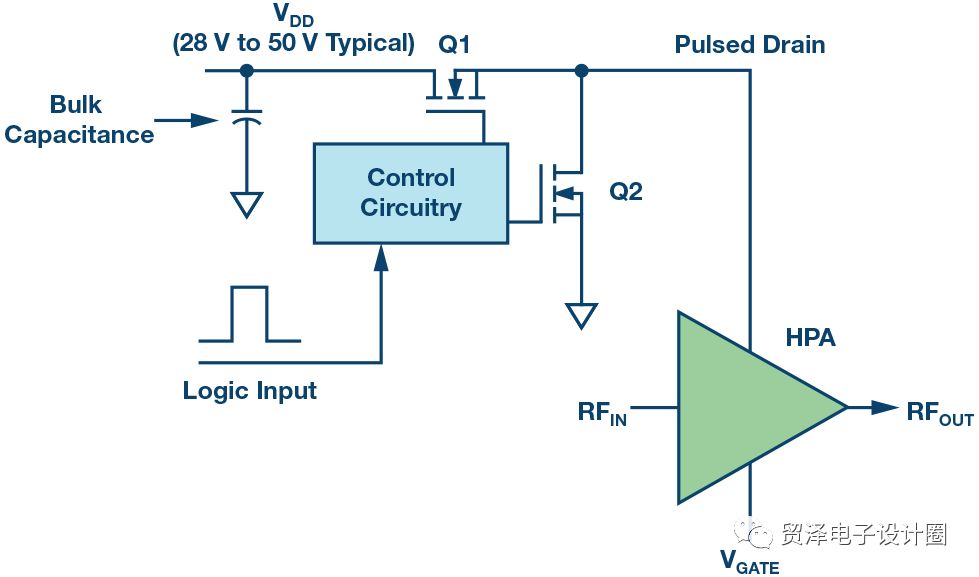

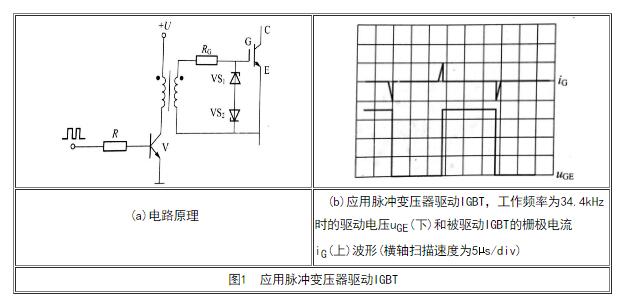

典型漏极脉冲配置通过漏极控制开关HPA的典型配置如图1所示。一个串联FET开启输入HPA的高电压。控制电路需要将逻辑电平脉冲转换为更高电压以使串联FET导通。

此配置的难点包括:

●大电流的切换要求从大容量电容到HPA漏极引脚的路径是一条低电感路径。

●关闭时,漏极电容保有电荷,需要额外的放电路径。这是通过额外的FET Q2来实现的,对控制电路的约束随之增加:Q1和Q2绝不能同时使能。

●很多情况下,串联FET是N沟道器件。这要求控制电路产生一个高于HPA漏极电压的电压才能开启。

控制电路的设计方法已是众所周知且行之有效。然而,相控阵系统不断期望集成封装并降低SWaP,因此希望消除上述难点。实际上,人们的愿望是完全消除漏极控制电路。

图1. 传统HPA脉冲漏极配置。

推荐栅极脉冲电路栅极驱动电路的目标是将逻辑电平信号转换成合适的GaN HPA栅极控制信号。需要一个负电压来设置适当的偏置电流,以及一个更大的负电压来关闭器件。因此,电路应接受正逻辑电平输入并转换为两个负电压之间的脉冲。电路还需要克服栅极电容影响,提供急速上升时间,过冲应极小或没有。

对栅极偏置设置的担忧是,偏置电压的小幅增加可能导致HPA电流的显著增加。这就增加了一个目标,即栅极控制电路应非常稳定,并有一个箝位器来防止受损。另一个问题是,设置所需漏极电流时,不同器件的最佳偏置电压有差异。这种差异使得人们更希望有系统内可编程栅极偏置特性。

图2. 推荐HPA栅极驱动电路。

图2所示电路达成了所述的全部目标。运算放大器U1使用反相单负电源配置。利用一个精密DAC设置运算放大器基准电压,以实现V+引脚上的增益。当逻辑输入为高电平时,运算放大器箝位到负供电轨。当输入为低电平时,运算放大器输出接近一个小的负值,该值由电阻值和DAC设置决定。反相配置是故意选择的,目的是当逻辑输入为低电平或接地时开启HPA,因为逻辑低电平的电压差异小于逻辑高电平。采用轨到轨运算放大器,它具有较大压摆率和足够的输出电流驱动能力,适合该应用。

元件值选择如下:

●R1和R2设置运放增益。

●DAC设置连同R3和R4决定运算放大器V+引脚的基准电压。C1和R3针对低通滤波器噪声而选择。

●R5和R6用于实现重要的箝位功能。这是因为运放的VCC引脚以地为基准,所以这是运放输出的最大值。R5和R6为–5 V电源提供一个电阻分压器。

●R5的不利影响是由于栅极电容,它会减慢脉冲响应。这要通过增加C3来补偿,以实现陡峭的脉冲。

●C2的值较小,用以限制运放输出脉冲上升沿的过冲。

实测数据用于验证电路的测试设置如图3所示。对精密DAC、运算放大器和HPA使用评估板。一个脉冲发生器用于模拟1.8 V逻辑信号。信号发生器连续工作,利用一个输入带宽高于RF频率的RF采样示波器测量HPA对RF信号的开启/关闭。

图3. 测试设置。

测试所用的元器件值参见表1。

表1. 所用元器件值

实测开启时间如图4所示。时间标度为每格500 ns,RF信号的上升时间小于200 ns。对于测量从栅极脉冲开始到RF脉冲上升沿结束的时间的系统,可以看到开启时间约为300 ns,这说明系统分配1s用于发射到接收转换会有相当可观的裕量。

图4. 实测HPA开启时间。

图5. 实测HPA关闭时间。

实测关闭时间如图5所示。时间标度同样是每格500 ns,下降时间明显快于上升时间,同样远小于200 ns,说明系统分配1 s用于发射到接收转换会有相当可观的裕量。

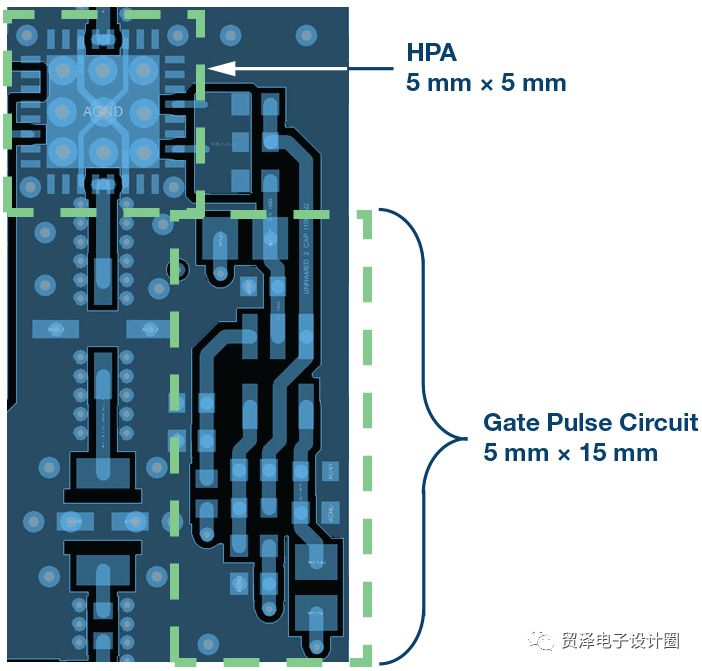

布局考虑对一个代表性布局做了尺寸研究,如图6所示。栅极脉冲电路的运算放大器部分放置在通向HPA输入的RF路径附近。精密DAC未显示出来,假定其放置在控制部分中,为多个发射通道提供输入。布局研究表明,可将该电路添加到实际的低成本PWB实现方案中,发射RF电路所需的额外空间极小。

图6. 物理尺寸分配。

结语本文提出了一种独特的栅极脉冲电路,并进行了HPA快速开/关评估。

其特性包括:

-

转换时间小于200 ns。

-

兼容任何逻辑输入。

-

通过可编程偏置消除器件间差异。

-

提供箝位保护以设置最大栅极电压。

-

上升时间/过冲补偿。

-

尺寸支持高密度相控阵应用。

先进电子系统集成度不断提高,要求缩小物理尺寸,因此可以想象,这种电路及其方法的其他变化,将开始在需要快速HPA转换时间的相控阵应用中激增。

作者

Peter Delos

Peter Delos 是ADI公司航空航天和防务部的技术主管。他于1990年获得美国弗吉尼亚理工大学电气工程学士学位(BSEE),并于2004年获得美国新泽西理工学院电气工程硕士学位(MSEE)。1990年至1997年,他为美国海军核电站计划工作。工作内容包括:完成海军核电站学校官员计划,担任海军潜艇基地教师,领导康涅狄格州格罗顿的海狼级潜艇的现场电气工程师。

1997年,他接受了洛克希德马丁公司在新泽西州穆尔斯顿的一个职位,开始了一段硕果累累的职业历程,为多个雷达和电子战计划开发接收机/激励器和频率合成器。这段经验包括架构定义、详细设计、快速原型开发、制造、现场安装和协调多个工程专业。他的工作引领了相控阵接收器/激励器从集中式架构到阵列上数字波束合成系统的转变。

Jarrett Liner

Jarrett Liner是ADI公司航空航天与防务部门(位于美国北卡罗来纳州格林斯博罗)的RF系统应用工程师,他在射频系统和器件设计方面有着丰富的经验。

此前,他是防务和航空航天领域碳化硅衬底氮化镓放大器应用工程师。其先前的经历还包括从事13年的RF IC WLAN功率放大器和前端模块的设计与测试工作。他曾作为电子技师在美国海军服役6年。Jarrett于2004年获得美国北卡罗来纳州农业技术州立大学(位于北卡罗来纳州格林斯博罗)电气工程学士学位。

当Jarrett不在实验室仿真电路或测量数据时,他可能在山地上骑自行车、在健身房教授自行车课程、跑步或者在庭院与他的四个孩子追逐嬉戏。

-

ADI

+关注

关注

146文章

45819浏览量

249673 -

栅极驱动

+关注

关注

8文章

184浏览量

23126

原文标题:能否在200 ns内开启或关闭RF源?看完这篇你就知道了。。。

文章出处:【微信号:Mouser-Community,微信公众号:贸泽电子设计圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

独特的栅极驱动应用能否在200 ns内开启或关闭RF源?

DVRFD630-275,开发板是一种通用电路板,旨在简化IXRFD630栅极驱动器的评估

一种新型实用的IGBT驱动电路

一种快沿脉冲信号发生器的设计

一种独特但简单的栅极脉冲驱动电路

一种独特但简单的栅极脉冲驱动电路

评论