由于篇幅有限,本文仅选取部分内容进行分享。

Vitis 简介

AMD Vitis 工具套件包含多种设计技术,用于开发以 AMD 器件(例如,AMD Versal 自适应 SoC 器件、AMD Zynq MPSoC 和 AMD Alveo 数据中心加速器卡)为目标的异构嵌入式应用。

Vitis 工具包括:

C++ 编译器、库和本征函数,适用于 AI 引擎和可编程逻辑( PL )

适用于 Arm 和 MicroBlaze CPU 的传统工具链和库

图形化集成设计环境( IDE )

系统连接器,用于配置复杂的器件子系统,如 AI 引擎、NoC 和 Control & Integrated Processing system( CIPS ),并将其与高性能多速率系统中的 PL 模块与内核相集成

调试器和硬件/软件检测自动化,有助于定位和解决嵌入式系统中的性能瓶颈和问题

跨 PL( HDL )、AI 引擎( System-C ) 和 CPU( QEMU )无缝编译、链接和运行异构仿真

程序分析器,用于剖析和可视化仿真中和目标上的硬件/软件性能

Xilinx Runtime( XRT )提供 Linux 用户空间 API,用于运行时镜像加载、存储器管理与内核控制

开发平台,提供开箱即用的沙箱,用于 AI 引擎 开发、PL+AI 引擎子系统开发以及嵌入式系统应用引导

硬件优化的库,用于 DSP、视觉和图像处理、线性代数和诸多其他应用域

Vitis 工具套件是基于 AMD Vivado Design Suite 构建的,支持硬件和软件的 C/C++ 编程、灵活且可缩放的系统连接规格用于促进自上而下、中间向外和自下而上的设计迭代、RTL 模块集成、清晰的底层 Vivado 硬件工具流程自动化和交接。

Vitis 关键概念

本主题介绍的关键概念有助于您了解和使用 AMD Vitis 工具来开展嵌入式系统设计。这些工具支持通过以下方式完成各种开发流程:使用脚本编制执行开发或者通过 Vitis IDE 进行交互式设计输入来执行开发。所有开发流程均以相同结果为目标,但设计师的技能等级和工程要求可能会影响特定流程类型的倾向性。下表描述了这些步骤。

表 1:概念性设计步骤

| 步骤 | 注释 |

| 选择器件 | 声明为部件或开发板 |

|

设置基本的硬件 基础架构 |

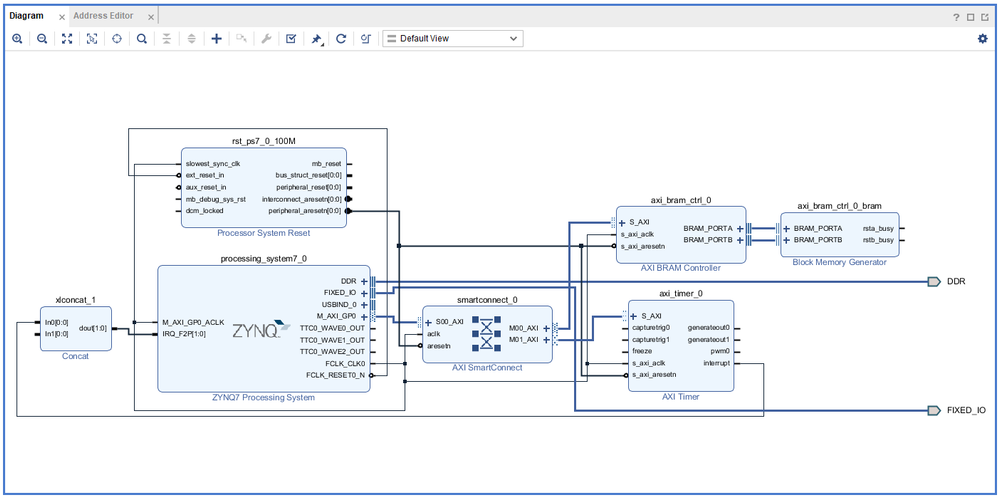

这即所谓通过 AMD Vivado 创建的硬件平台。有效的硬件平台由 Vivado IP integrator 组件(例如,CIPS、NoC )和至少一个时钟(含关联复位)组成。(可选)除了时钟域、复位和定制 RTL IP 外,还可添加 AI 引擎、NoC DDRMC、AXI SmartConnect 和 AXI Interrupt Controller。在块设计内的单元和端口上将包含 PFM 属性,这些单元和端口用于为内核控制定义潜在的连接点、访问 DDR 和其他存储器、串流输入/输出、时钟、复位及中断。此初始设计会作为可扩展硬件平台导出到 Vitis。 |

| 添加处理元件 |

这即所谓的 Vitis 组件,包括 PL 内核与 AI 引擎计算图。 注释:这些组件先独立完成开发和验证,然后再添加。组件开发不在本文档的探讨范围内。 |

| 实现硬件 | 在 Vitis 术语中,这是指编译和链接硬件系统的进程。Vitis 实现步骤会利用 Vivado 来进行 PL 综合与布局布线。 |

| 添加软件应用 | 在处理器(如,APU、RPU 和 MicroBlaze )上运行的控制应用和/或处理应用。 |

| 封装软件和硬件 | 将可加载的对象与可执行应用组合为二进制可交付物(如,SD 卡、QSPI 闪存等)的进程。 |

|

在目标上部署 并运行 |

此步骤包括加载二进制可交付物并在硬件上运行或者在硬件仿真中运行。Vitis 实现步骤会利用 Vivado 来进行 PL 综合与布局布线。 |

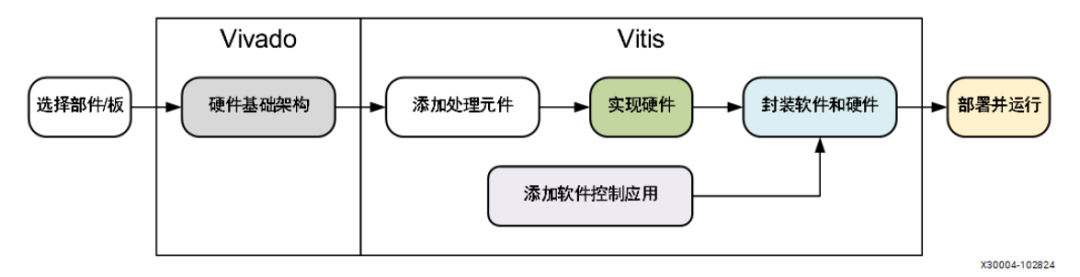

下图演示了设计嵌入式系统并将其与 AMD 工具集成的概念性流程。

图 1:Vitis 概念性设计流程

Vitis 工具支持多种不同的设计流程,如第 3 章:Vitis 流程和构建环境所述。以下章节着重讲解了用于创建和集成这些不同组件的各种工具和技巧。

-

amd

+关注

关注

25文章

5475浏览量

134282 -

嵌入式设计

+关注

关注

0文章

392浏览量

21301 -

Vitis

+关注

关注

0文章

147浏览量

7456

原文标题:使用 Vitis 进行嵌入式设计开发用户指南(附下载)

文章出处:【微信号:赛灵思,微信公众号:Xilinx赛灵思官微】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Vitis里如何创建嵌入式软件工程

Vitis2023.2使用之—— classic Vitis IDE

Compact系列CPLD嵌入式Flash(EFlash)用户指南

使用AMD Vitis进行嵌入式设计开发用户指南

使用AMD Vitis进行嵌入式设计开发用户指南

评论