STMicroelectronics成像部门负责向消费者、工业、安全和汽车市场提供创新的成像技术和产品。该团队精心制定了一套通过模板实现的High-Level Synthesis(HLS)高层次综合流程,使得上述产品能够迅速上市。对于汽车市场,该流程符合ISO 26262标准,因此能确保可靠性。

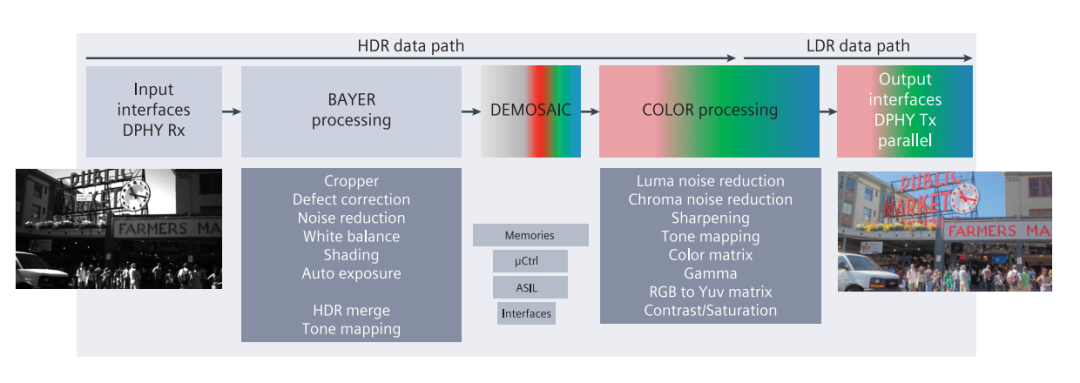

ISP是处理图像传感器数据的硬件和软件组合。ISP可能非常复杂,因此该团队使用了可复用的IP模块来组装设计。图1显示了一个示例ISP方框图。

图1中的ISP显示了主要ISP功能,并沿着数据通路说明了各自所需的诸多处理算法。

图1.用于汽车应用的复杂高质量ISP

了解HLS工具历史

成像部门于2007年开始对多媒体IP(编码器、解码器、显示器和ISP功能)运用HLS设计流程,最初使用的是西门子数字化工业软件竞争对手提供的工具。当该工具在2015年停止服务后,该团队对不同供应商提供的各种HLS工具进行了评估。他们将若干ISP设计用作测试案例,然后监测其所生成的RTL的面积和功耗结果。在此评估基础上,Catapult High-Level Synthesis平台因为表现优异而被该团队选中。

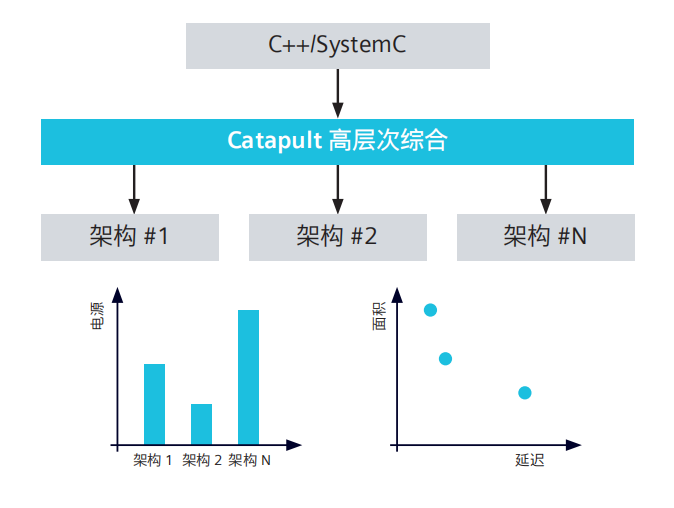

借助Catapult HLS平台,设计人员便能利用行业标准ANSI C++和SystemC来描述功能意图,并将其提高到生产率更高的抽象层次。根据这些高层次的描述,Catapult即可生成产品级的RTL。通过加快RTL生成时间以及自动生成无错误的RTL,Catapult可显著缩短RTL验证所需的时间。Catapult的功耗优化功能可自动大幅降低动态功耗。高度交互的工作流程可提供对综合过程的完全可见性和控制,使设计人员能够在功耗、性能和面积等方面迅速收敛到理想实现方案(图2)。

图2.快速探索架构以求得理想功耗和面积

创建成像IP模板

该团队意识到,ISP是一系列的级联滤波器,这些滤波器具有相似的结构和接口。他们的想法是利用C++模板开发一个参数化滤波器库,然后将其复用于每个ISP设计中。这种方法具有如下优势:

◎ 设计效率:复用经过验证的模板可以更快地构建ISP

◎ 更新:能够轻松将更新应用到每个IP模块,而且可以在一天内将算法更改整合完毕

◎ 集中精力:设计人员可以将时间花在增量算法开发上,而不必在通用结构上耗费心力

◎ 资源:团队可以为项目开发更多的IP模块,且无需增加额外的员工

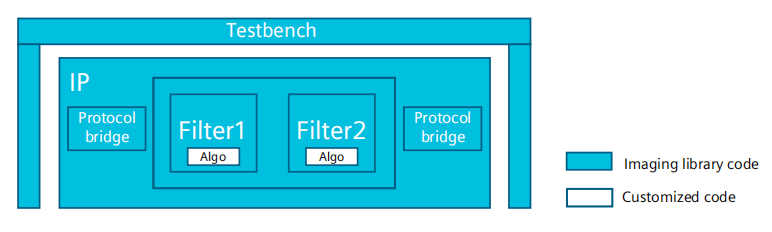

每个参数化模板都是一个C++类(图3),其可实现如下方面功能:

◎ 内存管理

◎ 协议桥

◎ 像素管理内核

◎ 连接到验证平台

图3.设计人员可专注于算法,而不是基础架构

设计人员可覆写filterFunction以提供算法代码,然后再通过覆写execute函数将其连接到滤波器。

利用这一模板流程,该团队在过去两年间创建了50多个设计,规模从1万个逻辑门到200万个逻辑门不等。

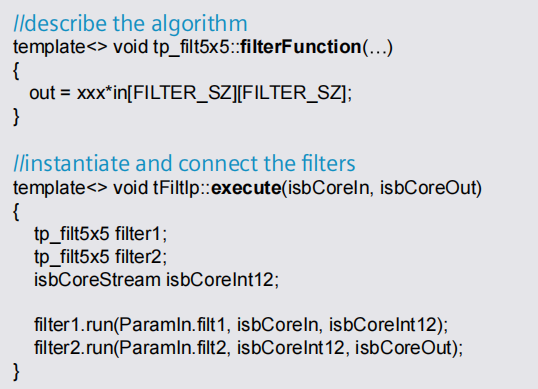

验 证 设 计

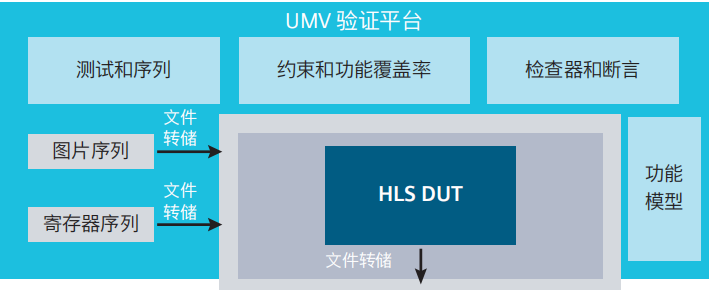

该团队使用UVM验证平台来指定提供伪随机验证及收集代码和功能覆盖率指标的序列。该团队使用了相同的验证平台(无需任何修改)来验证C++和生成的RTL设计。每个验证平台(图4)会为每个项目建立相同的标准集,这样一来,便可通过自动设置验证环境来缩短开发时间。此标准集包括:

◎ 标准化数据的输入和输出接口

◎ 标准化寄存器配置接口

◎ 标准化高层次控制(启用和重置设计)

◎ 标准化输入和输出数据格式

图4.常见UVM验证平台仿真C++(图中所示)

或RTL被测设计

UVM验证平台的常见元素包括操作被测设计(DUT)的测试和序列、约束和功能覆盖率语句,以及多种检查器和断言。图片和寄存器序列可操作DUT输入。该团队使用功能模型对DUT进行按位比较。

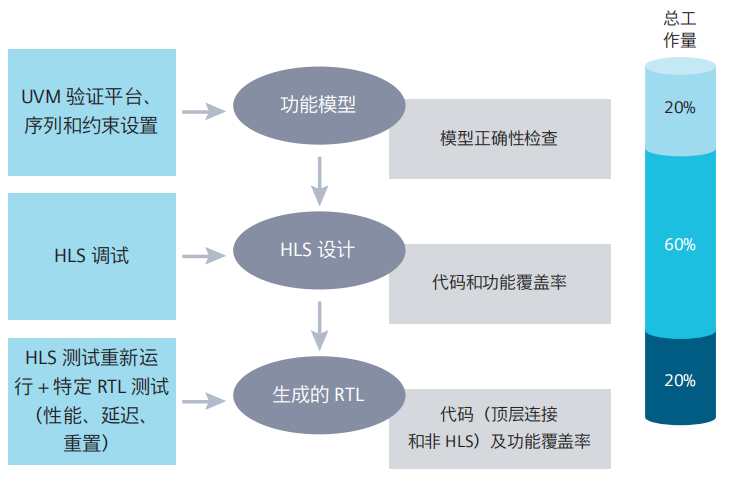

该团队对每个项目使用了相同的验证方法,因此可以确保获得尚佳质量的设计(图5)。

图5.验证流程

HLS验证流程的高层次步骤包括:

◎ 设计人员创建一个功能模型,验证人员利用必要 的序列和约束建立UVM验证平台。此阶段的仿真能够提供对整体环境的“正确性”检查,因此可能会发现问题。

◎ 在一个项目中,HLS调试步骤消耗的时间最多。此时,需要运行相关序列来调试问题以及收集代码和功能覆盖率指标。

◎ 藉由使用相同的UVM验证平台,团队可以对 Catapult HLS生成的RTL进行仿真。此时,团队 会针对C++设计中未建模的功能,例如输入和输出之间的延迟以及重置行为,添加一些特定RTL测试。在此步骤中,团队还会仿真HLS流程中未生成的任何RTL(如有)。此时,团队会从设计的顶层收集代码和功能覆盖率指标。

符合ISO 26262标准

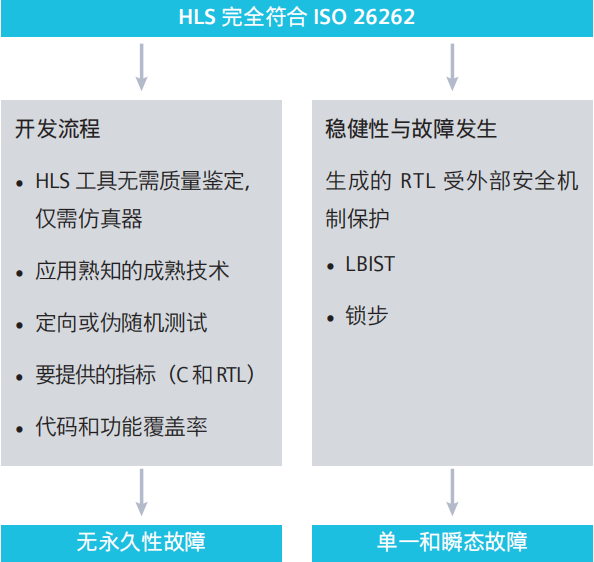

许多ISP产品的目标市场均为汽车市场,这意味着团队必须遵循ISO 26262标准。ISO 26262是一项针对重量在3500公斤及以下的公路车辆中的电气和电子元器件功能安全的标准。团队需要确保HLS流程和设计稳健性符合标准(图6)。

图6.HLS流程符合ISO 26262

该标准的其中一个关键要求是要确保器件没有永久性故障(设计错误)。也就是说,团队必须确保开发流程是“安全的”。要满足这一标准,则必须应用成熟的技术,执行一系列测试,并收集衡量指标报告。团队没有对Catapult HLS平台进行 ISO 26262质量鉴定。相反,他们对运行测试的仿真器进行了鉴定。虽然团队不要求在其流程中对Catapult HLS平台进行质量鉴定,但实际上Siemens Safe计划会提供该工具的ISO 26262质量鉴定和相关文档。

另一个主要要求是要确保设计能够处理单个或瞬态故障,并能从中予以恢复。团队在ISP外围使用逻辑BIST和Lockstep(锁步)等外部安全机制来确保其稳健性。

从HLS流程获益

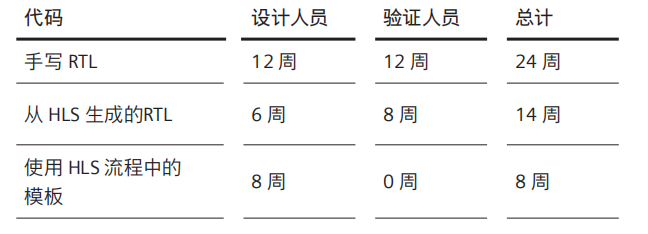

采用基于模板的HLS流程的主要优势在于,其可大幅减少开发时间和成本,而又不会影响结果和设计质量(表1)。使用该流程,团队创建设计的速度比手工编码快了3倍左右,单个设计人员便可执行验证,通常不需要单独的验证人员资源。

表1. 一名设计人员和一名验证人员

花在ISP设计项目上的平均时间

开发成本也将进一步降低,原因如下:

◎ 使用C++进行验证,以收集关键覆盖率指标,这意味着团队可以在几分钟内运行数以千计的测试,而不像RTL那样需要几个小时

◎ 与RTL相比,C++代码的行数显著减少,这意味着维护成本将会大幅降低

◎ 可以轻松适应设计流程后期的规范变化,而不会影响设计进度

◎ 短短几天时间便可完成对10名设计人员的HLS流程培训,这意味着团队可以快速提高生产率

此外,Catapult HLS平台具有自动化设计实现的功能,因此可以进一步降低HLS流程的开发时间和成本:

◎ 自动流水线:通过指令的简单改变提高流水线级 数,而C++代码将保持不变。如果是手动流水线,则需要大量的重新编码和调试工作

◎ 自动硬件共享:例如,要在一个流水线的不同状态下重复使用一个乘法器来处理同一迭代的几个操作,若通过手动实现将非常困难

◎ 自动功能时钟门控:相比手动编码可节省大量时间,并能自动降低功耗10%

◎ 该团队发现,使用该工具生成的RTL结果的质量非常出色,尤其是针对复杂设计时。

如需了解有关Catapult HLS解决方案的更多信息,请点击此处。

-

传感器

+关注

关注

2552文章

51222浏览量

754628 -

西门子

+关注

关注

94文章

3049浏览量

116050 -

图像信号

+关注

关注

0文章

26浏览量

14157 -

HLS

+关注

关注

1文章

130浏览量

24144

原文标题:客户故事|使用HLS流程设计和验证图像信号处理设备,加快产品上市

文章出处:【微信号:Mentor明导,微信公众号:西门子EDA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于FPGA的混合信号验证流程

新手求助,HLS实现opencv算法加速的IP在vivado的使用

【正点原子FPGA连载】第一章HLS简介-领航者ZYNQ之HLS 开发指南

【正点原子FPGA连载】第六章OV5640摄像头灰度显示实验-领航者ZYNQ之HLS 开发指南

【正点原子FPGA连载】第十三章基于xfOpenCV的中值滤波实验-领航者ZYNQ之HLS 开发指南

Vivado HLS实现OpenCV图像处理的设计流程与分析

嵌入式硬件开发学习教程——Xilinx Vivado HLS案例 (流程说明)

关于ZYNQ HLS图像处理加速总结的分享

HLS/HLV 流程说明及优势

基于Vitis HLS的加速图像处理

使用HLS流程设计和验证图像信号处理设备

使用HLS流程设计和验证图像信号处理设备

评论