RISC-V双系统平台结合了FPGA的灵活性和RISC-V指令集的开放性,为用户提供了一个高效、灵活的开发环境。

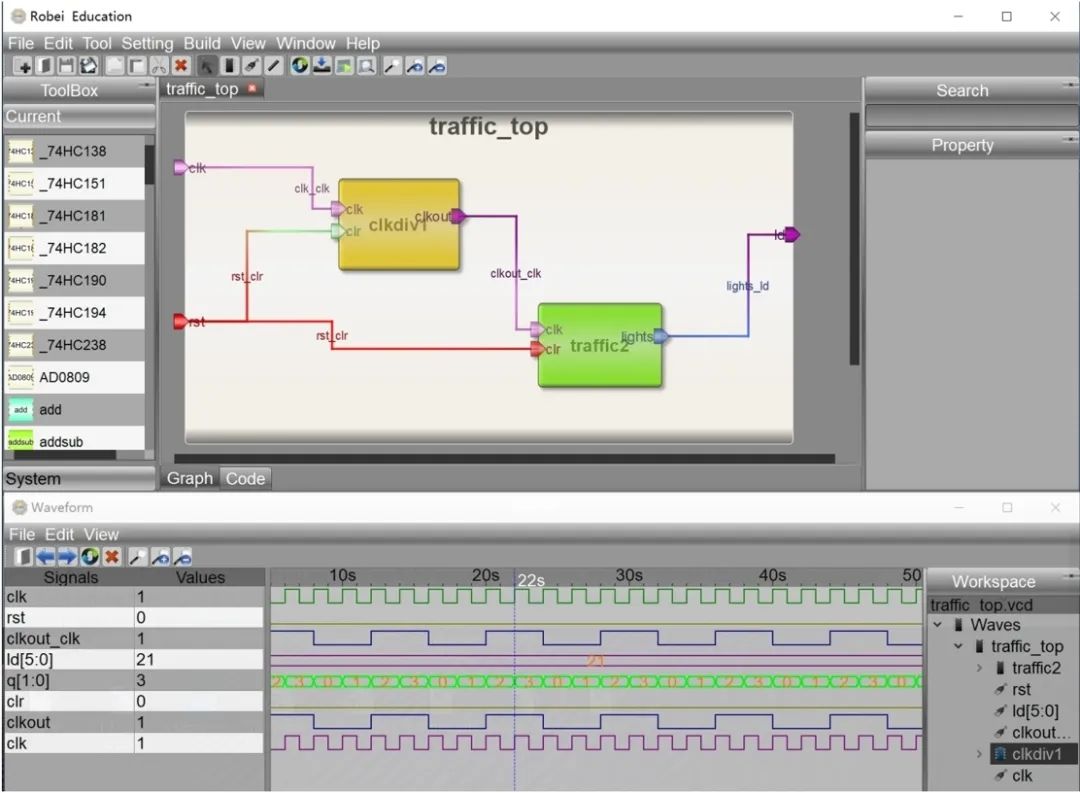

Robei EDA软件

Robei EDA工具:是一种全新的面向对象的可视化芯片设计软件,支持基于Verilog语言的集成电路前端设计与仿真。具备可视化架构设计、RTL编码(算法编程)、结构层自动代码生成、语法检查、编译仿真与波形查看等功能。

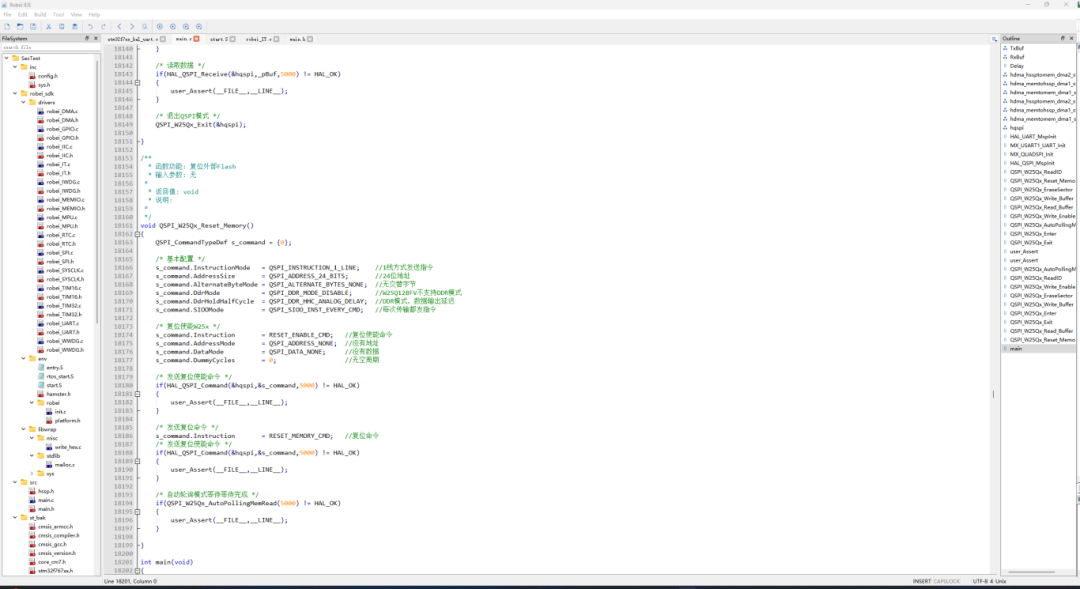

Robei IDE软件

Robei IDE 是由若贝公司开发的一款RISC-V集成开发工具,专门用于沉芯异构芯片的开发。Robei IDE 提供了完善的项目文件管理功能,方便用户对项目文件组织管理。该工具支持代码的编写和编译,使用户能够方便地进行程序开发;集成了下载和调试功能,用户通过它将编译好的程序下载到目标芯片,并进行调试。还包含了自适应IDE,专门用于自适应处理器的配置与重构,自适应IDE提供了Rocel配置、数据通路设定、数据对齐检查、单步执行仿真、一仿真、生成配置文件、配置文件融合等功能。

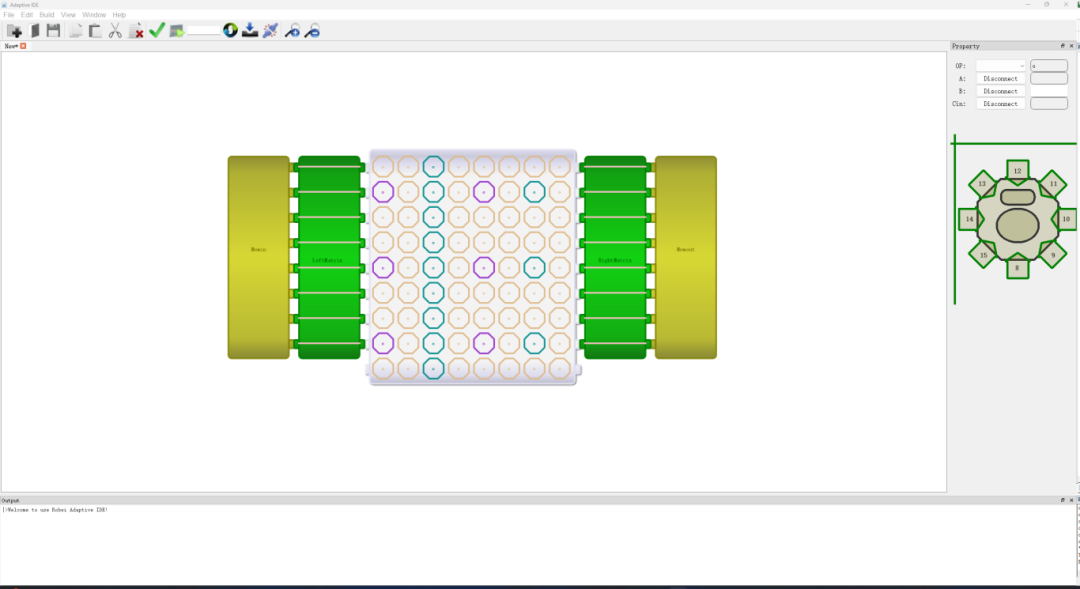

软件开发环境

自适应开发环境

Robei IDE的界面设计简洁直观,用户可以快速上手。自适应IDE的界面采用可视化设计,类似于下棋,用户只需熟悉基本规则即可轻松进行设计,可以用于系统设计与教育教学,帮助学生和教师更好地进行FPGA和ASIC的设计与开发。

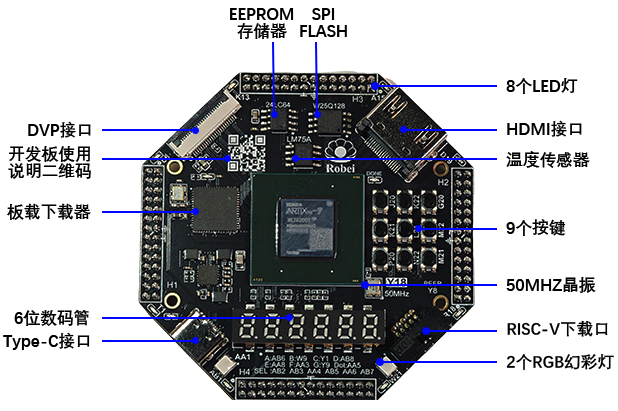

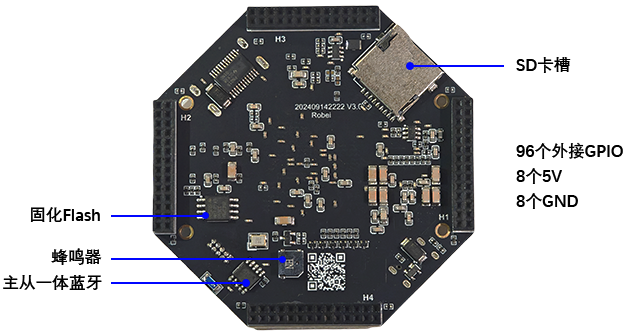

RX200T八角板

FPGA+RISC-V实验箱

FPGA+RISC-V实验箱集高性能、灵活、易上手于一体的综合性学习与实践平台。实验箱集成了高性能FPGA芯片与RISC-V软核处理器,实现硬件加速与软件灵活性的完美结合。用户可以通过FPGA,搭建RISC-V架构控制逻辑,进行复杂的数字信号处理、并行计算等任务。

芯片参数

|

CPU RISC-V指令集:RV32IMF CPU频率:3MHZ~250MHZ 快速中断响应处理 指令Flash:256KB 数据SRAM:256KB 16KB Cache ITCM支持 |

I/0管脚 64-176个可重构GPIO 4个SPI接口 2个Quad SPl 2个Hyperbus接口 12个UART接口 4个IIC/I3C接口 2个CAN总线接口 12个16bit Timer 4个32bit Timer独立看门狗 16个PWM接口 1个SDIO |

案例

| 拨码开关与LED应用实例 | 串口应用实例 |

| 蓝牙通信应用实例 | 蜂鸣器应用实例 |

| LM75A温度获取应用实例 | 数码管显示应用实例 |

| HC_SR04超声波测距应用实例 | 点阵显示应用实例 |

| RGB_LED幻彩灯应用实例 | 交通灯系统的实现 |

| EEPROM存储读写应用实例 | 触摸按键应用实例 |

| RTC日历获取应用实例 | WIFI获取天气应用实例 |

| 电机驱动应用实例 | AD/DA应用实例 |

| 步进电机实例 | DHT20温湿度实例 |

-

集成电路

+关注

关注

5391文章

11588浏览量

362514 -

芯片设计

+关注

关注

15文章

1024浏览量

54942 -

RISC-V

+关注

关注

45文章

2307浏览量

46297

原文标题:若贝集成电路设计和RISC-V双系统平台

文章出处:【微信号:Robei,微信公众号:Robei】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

2024 RISC-V 中国峰会:华秋电子助力RISC-V生态!

RISC-V Summit China 2024 | 青稞RISC-V+接口PHY,赋能RISC-V高效落地

沙龙活动:蓬勃发展的RISC-V生态

沙龙活动:蓬勃发展的RISC-V生态

RISC-V MCU开发相关资料分享

布局 RISC-V 领域,中国联通加入中国 RISC-V 产业联盟

赛昉科技成立RISC-V Multimedia SIG,推动openKylin on RISC-V生态发展

RISC-V核、平台和芯片该如何选择?

256核!赛昉发布全新RISC-V众核子系统IP平台

RISC-V学习笔记【1】RISC-V概述

RISC-V指令集的特点和优势分析

中移芯昇科技RISC-V芯片亮相ICDIA滴水湖论坛***展区

走进苏州中科集成电路设计中心

赛昉科技与上海交通大学国家集成电路人才培养基地达成课程合作,推动高校RISC-V人才培育

若贝集成电路设计和RISC-V双系统平台

若贝集成电路设计和RISC-V双系统平台

评论