在半导体制造的微观世界里,碳化硅衬底作为新一代芯片的关键基石,其厚度测量的精准性如同精密建筑的根基,不容有丝毫偏差。然而,测量探头的 “温漂” 问题却如同一股暗流,悄然冲击着这一精准测量的防线,给碳化硅衬底厚度测量带来诸多实际且棘手的影响。

一、“温漂” 现象的内在根源

测量探头的 “温漂”,本质上是由于温度因素致使探头自身物理特性发生改变,进而引发测量误差的现象。一方面,环境温度的波动是 “温漂” 的重要诱因。半导体制造车间宛如一个复杂的热生态系统,大量设备持续运行散发的热量、通风与空调系统的调控失衡,以及外界气候变化、人员进出引发的冷热气流交换,都使得车间温度处于动态变化之中。对于对温度极为敏感的测量探头而言,哪怕是零点几摄氏度的起伏,都可能触发其内部敏感元件的性能波动。

以电学原理工作的探头为例,温度升高时,电子元件的导电性、电容值等关键参数会发生微妙变化。根据电学测量与厚度转换的原理,这些细微改变将直接反映在测量信号上,造成厚度测量值的偏差。另一方面,探头自身在工作过程中的发热也是不可忽视的因素。当电流通过探头内部电路,焦耳热随之产生,尤其是在长时间连续测量碳化硅衬底厚度时,热量不断累积。若探头散热设计欠佳,热量无法及时散发,便会在探头内部形成局部高温区域,促使光学镜片的折射率、机械结构的尺寸等发生改变,如同蝴蝶效应一般,最终在厚度测量结果上掀起巨大波澜。

二、对测量精度的深度侵蚀

在碳化硅衬底厚度以纳米级精度要求的测量场景下,“温漂” 带来的精度损失堪称致命。由于碳化硅材料本身的特性,其衬底制备工艺复杂,厚度公差极小。例如在制造高功率碳化硅器件用衬底时,厚度公差往往控制在几十纳米范围内。而 “温漂” 引发的测量误差,轻易就能突破这一精密防线。

假设环境温度上升 1℃,对于常见的电容式测量探头,其电容极板间的介电常数、极板间距等细微参数改变,换算到衬底厚度测量值,误差可达数纳米至数十纳米。这意味着原本符合工艺标准、厚度精准的衬底,可能因 “温漂” 被误判为次品,反之,有厚度缺陷的衬底却可能蒙混过关,流入后续工序,极大地影响了芯片良品率,让前期高昂的研发与制备投入付诸东流。

三、稳定性与重复性的严峻挑战

除了精度受损,“温漂” 还给测量的稳定性和重复性设置了重重障碍。半导体制造通常涉及对同一片衬底不同位置或同一批次大量衬底的连续测量。然而,车间温度的自然起伏以及探头自身发热的不确定性,使得测量过程仿若置身波涛汹涌的海面,测量数据毫无规律地跳动。

工程师在上午测量一批碳化硅衬底时,或许能得到一组看似稳定的厚度数据,但随着下午车间温度升高,“温漂” 加剧,再次测量同批衬底,数据可能出现整体偏移,标准差急剧增大。如此不稳定的测量输出,让工艺人员难以准确判断衬底厚度的一致性,无法精准把控工艺参数,给芯片制造过程中的质量管控带来极大困扰,延误研发与生产周期,增加成本开销。

四、长期可靠性的潜在危机

从长期运行视角审视,“温漂” 犹如一颗定时炸弹,威胁着测量探头及整个测量系统的寿命与可靠性。频繁的温度变化致使探头材料反复热胀冷缩,加速内部机械结构的磨损,电子元件的老化速度远超正常水平。长此以往,探头不仅 “温漂” 问题愈发棘手,还极易出现硬件故障,频繁停机维修,大幅增加设备维护成本。

更为关键的是,基于不准确的 “温漂” 数据持续调整碳化硅衬底加工工艺,会像多米诺骨牌一样,在整个半导体制造流程中引发连锁反应。诸如蚀刻不均匀、薄膜沉积厚度失控等问题纷至沓来,最终侵蚀芯片的电学性能、稳定性等核心指标,让产品在市场竞争中丧失优势,阻碍半导体产业的蓬勃发展。

五、应对 “温漂” 的策略突围

为化解这一难题,半导体行业从多维度协同发力。在硬件层面,研发新型低膨胀系数、温度稳定性高的探头材料,如特种陶瓷、石英玻璃混合材质,从根源降低 “温漂” 敏感度;优化探头内部结构设计,采用热隔离、温控补偿腔室等,减少外界温度干扰。软件算法上,借助实时温度传感器监测环境温度,配合智能算法动态校准测量值,依据温度变化曲线提前预估 “温漂” 量并修正;建立温度 - 测量误差数据库,通过大数据分析实现精准补偿。此外,在车间管理方面,加强恒温恒湿环境控制系统建设,严格控制温度波动范围,为高精度碳化硅衬底厚度测量创造稳定条件。

综上所述,测量探头的 “温漂” 问题虽隐匿却对碳化硅衬底厚度测量有着广泛而深刻的实际影响,从短期测量精度到长期工艺可靠性,贯穿半导体制造全过程。唯有通过材料创新、算法优化、环境管控等多管齐下,才能有效驯服这只 “精度杀手”,确保碳化硅衬底厚度测量精准无误,为蓬勃发展的半导体产业筑牢根基。

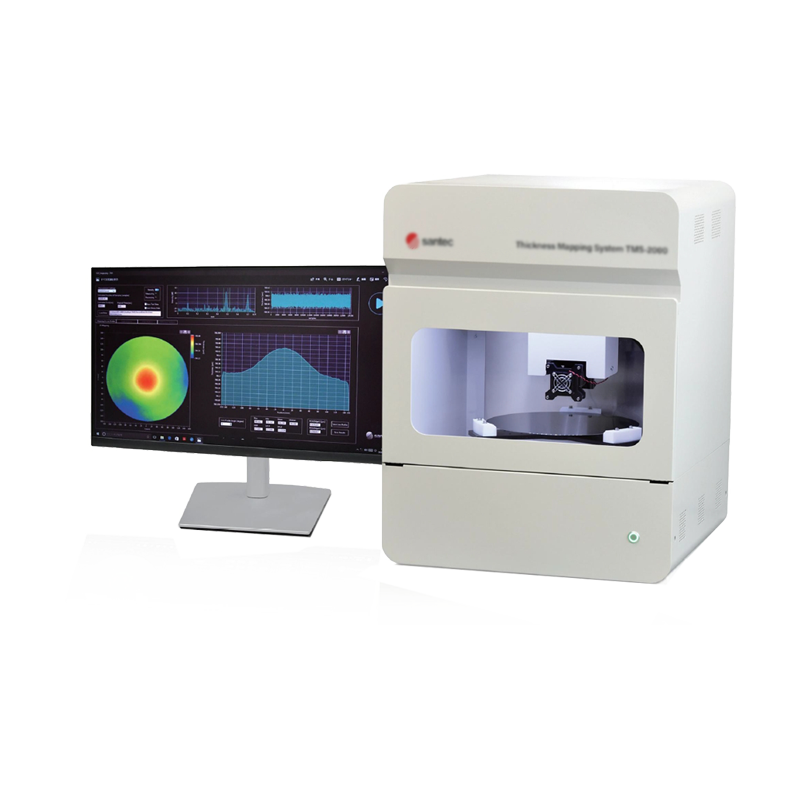

六、高通量晶圆测厚系统

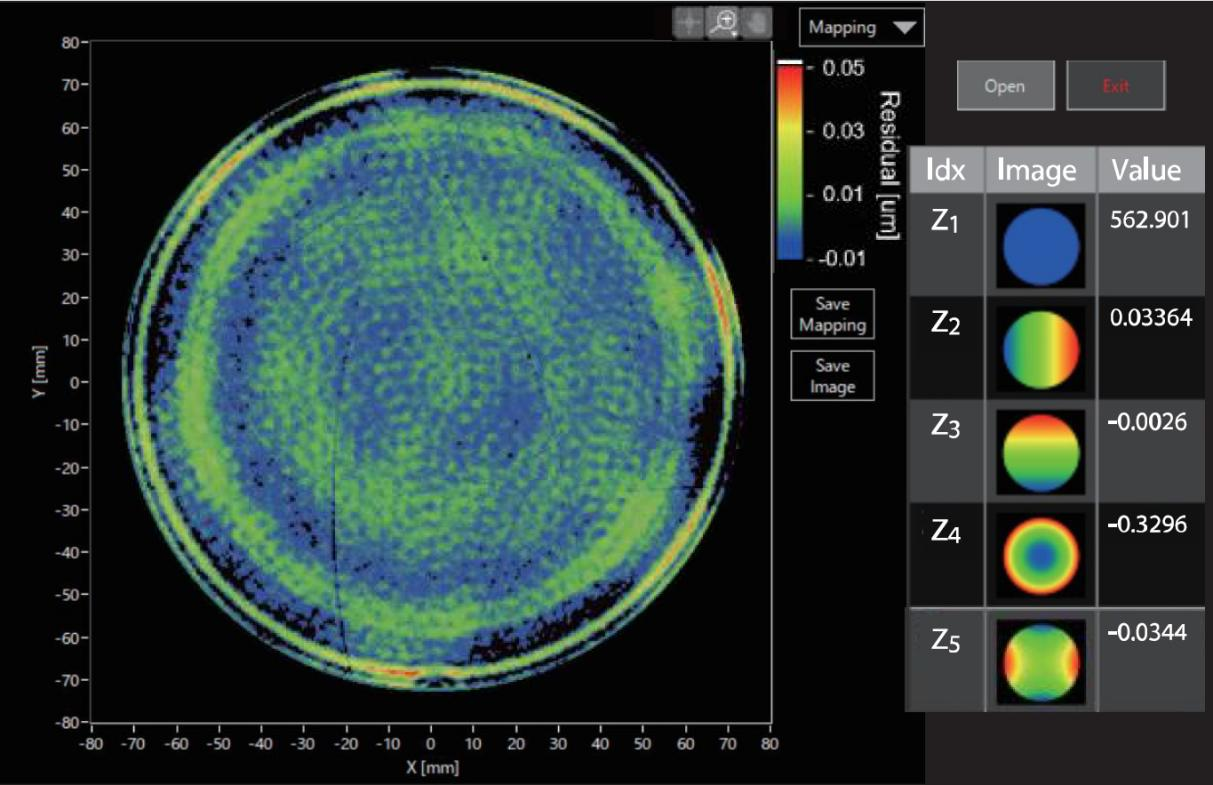

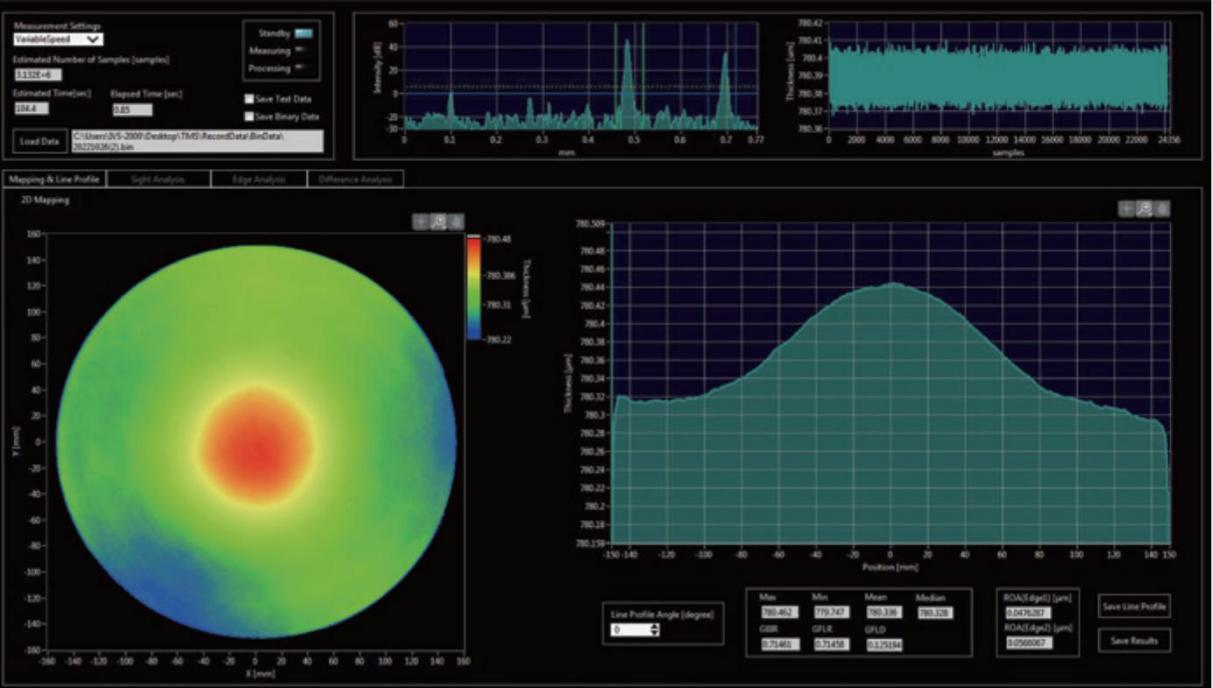

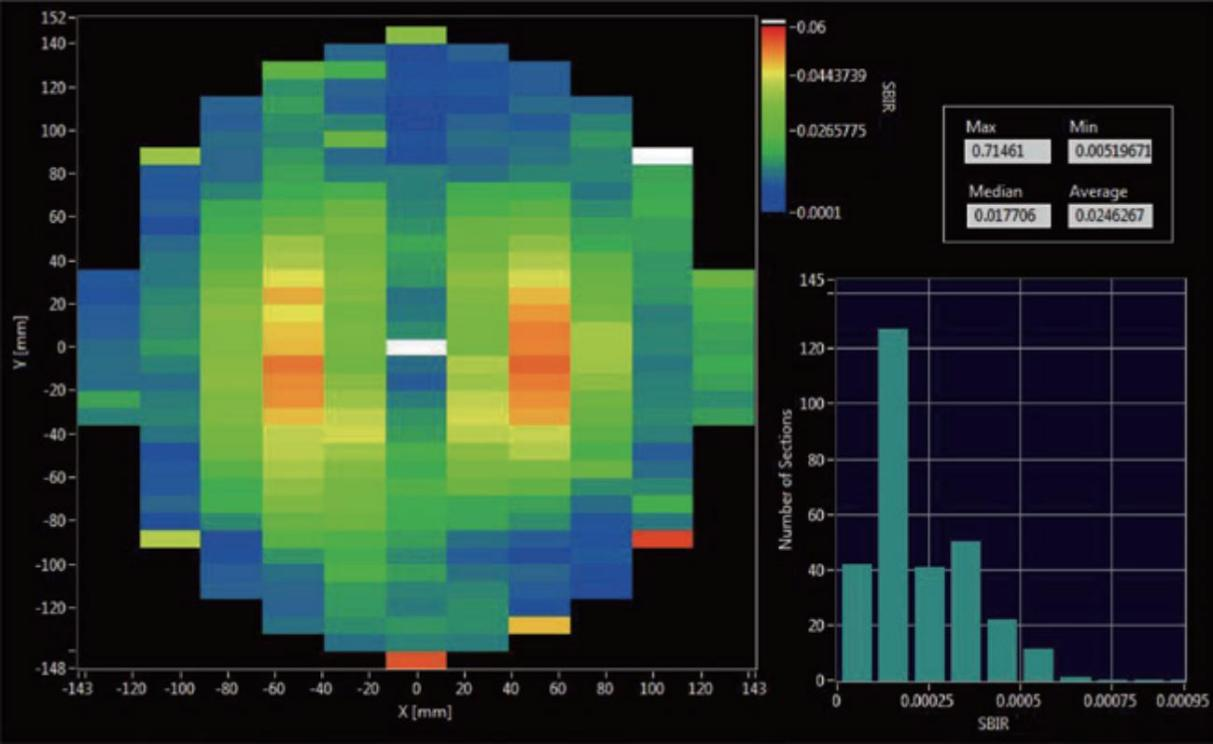

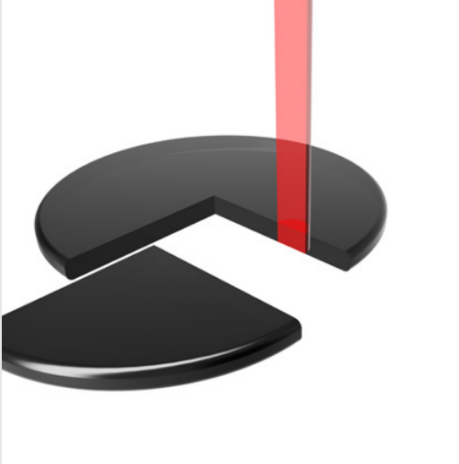

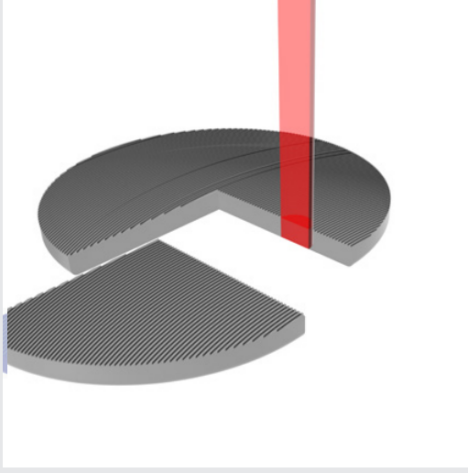

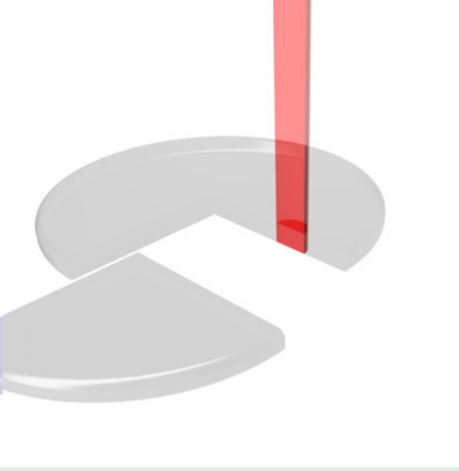

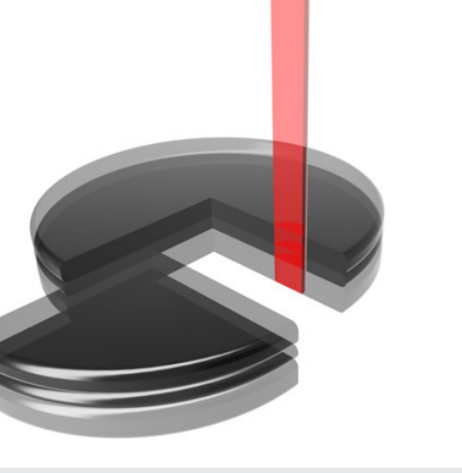

高通量晶圆测厚系统以光学相干层析成像原理,可解决晶圆/晶片厚度TTV(Total Thickness Variation,总厚度偏差)、BOW(弯曲度)、WARP(翘曲度),TIR(Total Indicated Reading 总指示读数,STIR(Site Total Indicated Reading 局部总指示读数),LTV(Local Thickness Variation 局部厚度偏差)等这类技术指标。

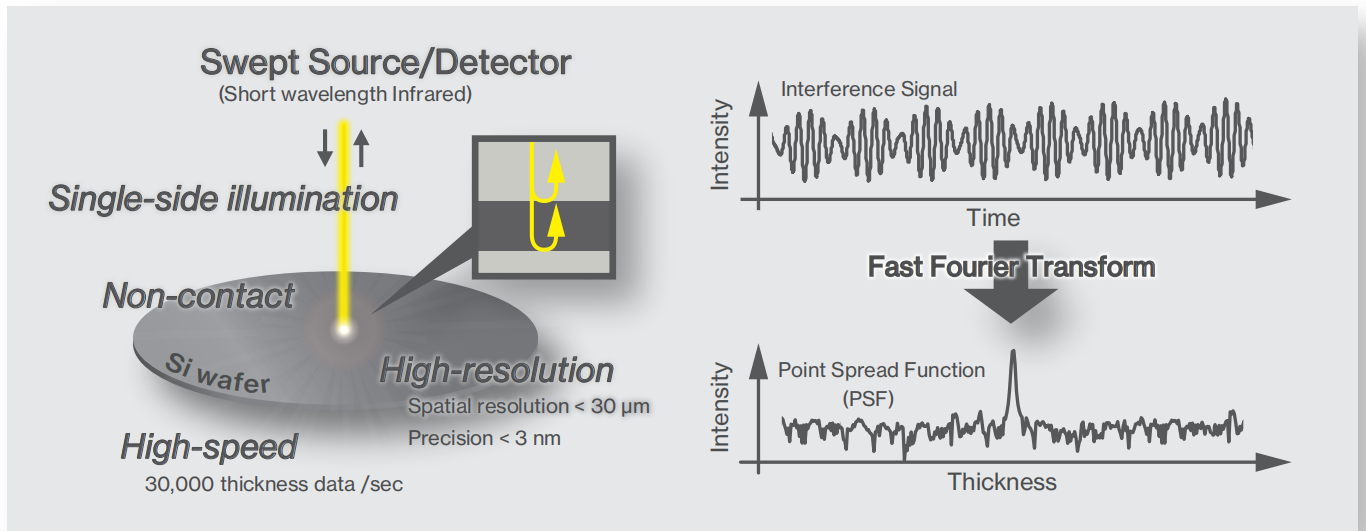

高通量晶圆测厚系统,全新采用的第三代可调谐扫频激光技术,相比传统上下双探头对射扫描方式;可一次性测量所有平面度及厚度参数。

1,灵活适用更复杂的材料,从轻掺到重掺 P 型硅 (P++),碳化硅,蓝宝石,玻璃,铌酸锂等晶圆材料。

重掺型硅(强吸收晶圆的前后表面探测)

粗糙的晶圆表面,(点扫描的第三代扫频激光,相比靠光谱探测方案,不易受到光谱中相邻单位的串扰噪声影响,因而对测量粗糙表面晶圆)

低反射的碳化硅(SiC)和铌酸锂(LiNbO3);(通过对偏振效应的补偿,加强对低反射晶圆表面测量的信噪比)

绝缘体上硅(SOI)和MEMS,可同时测量多 层 结 构,厚 度 可 从μm级到数百μm 级不等。

可用于测量各类薄膜厚度,厚度最薄可低至 4 μm ,精度可达1nm。

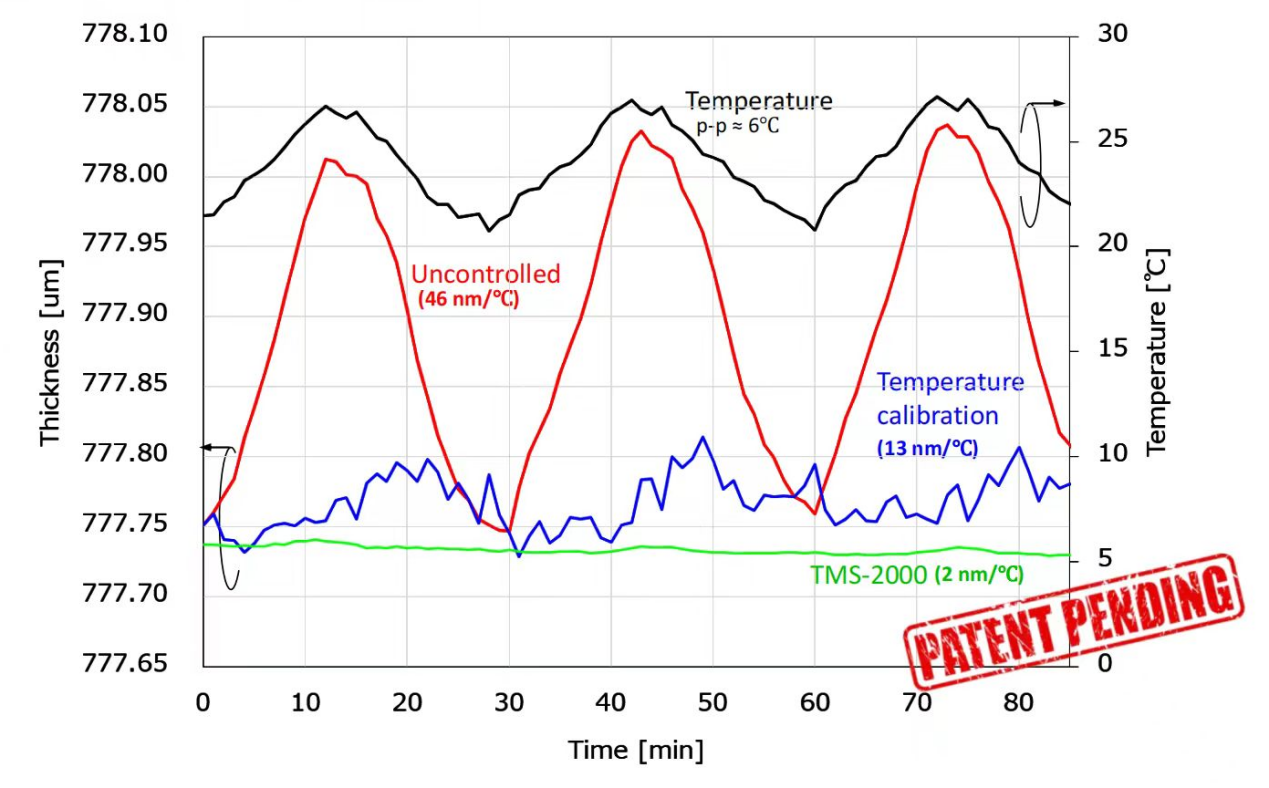

2,可调谐扫频激光的“温漂”处理能力,体现在极端工作环境中抗干扰能力强,充分提高重复性测量能力。

采用第三代高速扫频可调谐激光器,一改过去传统SLD宽频低相干光源的干涉模式,解决了由于相干长度短,而重度依赖“主动式减震平台”的情况。卓越的抗干扰,实现小型化设计,同时也可兼容匹配EFEM系统实现产线自动化集成测量。

3,灵活的运动控制方式,可兼容2英寸到12英寸方片和圆片测量。

-

晶圆

+关注

关注

52文章

4957浏览量

128185 -

测量

+关注

关注

10文章

4927浏览量

111647 -

碳化硅

+关注

关注

25文章

2798浏览量

49171

发布评论请先 登录

相关推荐

碳化硅衬底,进化到12英寸!

碳化硅压敏电阻 - 氧化锌 MOV

碳化硅深层的特性

碳化硅半导体器件有哪些?

请教碳化硅刻蚀工艺

碳化硅衬底市场群雄逐鹿 碳化硅衬底制备环节流程

简述碳化硅衬底类型及应用

碳化硅衬底的环吸方案相比其他吸附方案,对于测量碳化硅衬底 BOW/WARP 的影响

不同的碳化硅衬底的吸附方案,对测量碳化硅衬底 BOW/WARP 的影响

测量探头的 “温漂” 问题,都是怎么产生的,以及对于碳化硅衬底厚度测量的影响

测量探头的 “温漂” 问题,对于碳化硅衬底厚度测量的实际影响

测量探头的 “温漂” 问题,对于碳化硅衬底厚度测量的实际影响

评论