xilinx FPGA IOB约束使用以及注意事项

一、什么是IOB约束

在xilinx FPGA中,IOB是位于IO附近的寄存器,是FPGA上距离IO最近的寄存器,同时位置固定。当你输入或者输出采用了IOB约束,那么就可以保证从IO到达寄存器或者从寄存器到达IO之间的走线延迟最短,同时由于IO的位置是固定的,即存在于IO附近,所以每一次编译都不会造成输入或者输出的时序发生改变。

二、为什么要使用IOB约束

考虑一个场景,当你用FPGA写了一个spi模块,将时钟、片选和数据线绑定到FPGA的IO管脚,如果没有加IOB约束的话,综合工具在布局布线的时候直接将FPGA内部寄存器输出连到IO上,但是这样存在一定的问题,每次修改逻辑重新编译的时候,输出寄存器的位置有可能发生改变,那么从寄存器输出到IO之间的布线长度就会发生变化,造成寄存器输出到达IO之间的走线延迟发生改变,每一次编译都会使得spi的输出时序不确定。

为了解决这个问题,需要加入IOB约束,将模块输出端口的最后一级寄存器放在IOB上,这样最后一级输出的寄存器位置就固定下来了,每次编译都不会造成输出时序发生改变。

IOB约束使用方法如下:

1、在约束文件中加入下面约束:

set_property IOB true [get_ports {port_name}]

set_property IOB true [get_cells {cell_name}]

2、直接在代码中加约束,在寄存器前加入下面约束,需要注意的是,对于输入IOB约束,这里的寄存器是第一级寄存器,对于输出IOB约束,这里的寄存器是最后一级寄存器,且寄存器输出不能再作为组合逻辑输入。

(* IOB = "true" *) reg O_data;

三、IOB约束使用注意事项

对于输出IOB约束,在使用的时候有一些限制:

1、约束的端口必需是寄存器输出,这点比较好理解,因为IOB约束本质上是约束最后一级寄存器的位置,将最后一级寄存器的位置放在IOB上,而不是增加一级寄存器。所以你必须要是寄存器输出,才能进行IOB约束,这是前提。

2、最后一级寄存器的输出不能再作为输入反馈到内部逻辑中,必需是开路的。举个例子,比如如下代码:

always @ (posedge clk)

begin

if(cnt == 2'b1 || cnt == 2'b3)

spi_clk <= ~spi_clk;

else

spi_clk <= spi_clk;

end

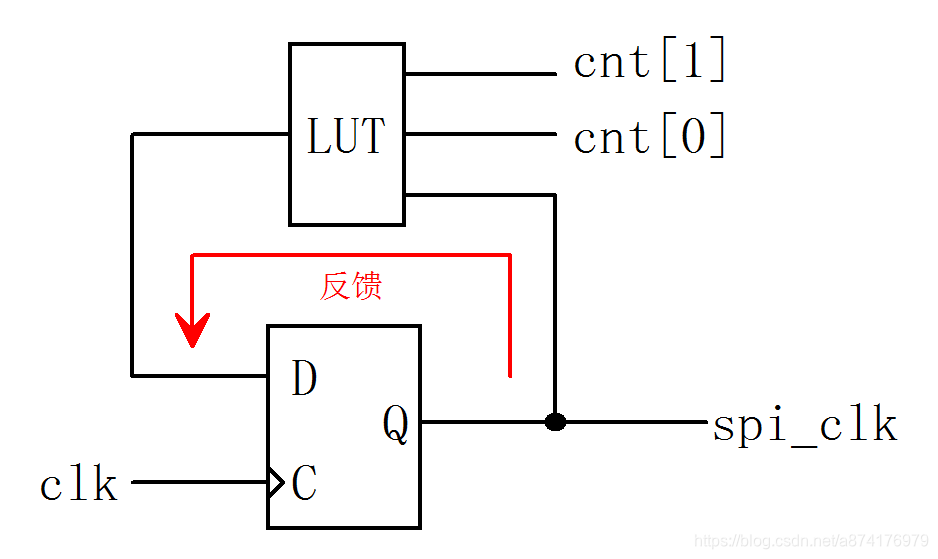

上面描述了一个分频器,当计数器cnt为1和3的时候spi_clk翻转,那这个时候spi_clk就是一个输出又作为输入反馈到内部的寄存器,得到的综合结果如下图:

由于需要将寄存器的输出作为输入其他逻辑的输入,这种情况下是无法将spi_clk寄存器放到IOB上的,因为IOB的输出直接对接IO,无法再作为输入反馈到内部逻辑。

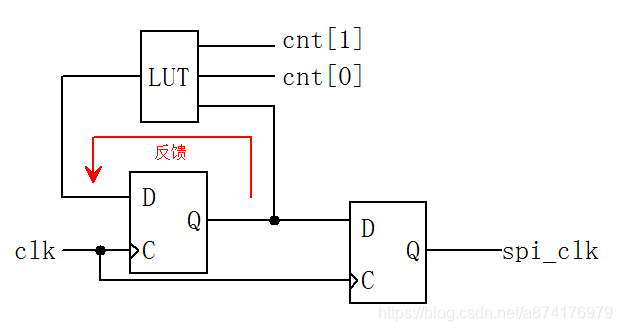

所以可以将spi_clk输出再加一级寄存器,将加入的寄存器放到IOB上,相应的需要对时序做出一定的调整,和sip_clk有时序关系的都需要打一拍以保持同步。

-

FPGA

+关注

关注

1630文章

21796浏览量

605393 -

Xilinx

+关注

关注

71文章

2171浏览量

121987

原文标题:xilinx FPGA IOB约束使用以及注意事项

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA的高速接口应用注意事项

FPGA设计的注意事项

xilinx FPGA的IOB使用教程说明

FPGA管脚调整的注意事项

Xilinx FPGA的约束设置基础

xilinx FPGA IOB约束使用以及注意事项

xilinx FPGA IOB约束使用以及注意事项

评论