本文主要介绍微型晶体管高分辨率X射线成像

一种经过升级的X射线可对芯片内部进行3D成像,展现其设计和缺陷。这种方法的分辨率为4纳米,提供的图像非常清晰,可以绘制芯片的布线路径,在不破坏芯片的前提下展现微小晶体管的特征。 研究人员使用混合光学成像技术和其他方法来缩小潜在的问题区域;然后, 研究人员用扫描电子显微镜对芯片的部分表面进行成像;最后对芯片切片,用透射电子显微镜(TEM)进一步成像。发现缺陷后,回头来修改其设计。

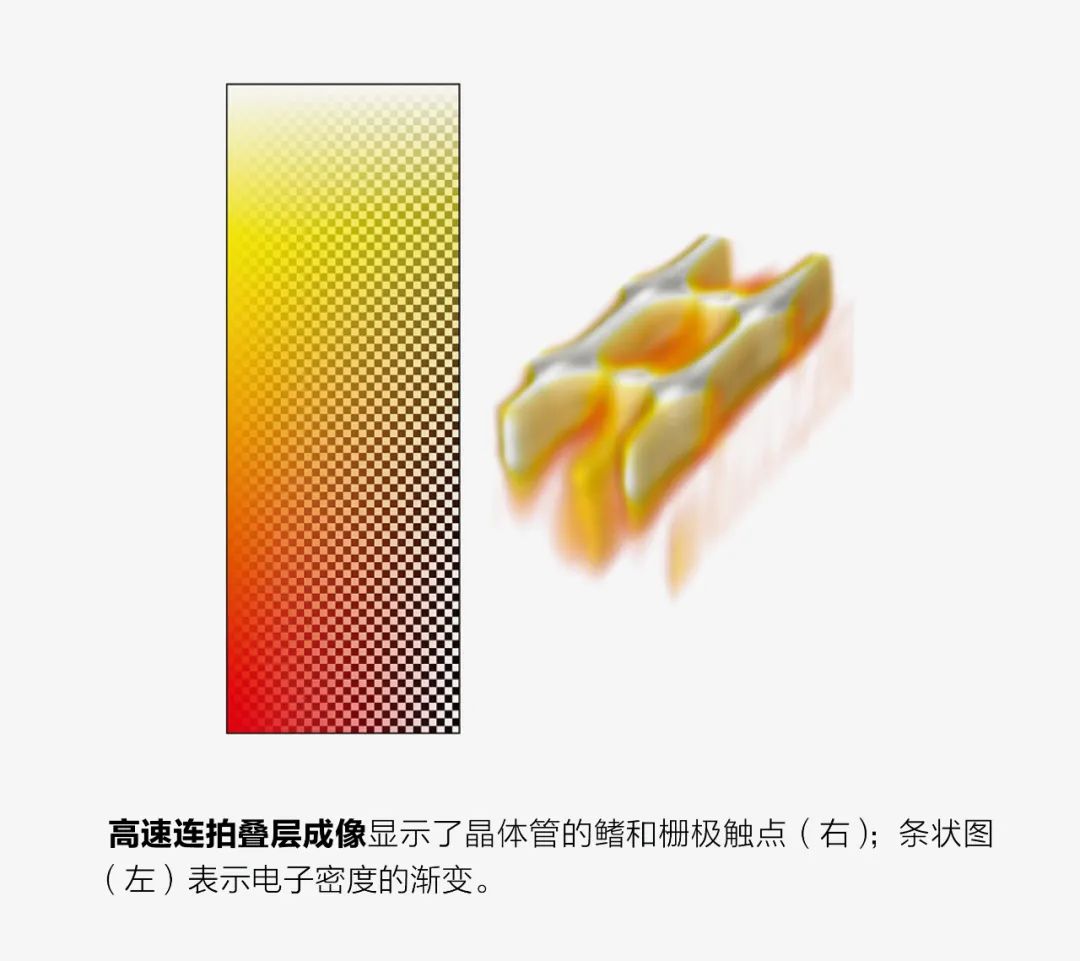

新的成像技术使用了一种名为“同步加速器”的粒子加速器产生的“硬”X射线,即高能X射线。无需切片,这些光束即可穿透芯片。这种方法名为“叠层成像术”,其工作原理是用高能射线的相干光束从不同角度反复照射样品。芯片上的微小特征会使光发生衍射。然后,根据衍射X射线的强度和相位,用算法重建最可能的图像样本。

这种成像技术的最初版本叠层X射线分层成像术可实现的分辨率大约为19纳米,虽然可识别芯片的互连,但图像过于粗糙,无法精确定位单个晶体管的特征。 一种解决方案称为高速连拍叠层成像术,即快速拍摄大量图像,然后用计算方法进行分类。

虽然这种叠层X射线计算机断层扫描(CT)技术的分辨率不到透射电子显微镜的1/4,但这种取舍是值得的,因为这项技术不需要切割,也不会破坏芯片,而且可以提供更深处的3D图像,工程师可以看到整个芯片5微米深度,而透射电子显微镜可见的深度为10到30纳米。研究人员表示,这种新方法可以让工程师更容易、更快速地发现芯片缺陷。制造结果的性能无法始终达到设计师的目标,而成像可以帮助工程师将设计和现实更紧密地联系在一起。 随着晶体管和芯片具备更多的3D特征,获得更高分辨率的3D视图越来越重要了。晶体管变得越来越小,不再是平面结构,无论是鳍式场效应晶体管还是即将实现的栅极全包围晶体管,它们都是从表面凸出来的,或者是分层的。诸多半导体制造商计划在未来的几代产品中,将芯片的电源互连从芯片的正面移到背面,这额外增加了其复杂性。

-

晶体管

+关注

关注

77文章

9829浏览量

139396 -

X射线成像

+关注

关注

0文章

4浏览量

6766

原文标题:微型晶体管高分辨率X射线成像

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

高分辨率示波器的功能与作用:以麦科信MHO6为例

高速、高分辨率、大面积成像应用的理想选择——Falcon4-CLHS工业相机

诺丁汉特伦特大学研发全红外波段高分辨率成像技术

24位或者说高分辨率的AD到底有什么用呢?

如何提高透镜成像的分辨率

使用DM642 DSP和THS8200驱动器的高分辨率视频

鼎阳科技|高分辨率产品增长39.42%,引领高端市场新浪潮!

什么是高分辨率示波器?它有哪些优势?

Moritex 5X 高分辨率远心镜头 助力晶圆检测

高管洞察:高分辨率音乐需要高分辨率扬声器

高分辨率音频和普通音频之间的区别

微型晶体管高分辨率X射线成像

微型晶体管高分辨率X射线成像

评论