文章来源:半导体与物理

原文作者:jjfly686

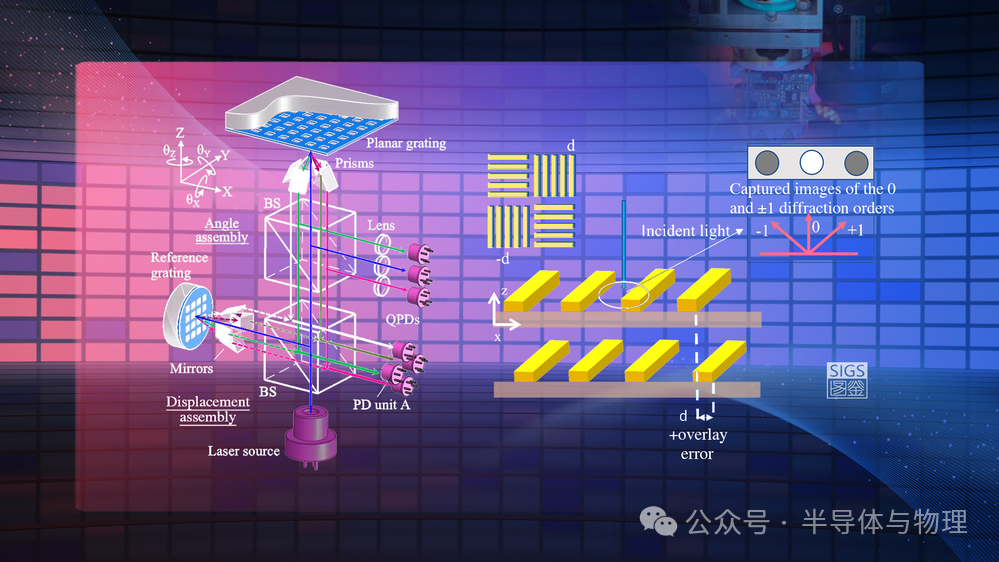

在芯片制造的复杂流程中,光刻工艺是决定晶体管图案能否精确“印刷”到硅片上的核心环节。而光刻Overlay(套刻精度),则是衡量光刻机将不同层电路图案对准精度的关键指标。简单来说,它就像建造摩天大楼时每一层的钢筋骨架能否完美对齐——任何微小的错位都可能导致整栋建筑的崩塌。在芯片领域,Overlay的误差会直接影响芯片的良率和性能,甚至决定先进制程的成败。

什么是光刻Overlay

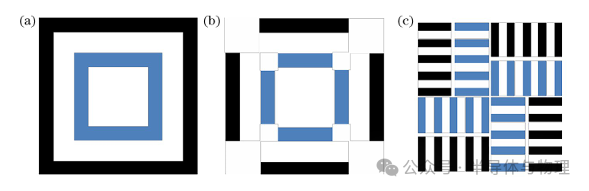

光刻Overlay指的是芯片制造过程中,前后两次光刻工艺形成的电路图案之间的对准精度。一颗现代芯片可能包含数十层电路结构(如晶体管层、金属互联层、绝缘层等),每一层都需要通过光刻机将设计图案投射到硅片上。如果相邻层的图案无法精准对齐(例如金属导线未能连接到晶体管触点),就会导致芯片功能失效。

Overlay误差的量化通常以纳米(nm)为单位。例如,在7nm先进制程中,Overlay误差需要控制在2nm以内。

Overlay误差影响芯片制造

1. 良率杀手:电路短路与断路

Overlay误差过大会直接导致不同层电路错位。例如,金属连线层若未能对准晶体管触点,可能引发断路;而相邻导线若重叠过多,则可能造成短路。据统计,Overlay问题可占高端芯片良率损失的30%以上。

2. 性能波动:晶体管参数失控

在FinFET或GAA(环绕栅极)晶体管中,栅极长度、沟道位置等关键参数对Overlay极其敏感。即使几纳米的偏差,也可能导致阈值电压漂移、漏电流增加,进而影响芯片功耗和频率。

3. 多层堆叠技术的瓶颈

3D NAND闪存、DRAM堆叠芯片等新型结构需要数十层材料的精确对准。Overlay误差会引发层间应力不均、信号传输失真等问题,严重时甚至导致结构开裂。

如何提升光刻Overlay精度

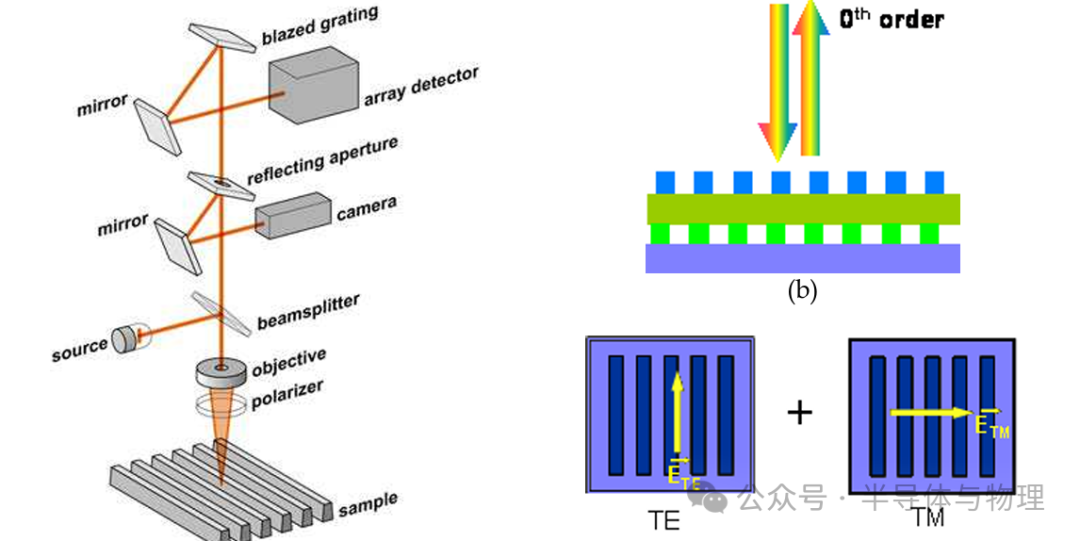

1. 光刻机硬件的极致优化

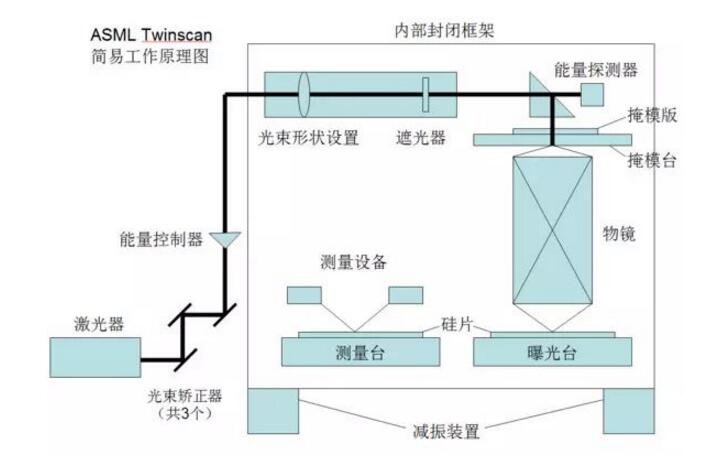

双工件台系统:ASML的TWINSCAN技术通过“曝光-测量”双台并行,将对准速度提升数倍。

高数值孔径(NA)物镜:EUV光刻机通过增大物镜数值孔径,提升分辨率和套刻精度。

激光干涉仪与形变补偿:实时监测硅片形变并通过机械臂微调,抵消热膨胀或机械应力导致的位移。

2. 材料与工艺的协同创新

智能光刻胶:开发具有自对准特性的化学放大胶(CAR),利用分子间作用力修正微小偏差。

平坦化工艺(CMP):通过化学机械抛光减少硅片表面起伏,避免高低差导致的聚焦误差。

应力匹配材料:在多层堆叠中使用热膨胀系数相近的材料,降低温度变化引起的层间错位。

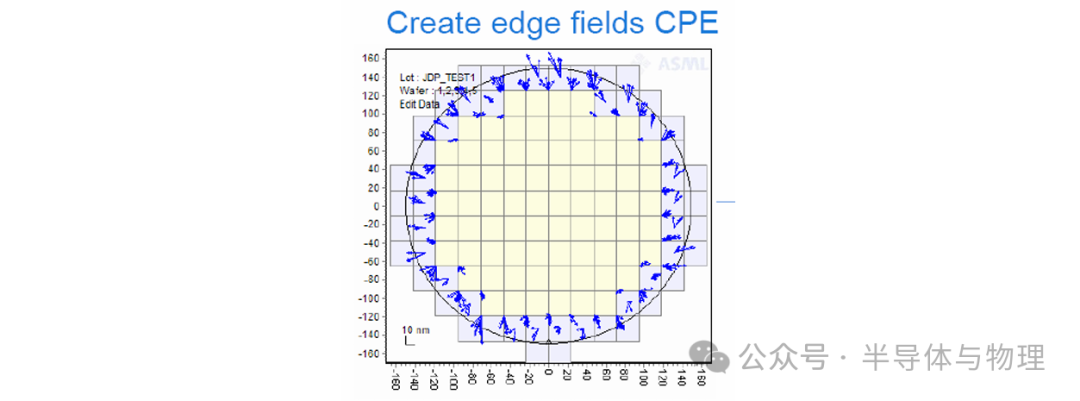

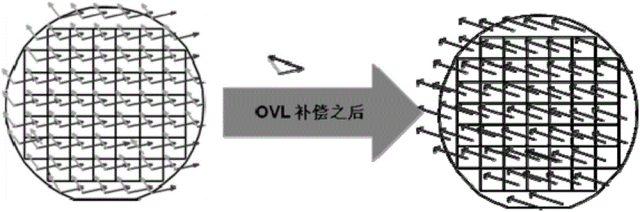

3. 算法与数据的闭环控制

实时反馈系统:每片晶圆曝光后立即测量Overlay数据并反馈调整。

机器学习预测模型:利用历史数据训练AI,预判设备状态变化(如镜头热漂移)并提前补偿。

虚拟量测(VM):结合工艺参数模拟Overlay结果,减少物理测量时间。

4. 多重曝光与工艺协同

自对准双重成像(SADP/SAQP):通过多次曝光和刻蚀组合,分解复杂图形并提升对准容差。

设计-工艺协同优化(DTCO):在芯片设计阶段预留Overlay补偿空间,例如采用冗余触点或弹性布线。

-

晶体管

+关注

关注

78文章

10443浏览量

148705 -

芯片制造

+关注

关注

11文章

736浏览量

30539 -

光刻工艺

+关注

关注

1文章

38浏览量

2129

原文标题:光刻工艺中的Overlay

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

什么是光刻机的套刻精度

什么是光刻机的套刻精度

评论