AS配置方式由FPGA器件引导配置操作过程,它控制着外部存储器及其初始化过程,EPCS系列配置芯片如EPCS1、EPCS4配置器件专供AS模式。使用Altera串行配置器件来完成,FPGA器件处于主动地位,配置器件处于从属地位。配置数据通过DATA0引脚送入 FPGA。配置数据被同步在DCLK输入上,1个时钟周期传送1位数据。

PS配置方式则由外部计算机或其它控制器控制配置过程。通过加强型配置器件(EPC16,EPC8,EPC4)等配置器件来完成,在PS配置期间,配置数据从外部储存部件,通过DATA0引脚送入FPGA。配置数据在DCLK上升沿锁存,1个时钟周期传送1位数据。

JTAG接口是一个业界标准,主要用于芯片测试等功能,使用IEEE Std 1149.1联合边界扫描接口引脚,支持JAM STAPL标准,可以使用Altera下载电缆或主控器来完成。

FPGA在正常工作时,它的配置数据存储在SRAM中,加电时须重新下载。在实验系统中,通常用计算机或控制器进行调试,因此可以使用PS。在实用系统中,多数情况下必须由FPGA主动引导配置操作过程,这时FPGA将主动从外围专用存储芯片中获得配置数据,而此芯片中FPGA配置信息是用普通编程器将设计所得的pof格式的文件烧录进去。

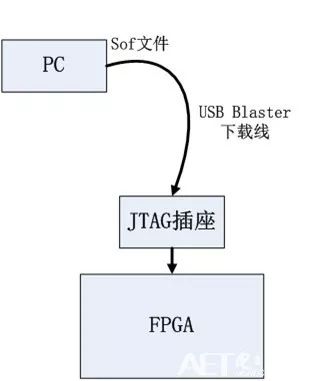

JTAG模式在线下载FPGA的原理如图7.15所示,PC端的Quartus II软件通过下载线缆将bit流(sof文件)下载到FPGA内部,下载完成后FPGA中立刻执行下载代码,速度很快,非常适合调试。

图7.15 基于JTAG的在线配置原理

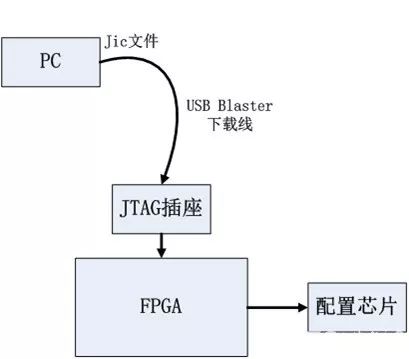

FPGA下载数据到配置芯片的原理如图7.16所示,PC端的Quartus II软件通过下载线缆将bit流(jic文件)下载到配置芯片中。由于配置芯片和JTAG接口都是分别连接到FPGA的,他们不是直接连接,所以配置文件从PC先是传送到FPGA,然后FPGA内部再转送给配置芯片,这个过程FPGA相当于起到一个桥接的作用。

图7.16 基于FPGA的配置芯片固化原理

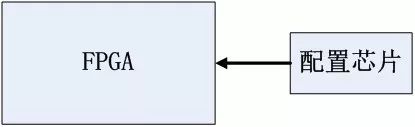

看完JTAG模式下在线配置FPGA和烧录配置芯片的原理,我们再了解一下FPGA上电初始的配置过程。FPGA上电后,内部的控制器首先工作,确认当前的配置模式,如果是外部配置芯片启动,则通过和外部配置芯片的接口(如我们的SPI接口)将配置芯片的数据加载到FPGA的RAM中,配置完成后开始正式运行,请数据流加载方向如图7.17所示。当然了,有人可能在想,JTAG在线配置是否和配置芯片加载相冲突呢?非也,JTAG在线配置的优先级是最高的,无论此时FPGA中在运行什么逻辑,只要JTAG下载启动,则FPGA便停下当前的工作,开始运行JTAG下载的新的配置数据。

图7.17 FPGA离线加载原理

-

FPGA

+关注

关注

1631文章

21806浏览量

606712 -

JTAG

+关注

关注

6文章

401浏览量

71905

原文标题:【博文精选】Altera FPGA配置方式之AS/PS/JTAG配置方式

文章出处:【微信号:ChinaAET,微信公众号:电子技术应用ChinaAET】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

EE-227:ADSP-21992 DSP的CAN配置过程

请问lmk04828-EP设置DCLKx的模拟延迟失败,导致时钟不稳定的原因?怎么解决?

通过DSP6455的MCBSP配置TLV320AIC20,如果想使用LINEI和LINEO,还需要哪些别的配置吗?

固化FPGA配置芯片的方式

树莓派4B的WiFi配置过程

工控机bios如何修改引导方式

FPGA的配置模式有哪些?具体配置过程是怎样的?

FPGA开发过程中配置全局时钟需要注意哪些问题

SD卡镜像启动过程中如何第一时间获取FPGA配置状态?

AMD Xilinx 7系列FPGA的Multiboot多bit配置

AS配置方式由FPGA器件引导配置操作过程

AS配置方式由FPGA器件引导配置操作过程

评论